频率检测电路和电子设备的制作方法

本技术涉及电路,特别是涉及频率检测电路和电子设备。

背景技术:

1、在电子设备中常常会用到时钟信号,时钟信号通常被用于同步电路当中,扮演计时器的角色,保证相关的电子组件得以同步运作。在一些应用场景中,会需要对时钟信号进行频率检测,一般若需要精确检测时钟信号的具体频率值,需要设计较为复杂的电路。

2、但是在另一些应用场景中,往往不需要检测到具体的频率值,而是能够检测时钟信号的频率的变化即可,需要实时检测时钟信号的变化,以确定时钟信号所在的范围。

技术实现思路

1、本技术提供了频率检测电路和电子设备,能够对时钟信号进行频率检测。

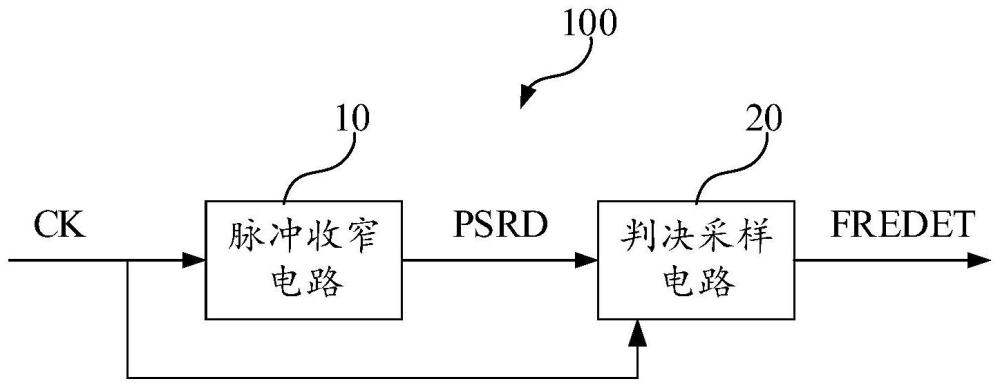

2、为解决上述技术问题,本技术采用的一个技术方案是:提供一种频率检测电路,包括:脉冲收窄电路,接收待检测时钟信号,对待检测时钟信号执行至少一级脉冲收窄操作,脉冲收窄电路具有至少一检测点频率,脉冲收窄电路基于检测点频率对待检测时钟信号进行收窄,以得到收窄输出时钟信号;判决采样电路,耦接脉冲收窄电路,基于待检测时钟信号作为采样时钟,对收窄输出时钟信号进行采样,以得到频率标志信号,其中,频率标志信号表征待检测时钟信号是否大于检测点频率。

3、其中,每级脉冲收窄操作对输入时钟信号进行第一反相,并在第一反相过程中,控制电平转换上升沿的爬升速度或电平转换下降沿的下降速度,得到第一反相时钟信号,并对第一反相时钟信号进行第二反相,以得到收窄输出时钟信号。

4、其中,响应于频率标志信号全部为第一逻辑信号,确定待检测时钟信号的频率高于检测点频率;或者,响应于频率标志信号全部为第二逻辑信号,确定待检测时钟信号的频率低于检测点频率。

5、其中,脉冲收窄电路包括m个脉冲收窄单元,每个脉冲收窄单元耦接上一级脉冲收窄单元,以上一级收窄输出时钟信号作为本级输入时钟信号,执行一级脉冲收窄操作,从而得到本级收窄输出时钟信号,其中,m为大于1的自然数。

6、其中,脉冲收窄电路提供n个检测点频率以获得n个收窄输出时钟信号,其中,任一脉冲收窄单元与下一级脉冲收窄单元之间的耦接点,和/或最后一级脉冲收窄单元的输出端,可作为脉冲收窄电路的一个输出端,以输出一路收窄输出时钟信号,对应的检测点频率由脉冲收窄电路的对应输出端之前的脉冲收窄单元确定;判决采样电路包括n个判决采样单元,其中,每个判决采样单元耦接脉冲收窄电路的一个输出端,以接收一路对应的收窄输出时钟信号,并接收待检测时钟信号,从而得到一路对应的频率标志信号,n个频率标志信号表征待检测时钟信号的频率大小范围,其中,n为小于等于m的自然数。

7、其中,每个脉冲收窄单元包括:第一反相电路,其中,第一反相电路为延迟反相电路,对接收的输入时钟信号进行第一反相,并在第一反相过程中,通过限流元件控制电平转换上升沿的爬升速度或电平转换下降沿的下降速度,得到第一反相时钟信号;第二反相电路,其中,第二反相电路为阈值反相电路,对第一反相时钟信号进行第二反相,得到收窄输出时钟信号。

8、其中,响应于对电平转换上升沿的爬升速度进行控制,第一反相电路包括:第一开关管,第一开关管的第一端用于接收工作电压;第二开关管,第二开关管的第一端耦接第一开关管的第二端;第三开关管,第三开关管的第一端耦接第二开关管的第二端,第三开关管的第二端接地;电容,电容的第一端耦接第三开关管的第一端,电容的第二端接地;其中,第一开关管、第二开关管和第三开关管的控制端接收待检测时钟信号;在待检测时钟信号为逻辑高电平时,控制第三开关管导通,对电容进行放电,在待检测时钟信号为逻辑低电平时,控制第一开关管和第二开关管导通,对电容进行充电,以第二开关管作为限流元件控制电平转换上升沿的爬升速度,得到第一反相时钟信号;

9、或者,第一反相电路包括:第一开关管,第一开关管的第一端用于接收工作电压;电阻,电阻的第一端耦接第一开关管的第二端;第二开关管,第二开关管的第一端耦接电阻的第二端,第二开关管的第二端接地;电容,电容的第一端耦接第二开关管的第一端,电容的第二端接地;其中,第一开关管和第二开关管的控制端接收待检测时钟信号;在待检测时钟信号为逻辑高电平时,控制第二开关管导通,对电容进行放电,在待检测时钟信号为逻辑低电平时,控制第一开关管导通,对电容进行充电,以电阻作为限流元件控制电平转换上升沿的爬升速度,得到第一反相时钟信号;

10、或者,第一反相电路包括:电流源;第一开关管,第一开关管的第一端耦接电流源;第二开关管,第二开关管的第一端耦接第一开关管的第二端,第二开关管的第二端接地;电容,电容的第一端耦接第二开关管的第一端,电容的第二端接地;其中,第一开关管和第二开关管的控制端接收待检测时钟信号;在待检测时钟信号为逻辑高电平时,控制第二开关管导通,对电容进行放电,在待检测时钟信号为逻辑低电平时,控制第一开关管导通,对电容进行充电,以电流源作为限流元件控制电平转换上升沿的爬升速度,得到第一反相时钟信号。

11、其中,响应于对电平转换下降沿的下降速度进行控制,第一反相电路包括:第一开关管,第一开关管的第一端接收工作电压;第二开关管,第二开关管的第一端耦接第一开关管的第二端;第三开关管,第三开关管的第一端耦接第二开关管的第二端,第三开关管的第二端接地;电容,电容的第一端耦接第二开关管的第一端,电容的第二端接地;其中,第一开关管、第二开关管和第三开关管的控制端接收待检测时钟信号;在待检测时钟信号为逻辑低电平时,控制第一开关管导通,对电容进行充电,在待检测时钟信号为逻辑高电平时,控制第二开关管和第三开关管导通,对电容进行放电,以第二开关管作为限流元件控制电平转换下降沿的下降速度,得到第一反相时钟信号;

12、或者,第一反相电路包括:第一开关管,第一开关管的第一端用于接收工作电压;电阻,电阻的第一端耦接第一开关管的第二端;第二开关管,第二开关管的第一端耦接电阻的第二端,第二开关管的第二端接地;电容,电容的第一端耦接电阻的第一端,电容的第二端接地;其中,第一开关管和第二开关管的控制端用于接收待检测时钟信号;在待检测时钟信号为逻辑低电平时,控制第一开关管导通,对电容进行充电,在待检测时钟信号为逻辑高电平时,控制第二开关管导通,对电容进行放电,以电阻作为限流元件控制电平转换下降沿的下降速度,得到第一反相时钟信号;

13、或者,第一反相电路包括:第一开关管,第一开关管的第一端接收工作电压;第二开关管,第二开关管的第一端耦接第一开关管的第二端;电容,电容的第一端耦接第二开关管的第一端;电流源,电流源的第一端耦接电容的第二端,电流源的第二端接地;其中,第一开关管和第二开关管的控制端用于接收待检测时钟信号;在待检测时钟信号为逻辑低电平时,控制第一开关管导通,对电容进行充电,在待检测时钟信号为逻辑高电平时,控制第二开关管导通,对电容进行放电,以电流源作为限流元件控制电平转换下降沿的下降速度,得到第一反相时钟信号。

14、其中,频率检测电路还包括:分频电路,接收待检测时钟信号,对待检测时钟信号进行分频,输出分频时钟信号;脉冲收窄电路耦接分频电路的输出端,对分频时钟信号执行至少一级脉冲收窄操作,得到收窄输出时钟信号。

15、其中,频率检测电路还包括:延时电路,接收待检测时钟信号,对待检测时钟信号进行延时,输出延时后的待检测时钟信号;脉冲收窄电路耦接延时电路的输出端,对延时后的待检测时钟信号执行至少一级脉冲收窄操作,得到收窄输出时钟信号。

16、为解决上述技术问题,本技术采用的一个技术方案是:提供一种电子设备,该电子设备包括如上述技术方案提供的频率检测电路。

17、其中,更包括:dll电路,耦接频率检测电路,dll电路以待检测时钟信号作为输入时钟,并根据频率标志信号调整其电路参数。

18、其中,电路参数包括采样频率,其中当待检测时钟信号低于检测点频率时,dll电路调低采样频率。

19、其中,电路参数包括延迟线延时,其中当待检测时钟信号低于检测点频率时,dll电路调长延迟线延时。

20、本技术的有益效果是:区别于现有技术的情况,本技术提供的频率检测电路包括:脉冲收窄电路和判决采样电路。通过脉冲收窄电路基于检测点频率对待检测时钟信号进行收窄,以得到收窄输出时钟信号,以及利用判决采样电路基于待检测时钟信号作为采样时钟,对收窄输出时钟信号进行采样,以得到频率标志信号,利用频率标志信号表征待检测时钟信号与预设的检测点频率的大小关系,以此实现对待检测时钟信号的频率检测。进一步,在一些不需要获取时钟信号精确频率而只需要判断频率高低的场景中,通过频率标志信号(表征与检测点频率的大小关系)能直观的反应待检测时钟信号所处的频率范围。

- 还没有人留言评论。精彩留言会获得点赞!