一种超短波测向装置的制作方法

1.本实用新型涉及测向设备技术领域,尤其涉及一种超短波测向装置。

背景技术:

2.测向装置是用来测出无线电台发射出来的电波及其传播方向,以确定发射机位置的装置,但是现有的测向装置整个设备的集成度相对较低,体积大、功耗大,成本也相对高。

技术实现要素:

3.本实用新型的目的在于克服现有技术的缺点,提供一种超短波测向装置,解决了现有技术存在的问题。

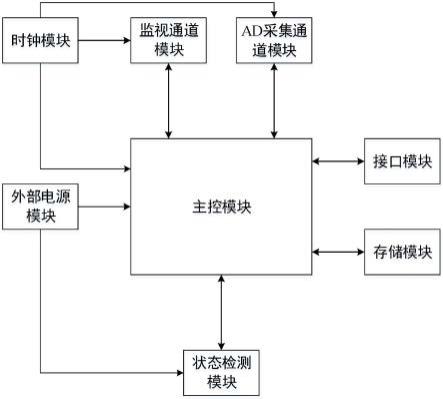

4.本实用新型的目的通过以下技术方案来实现:一种超短波测向装置,它包括主控模块、ad采集通道模块、监视通道模块、时钟模块、外部电源模块、接口模块和存储模块;所述主控模块与监视通道模块、ad采集通道模块、接口模块和存储模块相互连接;所述时钟模块的输出端与所述监视通道模块、ad采集通道模块和主控单元的时钟信号输入端连接;所述外部电源模块的供电输出端与所述主控模块的输入端连接。

5.所述时钟模块包括模拟时钟单元和数字时钟单元;所述模拟时钟单元和数字时钟单元的输出端与所述监视通道模块、ad采集通道模块和主控模块的时钟信号输入端连接。

6.所述模拟时钟单元包括时钟芯片ad9528,时钟芯片ad9528的输出端与所述监视通道模块、ad采集通道模块和主控模块的时钟信号输入端连接。

7.所述数字时钟单元包括时钟合成器和三个时钟缓冲器,时钟合成器的输出端输出33.333mhz时钟信号到所述主控模块,输出100mhz、156.25mhz和125mhz时钟信号到三个时钟缓冲器,每个时钟缓冲器接收一种频率的时钟信号并分层多路输出到所述ad采集通道模块。

8.所述ad采集通道模块包括四个ad采集芯片,每个ad采集芯片包括两路采集通道,每个ad采集芯片与主控模块相互连接;所述模拟时钟单元和数字时钟单元的时钟信号输出端与ad采集芯片的时钟信号输入端连接。

9.所述外部电源模块包括12v电源、第一降压单元、第二降压单元和第三降压单元;12v电源的输出端分别与第一降压单元、第二降压单元和第三降压单元的输入端连接;第一降压单元将12v电压降压为1.2v、1.5v和1.8v电压输入到主控模块;第二降压单元将12v电源降压为2.5v电源输入到主控模块;第三降压单元将12v电源降压为3.3v电压输入到主控模块。

10.所述主控模块包括fpga单元和dsp单元;fpga单元与dsp单元相互连接,ad采集通道模块和监视通道模块与所述fpga单元相互连接,所述时钟模块的时钟输出端与fpga单元的时钟信号输入端连接,所述存储模块和接口模块与fpga单元和dsp单元相互连接,所述外部电源模块的供电输出端与fpga单元和dsp单元的供电输入端连接。

11.还包括状态检测模块,状态检测模块包括温度监测单元和电压电流检测单元,所

述温度监测单元和电压电流检测单元与所述fpga单元连接。

12.本实用新型具有以下优点:一种超短波测向装置,具有8通道超短波信号同步采集、处理能力以及1通道超短波信号监视,具备通过ddr芯片对高速采集数据进行独立缓存的功能,能够将高速采集数据通过ddr芯片缓存后再通过srio接口向后级传输,支持千兆网口数据传输,能够实现设备上主要器件温度、电压等自检信息进行上传。

附图说明

13.图1为本实用新型的电路原理示意图;

14.图2为数字时钟单元的电路示意图;

15.图3为外部电源模块的电路示意图。

具体实施方式

16.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本技术实施例的组件可以以各种不同的配置来布置和设计。因此,以下结合附图中提供的本技术的实施例的详细描述并非旨在限制要求保护的本技术的保护范围,而是仅仅表示本技术的选定实施例。基于本技术的实施例,本领域技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本技术保护的范围。下面结合附图对本实用新型做进一步的描述。

17.如图1所示,一种超短波测向装置,它包括主控模块、ad采集通道模块、监视通道模块、时钟模块、外部电源模块、接口模块和存储模块;所述主控模块与监视通道模块、ad采集通道模块、接口模块和存储模块相互连接;所述时钟模块的输出端与所述监视通道模块、ad采集通道模块和主控单元的时钟信号输入端连接;所述外部电源模块的供电输出端与所述主控模块的输入端连接。

18.所述主控模块包括fpga单元和dsp单元;fpga单元与dsp单元相互连接,ad采集通道模块和监视通道模块与所述fpga单元相互连接,所述时钟模块的时钟输出端与fpga单元的时钟信号输入端连接,所述存储模块和接口模块与fpga单元和dsp单元相互连接,所述外部电源模块的供电输出端与fpga单元和dsp单元的供电输入端连接。

19.进一步地,fpga单元的型号为xczu15eg,dsp单元的型号为tms320c6678,在xczu15eg的ps端连接的接口模块包括以太网接口、qspi和uart接口,存储模块包括ddr、flash和sd/e.mmc,在dsp上也连接有flash、ddr以及eeprom存储器。

20.ps端的以太网控制器支持gmii、rgmii和sgmii模式,本实用新型使用rgmii模式,外部挂接千兆以太网phy(dp83867),通过外部晶体产生phy芯片工作时钟。其供电电压为1.8v和1.0v。io电压为1.8v,可以直接与soc的ps端口接口,不需要增加额外的隔离芯片。以太网phy对外引出标准rj45网口。

21.所述时钟模块包括模拟时钟单元和数字时钟单元;所述模拟时钟单元和数字时钟单元的输出端与所述监视通道模块、ad采集通道模块和主控模块的时钟信号输入端连接。

22.所述模拟时钟单元包括时钟芯片ad9528,时钟芯片ad9528的输出端与所述监视通

道模块、ad采集通道模块和主控模块的时钟信号输入端连接。

23.进一步地,ad9528是一款双级pll,集成jesd204b sysref发生器,可用于多器件同步。第一级锁相环(pll)(pll1)通过减少系统时钟的抖动,从而实现输入基准电压调理。第二级pll(pll2)提供高频时钟,可实现来自时钟输出驱动器的较低积分抖动以及较低宽带噪声。外部vcxo提供pll2所需的低噪声基准电压,以满足苛刻的相位噪声和抖动要求,实现可以接受的性能。片内vco的调谐频率范围为3.450ghz至4.025ghz。集成的sysref发生器输出单次、n次或连续信号,并与pll1和pll2输出同步,以便对齐多个器件的时间;ad9528产生最高频率为1.25ghz的六路输出(输出0至输出3、输出12和输出13),以及最大频率高达1ghz的八路输出。每一路输出均可配置为直接从pll1、pll2或内部sysref发生器输出。14路输出通道的每一路都包含一个带数字相位粗调功能的分频器,以及一个模拟微调相位延迟模块,允许全部14路输出具有时序对齐的高度灵活性。ad9528还可用作灵活的双通道输入缓冲器,以便实现14路器件时钟和/或sysref信号的分配。启动时,ad9528直接向输出12和输出13发送vcxo信号,用作启动就绪时钟。

24.如图2所示,数字时钟单元包括时钟合成器和三个时钟缓冲器,时钟合成器的输出端输出33.333mhz时钟信号到所述主控模块,输出100mhz、156.25mhz和125mhz时钟信号到三个时钟缓冲器,每个时钟缓冲器接收一种频率的时钟信号并分层多路输出到所述ad采集通道模块。

25.其中,采用一片idt公司的843n571输出多个种类的时钟,其中100mhz,125mhz和156.25mhz各采用一片cdclvc1208进行fanout,分别输出8组100mhz,125mhz和15625mhz lvds时钟843n571直接倍频输出的33mhz时钟则直接连到fpga的ps端参考时钟中。

26.所述ad采集通道模块包括四个ad采集芯片,每个ad采集芯片包括两路采集通道,每个ad采集芯片与主控模块相互连接;所述模拟时钟单元和数字时钟单元的时钟信号输出端与ad采集芯片的时钟信号输入端连接。

27.进一步地,ad采集芯片的型号为adrv9009,总共8路采集通道,每个通道频率范围为75mhz~6ghz,瞬时带宽最大200mhz,每个adrv9009将jesd高速数据和配置数据输入到fpga,整板模拟主时钟由一片ad9528提供,部分时钟挂载buffer扩充时钟路数,输出给4片adrv9009和fpga。

28.进一步地,监视通道模块采用变频+adc模式设计,adc采用ad9467。

29.如图3所示,外部电源模块包括12v电源、第一降压单元、第二降压单元和第三降压单元;12v电源的输出端分别与第一降压单元、第二降压单元和第三降压单元的输入端连接;第一降压单元将12v电压降压为1.2v、1.5v和1.8v电压输入到主控模块;第二降压单元将12v电源降压为2.5v电源输入到主控模块;第三降压单元将12v电源降压为3.3v电压输入到主控模块。

30.外部供电输入为12v,soc的内核与dsp内核1.0v均需要大功率供电,考虑保留较大的供电余量,采用具有3相供电的大功率电源ltc3773,共需要2片,每项最大供电电流可达20a,最大电流取决于外部mos管的选择,可以两相组合最大输出电流可达40a,符合本板的供电需求;其余电源可采用单项输出的tps54622和tlv62130,其中前者输出电流最大为6a,后者输出电流最大3a。ltc3773每相输出、tps54622和tlv62130均有独立的en管脚,便以做整板的上电时序。

31.还包括状态检测模块,状态检测模块包括温度监测单元和电压电流检测单元,所述温度监测单元和电压电流检测单元与所述fpga单元连接。

32.进一步地,电压检测采用maxim公司的max16065芯片进行电压检测,max16065可以同时管理12路系统电压,内置精度为1%的10位adc用于测量每路输入,并将结果与过压门限、欠压门限以及配置为欠压或过压的预警门限进行比较。当被测电压超出设定门限时发出故障报警信号。针对不同的故障条件可以配置最多三个独立的故障报警输出。max16065支持高达14v的电源电压,可直接采用多数系统中的12v中等总线电源供电。利用一个专用高边电流检测放大器精确监测(

±

2.5%)1个通道的电流。因此可通过此芯片检测输入端的电流。

33.进一步地,温度检测芯片采用ti公司的tmp75cidr,tmp75c是一款集成数字温度传感器,此传感器具有一个可由1.4v~3.6v电源供电运行的12位模数转换器,tmp75c能够以0.0625℃的分辨率读取温度,并且可在-55℃至+125℃的温度范围内额定运行。具有两线制接口的数字输出,多达8个引脚可编程总线地址。

34.以上所述仅是本实用新型的优选实施方式,应当理解本实用新型并非局限于本文所披露的形式,不应看作是对其他实施例的排除,而可用于各种其他组合、修改和环境,并能够在本文所述构想范围内,通过上述教导或相关领域的技术或知识进行改动。而本领域人员所进行的改动和变化不脱离本实用新型的精神和范围,则都应在本实用新型所附权利要求的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1