一种具有最佳导通时间的零电流检测电路

1.本实用新型涉及集成电路设计领域,更具体地,涉及一种具有最佳导通时间的零电流检测电路。

背景技术:

2.工作于临界导通模式(crm)的电源管理芯片通常内部会有一个零电流检测(zcd)电路。当检测到电感电流减小到零时刻,zcd电路产生一个检测信号送入逻辑控制部分,来控制功率管重新导通,让电感再次进入充电阶段。

3.如图1所示,为一种工作在临界导通模式下的功率因数校正升压电路(crm boost pfc)。当电感电流上升至比较器cmp的门限值时逻辑电路关断功率管q1,电感开始放电,当电感电流减小到零时刻,zcd电路通过检测辅助绕组上的电压信息来控制逻辑电路重新打开功率管,此时电感电流重新上升,通过上述的工作过程,电路通过可以工作在临界导通模式。

4.如图2所示,为一种常见的零电流检测电路,nm1-nm5是nmos管,pm1-pm5是pmos管,迟滞比较器u1为施密特触发器,zcd端口通过图1中的电阻rzcd接外部电感的辅助绕组。功率管由导通状态切换到关断状态时,此时vd=vo,通过辅助绕组变换之后此时zcd端口电压为高电位,当vzcd大于vh时,u1的输入为高电位,nm5导通,nm4截止,比较器的反转电位变为vl,此时zcd_out为零,功率管持续关断,电感电流持续下降。当电感电流下降到零时,由于电感与功率管寄生电容发生谐振,功率管与电感连接节点电压逐渐降低,即vd开始由vo下降,此时vzcd由于辅助绕组的作用也会由高电位开始下降。当vzcd下降到小于vl时,零电流检测电路比较器反转,zcd_out反转为高电位,通过逻辑电路控制功率管q1导通,使电感电流重新上升。

5.在临界导通模式下,功率管的最理想导通时刻应该是当其漏极电压vd在谐振过程中降低到零时开通功率管。较早的导通会在功率管的源漏两端产生大的vds,引入开关损耗;而较晚的导通会使电路进入断续导通模式(dcm),增加传输损耗。

6.而常见的零电流检测电路通过迟滞比较器u1检测zcd端口处连接的辅助绕组的电压,即zcd端口的电压,由迟滞比较器u1检测后,将zcd端口的电压与电压基准进行比较来判断电感电流下降到零的时刻,从而直接打开功率管。通过这种方式得到的功率管导通时刻与最佳导通时间相差较远,会引入较大的开关损耗,降低电路的传输效率。

7.有鉴于此,为了解决现有零电流检测电路得到的导通时刻与最佳导通时间相差较远的问题,本实用新型提出一种可实现功率管零电压开通、降低功率管开关损耗、电路传输效率高的,一种具有最佳导通时间的零电流检测电路。

技术实现要素:

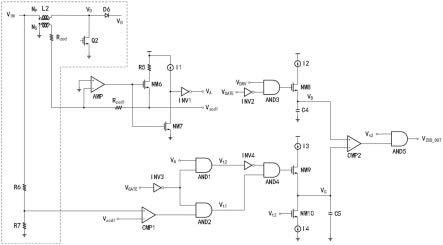

8.本实用新型提出一种具有最佳导通时间的零电流检测电路,可实现功率管零电压导通,降低功率管开关损耗,显著提高了检测电路的传输效率,相对于现有的检测电路而

言,本实用新型未使用迟滞比较器,避免了检测电路得到的导通时刻与最佳导通时间相差较远的问题,设置导通时刻计算电路,导通时刻计算电路结合t1与t2产生电路所输出v

t1

、v

t2

输出功率管最佳导通时刻信号v

zcd_out

,实现功率管零电压开通,降低了开关损耗并且提高了电路的传输效率。

9.一种具有最佳导通时间的零电流检测电路,包括升压拓扑结构、采样电路、t1与t2产生电路、导通时刻计算电路、门驱动延时采样电路,升压拓扑结构由电感l2与其辅助绕组、功率管q2、二极管d6组成,升压电感两端压降为v

in

,通过电感l2与其辅助绕组作用产生vd,电感l2与功率管q2的漏极、二极管d6正极连接,二极管d6负极电压为vo,所述辅助绕组输出端与采样电路输入端连接,所述辅助绕组用于得到与信号vd相关的信号v

zcd

,其特征在于,所述采样电路输出端与t1与t2产生电路输入端连接,采样电路用于采集输出信号va、信号v

zcd1

,导通时刻计算电路输入端分别与t1与t2产生电路输出端、门驱动延时采样电路输出端连接,所述t1与t2产生电路用于产生信号v

t1

、信号v

t2

并对信号v

t1

、信号v

t2

进行逻辑运算后输出,所述门驱动延时采样电路输入端分别接收有门驱动输出信号v

gate

、逻辑输出信号v

drv

,门驱动延时采样电路用于将门驱动输出信号v

gate

、逻辑输出信号v

drv

输出至导通时刻计算电路,导通时刻计算电路用于得到输出功率管最佳导通时刻信号的v

zcd_out

。

10.在一些实施方式中,所述导通时刻计算电路包括电流源i2、电流源i3、电流源i4、nmos管nm8、nmos管nm9、nmos管nm10、电容c4、电容c5、比较器cmp2、与门and5,电流源i2与nmos管nm8的漏极连接,门驱动延时采样电路输出端与nmos管nm8栅极连接,nmos管nm8的源极分别与电容c4、比较器cmp2的同相输入端连接,电流源i2在nmos管nm8导通时给电容c4充电,电容c4起到表征门驱动输出信号v

gate

与逻辑输出v

drv

的时间差t

delay

的作用,若门驱动输出信号v

gate

、逻辑输出信号v

drv

时间差t

delay

越大则电容c4处的电压越大,电容c4上的电压信号vb进入比较器cmp2的同相输入端;电流源i3与nmos管nm9的漏极连接,t1与t2产生电路输出端与nmos管nm9栅极连接;电流源i4与nmos管nm10的源极连接,信号v

t2

进入nmos管nm10的栅极,nmos管nm10的漏极与nmos管nm9的源极与比较器cmp2的反相输入端、电容c5连接,电流源i3在nmos管nm9导通时给电容c5充电;电流源i4在nmos管nm10导通时给电容c5放电,通过充放电得到电容c5上的电压vc,信号vc进入比较器cmp2的同相输入端;与门and5的一输入端与比较器cmp2的输出端连接,与门and5的另一输入端连接信号v

t2

,与门and5进行逻辑运算后输出功率管最佳导通时刻信号v

zcd_out

。

11.在一些实施方式中,周期t1是功率管q2导通的时间段,在周期t1期间,升压电感两端压降为v

in

,电感l2上的电感电流i

l

持续上升;当电感电流上升到限流值时,逻辑控制部分触发功率管q2关断,升压电感开始退磁,功率管q2的漏极电压vd近似等于二极管d6的输出电压vo;进入t3周期时,电感l2上的电感电流i

l

下降到0,此时升压电感完全退磁,功率管q2与升压电感的连接点发生lc谐振。

12.进一步的,在开关过程中的功率管q2的漏极电压vd的大小如表达式(s1)所示:其中f是升压电感和寄生电容的谐振频率;在t3期间,正弦波的中心幅度为v

in

,所以当v

in

小于vo的一半时,可以实现功率管q2零电压开通;在这种情况下,vd在t3期间变为零时导通功率管q2,升压电路可以以最小的开关

损耗打开功率管q2。

13.进一步的,电感l2与辅助绕组的连接的作用,可以得到与vd相关的信号v

zcd

,其大小如表达式(s2)所示:其中n

p

为初级侧线圈匝数,ns为辅助绕组的匝数,v

zcd

上的谐振波形是对称的正弦波形,其对称中心电压为0v;因此,v

zcd

过零的时刻之前和之后的波形在幅度上相等,并且符号相反;利用此特性,可以通过预先确定最佳导通时刻t3所对应的镜像点t1来预测零电压点t3;通过这种方式,电路可以通过检测t1和t2的时刻后确定t3。

14.在一些实施方式中,所述采样电路包括运算放大器amp、nmos管nm6、nmos管nm7、电阻r

zcd1

,所述辅助绕组通过电阻r

zcd1

与运算放大器amp反相输入端连接,运算放大器amp同相输入端接地,运算放大器amp输出端分别与nmos管nm6、nmos管nm7的栅极连接,nmos管nm6的漏极与电阻r5连接,电阻r5起到限流的作用,nmos管nm6的源极输出带有辅助绕组上的电压信息的信号v

zcd1

,mos管nm7的源极接地,mos管nm7的漏极分别连接电流源i1、反相器inv1的输入端,反相器inv1的输出端输出反应谐振中心时刻到来的信号va。

15.在一些实施方式中,所述t1与t2产生电路包括电阻r6、电阻r7、比较器cmp1、与门and1、与门and2、与门and4、反相器inv3、反相器inv4,门驱动输出信号v

gate

通过反相器inv3分别和与门and1一输入端、与门and2的一输入端连接,信号va和与门and2的另一输入端连接,与门and2经过逻辑运算后形成信号v

t2

,与门and1的输出端与反相器inv4的输入端连接,反相器inv4的输出端和与门and4的一输入端连接;信号v

in

通过电阻r6、电阻r7与比较器cmp1的同相输入端连接,信号v

zcd1

由采样电路输出后进入比较器cmp1的反相输入端,比较器cmp1的输出端与与门and2的另一输入端连接,与门and2进行逻辑运算后形成信号v

t1

,与门and2的输出端和与门and4的另一输入端连接,与门and4的输出端与nmos管nm9的栅极连接。

16.在一些实施方式中,当v

zcd

为高电压时,运算放大器amp的反相输入端输入为高,运算放大器amp输出端为0,nmos管nm6和nmos管nm7截止,此时信号v

zcd1

=信号v

zcd

,且信号va=0,当电感l2上的电感电流下降到0时,v

zcd

进入谐振周期,由(s2)的公式可以得到,在t2时刻,v

zcd

=0。

17.进一步的,当v

zcd

下降为负电压时,运算放大器amp的输出端电压为高,使nmos管nm6和nmos管nm7导通,此时信号va产生一个上升沿,这个上升沿所表示的时刻即为t2时刻,通过取r

zcd

=r

zcd1

,可在v

zcd

为负的情况下使v

zcd1

=-v

zcd

,因此在整个开关周期下可以得到v

zcd1

的值如(s3)所示:

[0018]vzcd1

=|v

zcd

|

ꢀꢀꢀ

(s3)

[0019]

在一些实施方式中,由表达式(s1)和表达式(s2)可知,当vd=0,此时为功率管q2的最佳导通时刻,此时根据谐振波形的对称性,则在t1时刻有

[0020]

进一步的,又由表达式(s3)得v

zcd1

=|v

zcd

|,所以取当比较器cmp1的反相端v

zcd1

小于时,比较器cmp1的输出得到一个上升沿信号,通过与门运算可以得到表示t1时刻到来的信号v

t1

;由谐振对称性可以得到t

3-t2=t

2-t1,所以可以由v

t1

和v

t2

来得到最佳导通时刻t3。

[0021]

进一步的,门驱动延时采样电路存在延迟t

delay

,电容c4会通过电流源i2的电流在该延迟时间t

delay

内充电,因此电容c4上的电压vb如表达式(s4)所示:

[0022]

进一步的,电容c5的充放电受到v

t1

和v

t2

的控制,在t1到t2这段时间内,nmos管nm9导通,nmos管nm10截止,电容c5开始充电;当t2时刻到来时,nmos管nm9截止,nmos管nm10导通,电容c5开始放电,放电过程直到电容c5上的电压vc小于电容c4上的电压vb时结束,这个时刻记为t

drv

,t

drv

表示的是逻辑电路产生开通信号的时刻;此时v

zcd_out

产生一个上升沿,控制后面的逻辑部分使v

gate

反转为高,导通功率管q2。

[0023]

进一步的,取电容c4、电容c5的容值相同都为c,电流源i2、电流源i3、电流源i4的电流大小都为i,通过如(s5)表达式所示:

[0024][0025]

进一步的,联立表达式(s4)和表达式(s5)可以得到如表达式(s6)所示:2t

2-t1=t

drv

+t

delay

=t3ꢀꢀꢀ

(s6)

[0026]

进一步的,由(s6)及上述分析可知,在t

drv

时刻v

zcd_out

产生一个上升沿,所以在经过门驱动延时t

delay

之后,得到的信号就是最佳导通时刻t3,实现了功率管q2的零电压导通。

[0027]

本实用新型的有益效果:本实用新型提出一种具有最佳导通时间的零电流检测电路,通过导通时刻计算电路包括电流源i2、电流源i3、电流源i4、nmos管nm8、nmos管nm9、nmos管nm10、电容c4、电容c5、比较器cmp2、与门and5,导通时刻计算电路结合t1与t2产生电路所输出v

t1

、v

t2

输出功率管最佳导通时刻信号v

zcd_out

,通过nmos管nm8将门驱动延时采样电路与比较器cmp2同相端连接,通过nmos管nm9、nmos管nm10将t1与t2产生电路输出端与比较器cmp2反相端连接,与门and5的一输入端与比较器cmp2的输出端连接,与门and5的另一输入端连接信号v

t2

,与门and5进行逻辑运算后输出功率管最佳导通时刻信号v

zcd_out

,可以实现功率管q2零电压开通,降低了开关损耗并且提高了电路的传输效率,并且通过门驱动延时采样电路检测逻辑输出信号v

drv

和门驱动信号v

gate

,以此来计算延迟时间t

delay

,提高电路传输精度。

附图说明

[0028]

图1为现有技术的一种工作在临界导通模式下的功率因数校正升压电路。

[0029]

图2为现有技术的一种常见的零电流检测电路。

[0030]

图3为本技术的具有最佳导通时间的零电流检测电路工作在临界导通模式下升压pfc变换器的各节点波形图。

[0031]

图4为本技术的具有最佳导通时间的零电流检测电路工作在临界导通模式下升压pfc变换器的谐振周期内的各节点波形图。

[0032]

图5为本技术的具有最佳导通时间的零电流检测电路。

[0033]

图6为本技术的采样电路得到的va和v

zcd1

在谐振周期内的波形图。

[0034]

图7为本技术的导通时刻计算电路的关键波形图。

具体实施方式

[0035]

描述以下实施例以辅助对本实用新型的理解。不意在且不应当以任何方式将实施例解释成为限制本实用新型的保护范围。

[0036]

在以下描述中,本领域的技术人员将认识到,在本论述的全文中,组件可描述为单独的功能单元(可包括子单元),但是本领域的技术人员将认识到,各种组件或其部分可划分成单独组件,或者可整合在一起(包括整合在单个的系统或组件内)。

[0037]

此外,附图内的组件或系统之间的连接并不旨在限于直接连接。相反,在这些组件之间的数据可由中间组件修改、重格式化、或以其它方式改变。另外,可使用另外或更少的连接。还应注意,术语“联接”、“连接”、或“输入”应理解为包括直接连接、通过一个或多个中间设备来进行的间接连接、和无线连接。

[0038]

实施例1:

[0039]

一种具有最佳导通时间的零电流检测电路,如图5所示,包括升压拓扑结构、采样电路、t1与t2产生电路、导通时刻计算电路、门驱动延时采样电路,升压拓扑结构由电感l2与其辅助绕组、功率管q2、二极管d6组成,升压电感两端压降为v

in

,通过电感l2与其辅助绕组作用产生vd,电感l2与功率管q2的漏极、二极管d6正极连接,二极管d6负极电压为vo,所述辅助绕组输出端与采样电路输入端连接,所述辅助绕组用于得到与信号vd相关的信号v

zcd

,其特征在于,所述采样电路输出端与t1与t2产生电路输入端连接,采样电路用于采集输出信号va、信号v

zcd1

,导通时刻计算电路输入端分别与t1与t2产生电路输出端、门驱动延时采样电路输出端连接,所述t1与t2产生电路用于产生信号v

t1

、信号v

t2

并对信号v

t1

、信号v

t2

进行逻辑运算后输出,所述门驱动延时采样电路输入端分别接收有门驱动输出信号v

gate

、逻辑输出信号v

drv

,门驱动延时采样电路用于将门驱动输出信号v

gate

、逻辑输出信号v

drv

输出至导通时刻计算电路,导通时刻计算电路用于得到输出功率管最佳导通时刻信号的v

zcd_out

。

[0040]

所述导通时刻计算电路包括电流源i2、电流源i3、电流源i4、nmos管nm8、nmos管nm9、nmos管nm10、电容c4、电容c5、比较器cmp2、与门and5,电流源i2与nmos管nm8的漏极连接,门驱动延时采样电路输出端与nmos管nm8栅极连接,nmos管nm8的源极分别与电容c4、比较器cmp2的同相输入端连接,电流源i2在nmos管nm8导通时给电容c4充电,电容c4起到表征门驱动输出信号v

gate

与逻辑输出v

drv

的时间差t

delay

的作用,若门驱动输出信号v

gate

、逻辑输出信号v

drv

时间差t

delay

越大则电容c4处的电压越大,电容c4上的电压信号vb进入比较器cmp2的同相输入端;电流源i3与nmos管nm9的漏极连接,t1与t2产生电路输出端与nmos管nm9栅极连接;电流源i4与nmos管nm10的源极连接,信号v

t2

进入nmos管nm10的栅极,nmos管nm10的漏极与nmos管nm9的源极与比较器cmp2的反相输入端、电容c5连接,电流源i3在nmos管

nm9导通时给电容c5充电;电流源i4在nmos管nm10导通时给电容c5放电,通过充放电得到电容c5上的电压vc,信号vc进入比较器cmp2的同相输入端;与门and5的一输入端与比较器cmp2的输出端连接,与门and5的另一输入端连接信号v

t2

,与门and5进行逻辑运算后输出功率管最佳导通时刻信号v

zcd_out

。

[0041]

如图3所示,周期t1是功率管q2导通的时间段,在周期t1期间,升压电感两端压降为v

in

,电感l2上的电感电流i

l

持续上升;当电感电流上升到限流值时,逻辑控制部分触发功率管q2关断,升压电感开始退磁,功率管q2的漏极电压vd近似等于二极管d6的输出电压vo;进入t3周期时,电感l2上的电感电流i

l

下降到0,此时升压电感完全退磁,功率管q2与升压电感的连接点发生lc谐振。

[0042]

如图4所示,在开关过程中的功率管q2的漏极电压vd的大小如表达式(s1)所示:其中f是升压电感和寄生电容的谐振频率;在t3期间,正弦波的中心幅度为v

in

,所以当v

in

小于vo的一半时,可以实现功率管q2零电压开通;在这种情况下,vd在t3期间变为零时导通功率管q2,升压电路可以以最小的开关损耗打开功率管q2。

[0043]

电感l2与辅助绕组的连接的作用,可以得到与vd相关的信号v

zcd

,其大小如表达式(s2)所示:其中n

p

为初级侧线圈匝数,ns为辅助绕组的匝数,v

zcd

上的谐振波形是对称的正弦波形,其对称中心电压为0v;因此,v

zcd

过零的时刻之前和之后的波形在幅度上相等,并且符号相反;利用此特性,可以通过预先确定最佳导通时刻t3所对应的镜像点t1来预测零电压点t3;通过这种方式,电路可以通过检测t1和t2的时刻后确定t3。

[0044]

所述采样电路包括运算放大器amp、nmos管nm6、nmos管nm7、电阻r

zcd1

,所述辅助绕组通过电阻r

zcd1

与运算放大器amp反相输入端连接,运算放大器amp同相输入端接地,运算放大器amp输出端分别与nmos管nm6、nmos管nm7的栅极连接,nmos管nm6的漏极与电阻r5连接,电阻r5起到限流的作用,nmos管nm6的源极输出带有辅助绕组上的电压信息的信号v

zcd1

,mos管nm7的源极接地,mos管nm7的漏极分别连接电流源i1、反相器inv1的输入端,反相器inv1的输出端输出反应谐振中心时刻到来的信号va。

[0045]

所述t1与t2产生电路包括电阻r6、电阻r7、比较器cmp1、与门and1、与门and2、与门and4、反相器inv3、反相器inv4,门驱动输出信号v

gate

通过反相器inv3分别和与门and1一输入端、与门and2的一输入端连接,信号va和与门and2的另一输入端连接,与门and2经过逻辑运算后形成信号v

t2

,与门and1的输出端与反相器inv4的输入端连接,反相器inv4的输出端和与门and4的一输入端连接;信号v

in

通过电阻r6、电阻r7与比较器cmp1的同相输入端连接,信号v

zcd1

由采样电路输出后进入比较器cmp1的反相输入端,比较器cmp1的输出端与与门and2的另一输入端连接,与门and2进行逻辑运算后形成信号v

t1

,与门and2的输出端和与门

and4的另一输入端连接,与门and4的输出端与nmos管nm9的栅极连接。

[0046]

如图6所示,可得到va和v

zcd1

在谐振周期内的波形,当v

zcd

为高电压时,运算放大器amp的反相输入端输入为高,运算放大器amp输出端为0,nmos管nm6和nmos管nm7截止,此时信号v

zcd1

=信号v

zcd

,且信号va=0,当电感l2上的电感电流下降到0时,v

zcd

进入谐振周期,由(s2)的公式可以得到,在t2时刻,v

zcd

=0。

[0047]

当v

zcd

下降为负电压时,运算放大器amp的输出端电压为高,使nmos管nm6和nmos管nm7导通,此时信号va产生一个上升沿,这个上升沿所表示的时刻即为t2时刻,通过取r

zcd

=r

zcd1

,可在v

zcd

为负的情况下使v

zcd1

=-v

zcd

,因此在整个开关周期下可以得到v

zcd1

的值如(s3)所示:v

zcd1

=|v

zcd

|

ꢀꢀꢀꢀ

(s3)

[0048]

由表达式(s1)和表达式(s2)可知,当vd=0,此时为功率管q2的最佳导通时刻,此时根据谐振波形的对称性,则在t1时刻有

[0049]

又由表达式(s3)得v

zcd1

=|v

zcd

|,所以取当比较器cmp1的反相端v

zcd1

小于时,比较器cmp1的输出得到一个上升沿信号,通过与门运算可以得到表示t1时刻到来的信号v

t1

;由谐振对称性可以得到t

3-t2=t

2-t1,所以可以由v

t1

和v

t2

来得到最佳导通时刻t3。

[0050]

如图7所示,可得到下列导通时刻计算电路的关键波形,门驱动延时采样电路存在延迟t

delay

,电容c4会通过电流源i2的电流在该延迟时间t

delay

内充电,因此电容c4上的电压vb如表达式(s4)所示:

[0051]

电容c5的充放电受到v

t1

和v

t2

的控制,在t1到t2这段时间内,nmos管nm9导通,nmos管nm10截止,电容c5开始充电;当t2时刻到来时,nmos管nm9截止,nmos管nm10导通,电容c5开始放电,放电过程直到电容c5上的电压vc小于c4上的电压vb时结束,这个时刻记为t

drv

,t

drv

表示的是逻辑电路产生开通信号的时刻;此时v

zcd_out

产生一个上升沿,控制后面的逻辑部分使v

gate

反转为高,导通功率管q2。

[0052]

取电容c4、电容c5的容值相同都为c,电流源i2、电流源i3、电流源i4的电流大小都为i,通过如(s5)表达式所示:

[0053][0054]

联立表达式(s4)和表达式(s5)可以得到如表达式(s6)所示:

[0055]

2t

2-t1=t

drv

+t

delay

=t3ꢀꢀꢀ

(s6)

[0056]

由(s6)及上述分析可知,在t

drv

时刻v

zcd_out

产生一个上升沿,所以在经过门驱动延时t

delay

之后,得到的信号就是最佳导通时刻t3,实现了功率管q2的零电压导通。

[0057]

本实用新型的工作原理:首先,通过升压拓扑结构与采样电路连接得到带有辅助绕组上的电压信息的信号v

zcd1

,同时通过电感和电容的谐振特性得到va,将v

zcd1

、va输入进t1与t2产生电路,由t1与t2产生电路输出检测信号v

t1

、信号v

t2

,,t1与t2产生电路进行逻辑运算输出至导通时刻计算电路的一输入端,同时门驱动延时采样电路将门驱动输出信号v

gate

、

逻辑输出信号v

drv

进行逻辑运算后输出至导通时刻计算电路的另一个输入端,导通时刻计算电路输出功率管最佳导通时刻信号的v

zcd_out

。

[0058]

本实用新型的有益效果:本实用新型提出一种具有最佳导通时间的零电流检测电路,通过导通时刻计算电路包括电流源i2、电流源i3、电流源i4、nmos管nm8、nmos管nm9、nmos管nm10、电容c4、电容c5、比较器cmp2、与门and5,导通时刻计算电路结合t1与t2产生电路所输出v

t1

、v

t2

输出功率管最佳导通时刻信号v

zcd_out

,通过nmos管nm8将门驱动延时采样电路与比较器cmp2同相端连接,通过nmos管nm9、nmos管nm10将t1与t2产生电路输出端与比较器cmp2反相端连接,与门and5的一输入端与比较器cmp2的输出端连接,与门and5的另一输入端连接信号v

t2

,与门and5进行逻辑运算后输出功率管最佳导通时刻信号v

zcd_out

,可以实现功率管q2零电压开通,降低了开关损耗并且提高了电路的传输效率,并且通过检测逻辑输出信号v

drv

和门驱动信号v

gate

,以此来计算延迟时间t

delay

,提高电路传输精度。

[0059]

尽管本实用新型已公开了多个方面和实施方式,但是其它方面和实施方式对本领域技术人员而言将是显而易见的,在不脱离本实用新型构思的前提下,还可以做出若干变形和改进,这些都属于本实用新型的保护范围。本实用新型公开的多个方面和实施方式仅用于举例说明,其并非旨在限制本实用新型,本实用新型的实际保护范围以权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1