延迟偏差测量电路的制作方法

本申请涉及校准校验,特别是涉及一种延迟偏差测量电路。

背景技术:

1、ate自动化测试设备,作为一种对芯片功能和性能检测的专用设备,在性能检测方面具有较高的精度标准,特别是存在与ate设备中的数字资源版timing校准技术,其校准精度会直接影响到设备整体的测试精度以及测试能力,校准精度一般为多通道间的时间偏差值。

2、目前对于多通道间的偏差值的测量方法是通过高速示波器等高成本测量设备测量,是利用机械臂等一次将被测信号与基准信号输入到专用设备,接着读取测量结果,或是通过测量过程复杂的高精度时间测量芯片进行测量,该方式是通过切换多路继电器开关,将被测信号一次引入到高精度时间测量芯片中,接着读取结果。可以看出,当前相关技术中对于多通道间偏差值测量的方法存在测量成本高或测量过程复杂、容错率低的问题,不适用于测量。基于此,针对当前相关技术中存在对于多通道间延迟偏差的测量存在测量成本高或测量过程复杂、容错率低的问题目前还没有提出有效的解决方案。

技术实现思路

1、基于此,有必要针对上述技术问题,提供一种延迟偏差测量电路。

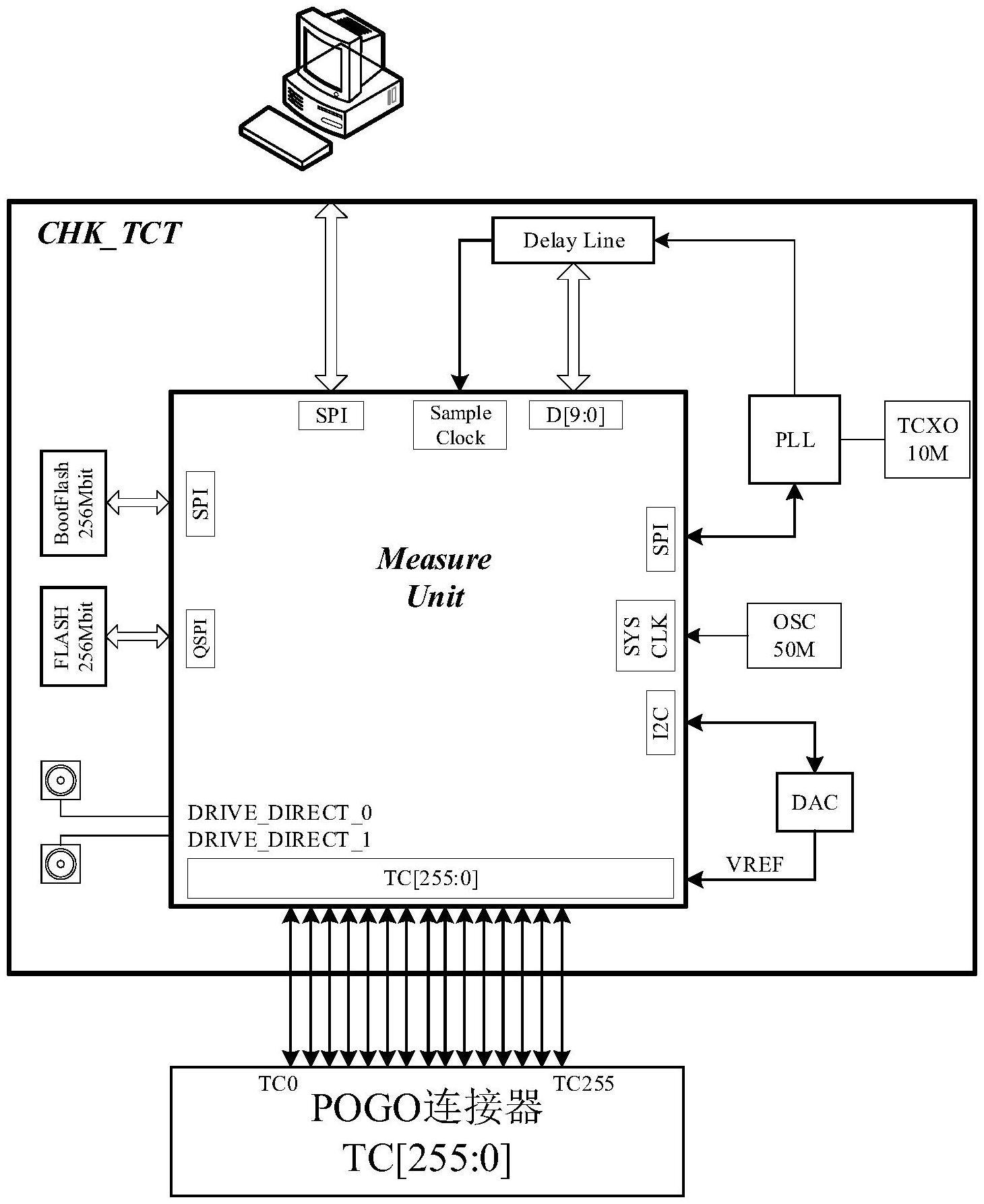

2、本申请提供一种延迟偏差测量电路,包括:

3、时钟信号产生模块,用于生成多个不同相位的时钟信号,相邻所述时钟信号的相位偏差为第一预设时钟周期;

4、测量模块,与所述时钟信号产生模块相连,用于接收多个待测信号及各所述时钟信号,并基于各所述时钟信号依次对每一所述待测信号采样,以确定各所述待测信号的相位偏差值。

5、在其中一个实施例中,所述时钟信号产生模块包括相连的初始时钟产生单元和延迟单元,所述延迟单元与所述测量模块相连,所述初始时钟产生单元用于产生初始时钟信号,所述延迟单元用于对所述初始时钟信号进行延迟,生成多个不同相位的时钟信号。

6、在其中一个实施例中,所述初始时钟产生单元还与所述测量模块相连,用于接收所述测量模块的控制指令并生成对应频率的初始时钟信号。

7、在其中一个实施例中,还包括第一存储模块,所述第一存储模块与所述测量模块相连,用于存储所述测量模块的测量程序。

8、在其中一个实施例中,还包括第二存储模块,所述第二存储模块与所述测量模块相连,用于存储所述测量模块的测量结果。

9、在其中一个实施例中,还包括晶振模块,所述晶振模块与所述测量模块相连,用于向所述测量模块提供基准时钟信号。

10、在其中一个实施例中,还包括基准电压模块,所述基准电压模块与所述测量模块相连,用于接收所述测量模块的控制指令并生成对应的基准电压。

11、在其中一个实施例中,还包括上位机,所述上位机与所述测量模块相连。

12、在其中一个实施例中,所述测量模块与多个待测的数字通道相连,以接收各所述待测信号。

13、在其中一个实施例中,所述测量模块为fpga芯片。

14、上述延迟偏差测量电路,通过时钟信号产生模块生成多个时钟信号,且相邻所述时钟信号的相位偏差为第一预设时钟周期;测量模块,与所述时钟信号产生模块相连,用于接收多个待测信号及各所述时钟信号,并基于各所述时钟信号依次对每一所述待测信号采样,以确定各所述待测信号的相位偏差值,解决了相关技术中存在对于多通道间延迟偏差的测量存在测量成本高或测量过程复杂、容错率低的问题,实现了测量多通道间延迟偏差时降低测量成本以及测量复杂程度。

技术特征:

1.一种延迟偏差测量电路,其特征在于,包括:

2.根据权利要求1所述的延迟偏差测量电路,其特征在于,所述初始时钟产生单元还与所述测量模块相连,用于接收所述测量模块的控制指令并生成对应频率的初始时钟信号。

3.根据权利要求1-2任一项所述的延迟偏差测量电路,其特征在于,还包括第一存储模块,所述第一存储模块与所述测量模块相连,用于存储所述测量模块的测量程序。

4.根据权利要求1-2任一项所述的延迟偏差测量电路,其特征在于,还包括第二存储模块,所述第二存储模块与所述测量模块相连,用于存储所述测量模块的测量结果。

5.根据权利要求1-2任一项所述的延迟偏差测量电路,其特征在于,还包括晶振模块,所述晶振模块与所述测量模块相连,用于向所述测量模块提供基准时钟信号。

6.根据权利要求1-2任一项所述的延迟偏差测量电路,其特征在于,还包括基准电压模块,所述基准电压模块与所述测量模块相连,用于接收所述测量模块的控制指令并生成对应的基准电压。

7.根据权利要求1-2任一项所述的延迟偏差测量电路,其特征在于,还包括上位机,所述上位机与所述测量模块相连。

8.根据权利要求1-2任一项所述的延迟偏差测量电路,其特征在于,所述测量模块与多个待测的数字通道相连,以接收各所述待测信号。

9.根据权利要求1-2任一项所述的延迟偏差测量电路,其特征在于,所述测量模块包括fpga芯片。

技术总结

本申请涉及一种延迟偏差测量电路。所述延迟偏差测量电路包括:时钟信号产生模块,用于生成多个不同相位的时钟信号,相邻所述时钟信号的相位偏差为第一预设时钟周期;测量模块,与所述时钟信号产生模块相连,用于接收多个待测信号及各所述时钟信号,并基于各所述时钟信号依次对每一所述待测信号采样,以确定各所述待测信号的相位偏差值,解决了相关技术中存在对于多通道间延迟偏差的测量存在测量成本高或测量过程复杂、容错率低的问题,实现了测量多通道间延迟偏差时降低测量成本以及测量复杂程度。

技术研发人员:王俊,王立新,杜昊

受保护的技术使用者:杭州长川科技股份有限公司

技术研发日:20221028

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!