一种SIL4功能安全输出的自检电路的制作方法

本技术属于铁路通信信号,具体涉及一种sil4功能安全输出的自检电路。

背景技术:

1、现今,sil4功能安全的io输出通道通常采用双通道设计,每个通道设计两个mosfet,两个mosfet分别受两模控制cpu的控制,对于通道进行自检时,需要检测mosfet是否失效以及每个通道是否按输出要求进行输出,由于设计采用双通道,自检时一个通道按输出要求进行输出,另一个执行自检,自检完成后检查另一通道。

2、但现有技术中的双通道在进行自检时,自检电压是额外加入的,自检时容易将自检电压注入输入电路,影响输入接口电压,同时,输入接口的电压也会对自检电压产生影响,而且,现有的mosfet为共电源设计,这样对mosfet自检时,会受到电源的影响,进而影响自检电路对输出状态的判断,而且也限制了负载的接入方式。

3、申请人依据检索式((sil4/desc and 自检/desc and mos管/desc))检索到一篇公布号为cn110830013a的专利,公开了一种具备实时自检功能的安全开关实现电路,包括vcu处理单元、驱动单元、mos开关单元和回采单元,vcu处理单元通过驱动单元与mos开关单元连接,所述的回采单元与mos开关单元连接,但上述专利文件中所记载的技术方案中,mos开关管为共电源设计,mos管k1和k2只能接电源vcc,限制了负载只能从output端接入,同时,mos开关单元中的四个mos管是两上管并联、两下管并联,总体串联的连接方式,每个通道并非独立通道。

技术实现思路

1、为解决上述技术问题,本实用新型提供一种sil4功能安全输出的自检电路。

2、具体方案如下:

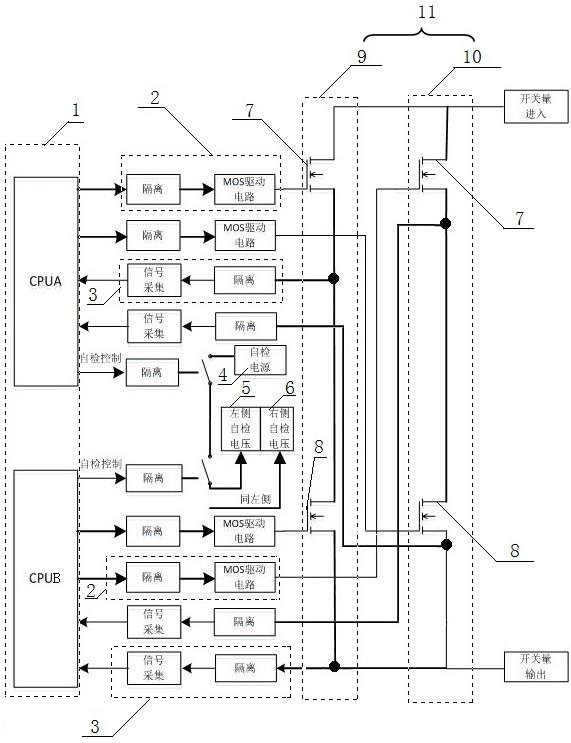

3、一种sil功能安全输出的自检电路,包括双模cpu,还包括双通道io输出模块,所述双通道io输出模块包括左通道和右通道,左通道中和右通道中均设置有输入端、上mos管、下mos管和输出端,所述上mos管和下mos管串接于输入端和输出端之间,双通道io输出模块中的每一个mos管处均设置有隔离驱动模块和信号采集模块,所述双通道io输出模块通过信号采集模块与双模cpu电连接,所述双模cpu通过隔离驱动模块与双通道io输出模块电连接,所述隔离驱动模块内设置有悬浮地,每个通道的上mos管和下mos管均与所述悬浮地电连接。

4、每个通道的输入端和输出端均设置有第一防护二极管,每个通道的输入端均通过第一防护二极管与上mos管的电连接,所述下mos管通过第一防护二极管与输出端电连接,所述左通道的输入端与右通道的输入端电连接,所述左通道的输出端与右通道的输出端电连接。

5、所述隔离驱动模块包括隔离电路和mos驱动电路,所述隔离电路包括推挽输入电路和隔离变压器,所述双模cpu通过推挽输入电路与隔离变压器电连接,所述隔离变压器与mos驱动电路电连接。

6、所述推挽输入电路包括npn型三极管和pnp型三极管,所述双模cpu与npn型三极管或pnp型三极管的基极电连接,npn型三极管的基极与pnp型三极管的基极电连接,npn型三极管的发射极与pnp型三极管的发射极电连接,npn型三极管的发射极或pnp型三极管的发射极与隔离变压器电连接。

7、所述mos驱动电路为mos驱动芯片,所述mos驱动芯片的接地端为悬浮地,每个通道的上mos管的源极和下mos管的源极均与mos驱动芯片的悬浮地电连接,每个通道的上mos管的栅极和下mos管的栅极均与mos驱动芯片的输入端电连接。

8、每个通道的上mos管的源极处和下mos管的源极处均设置采样端,所述信号采样模块为光耦,所述采样端通过光耦与所述双模cpu电连接。

9、所述自检电路中还包括自检电源,左侧自检电压输入端、右侧自检电压输入端、继电器和第二防护二极管,所述双模cpu通过继电器与自检电源电连接,所述自检电源分别与左侧自检电压输入端和右侧自检电压输入端电连接,每个通道的上mos管处的漏极还均连接有第二防护二极管,所述左侧自检电压输入端通过第二防护二极管与左通道的上mos管电连接,所述右侧自检电压输入端通过第二防护二极管与右通道的上mos管电连接。

10、本实用新型公开了一种sil4功能安全输出的自检电路,在隔离驱动模块内设置有悬浮地,每个通道内的mos管与悬浮地电连接,对mos管的自检不受外部电路的干扰,同时每个通道中设置第一防护二极管和第二防护二极管,使得自检电压不会反灌入输入端,同时输入端电压不会影响自检电压,又由于输出电路和双模cpu所在电路电气隔离,使得双通道io输出模块类似于电气无关节点,可应用于不同电压等级的电路中,其电路上方和下方均可以接负载,用途更加广阔,并且满足sil4的功能安全要求。

技术特征:

1.一种sil4功能安全输出的自检电路,包括双模cpu(1),其特征在于:还包括双通道io输出模块(11),所述双通道io输出模块(11)包括左通道(9)和右通道(10),左通道(9)中和右通道(10)中均设置有输入端、上mos管(7)、下mos管(8)和输出端,所述上mos管(7)和下mos管(8)串接于输入端和输出端之间,双通道io输出模块(11)中的每一个mos管处均设置有隔离驱动模块(2)和信号采集模块(3),所述双通道io输出模块(11)通过信号采集模块(3)与双模cpu(1)电连接,所述双模cpu(1)通过隔离驱动模块(2)与双通道io输出模块(11)电连接,所述隔离驱动模块(2)内设置有悬浮地(18),每个通道的上mos管(7)和下mos管(8)均与所述悬浮地(18)电连接。

2.根据权利要求1所述的sil4功能安全输出的自检电路,其特征在于:每个通道的输入端和输出端均设置有第一防护二极管(12),每个通道的输入端均通过第一防护二极管(12)与上mos管(7)的电连接,所述下mos管(8)通过第一防护二极管(12)与输出端电连接,所述左通道(9)的输入端与右通道(10)的输入端电连接,所述左通道(9)的输出端与右通道(10)的输出端电连接。

3.根据权利要求1所述的sil4功能安全输出的自检电路,其特征在于:所述隔离驱动模块(2)包括隔离电路和mos驱动电路,所述隔离电路包括推挽输入电路(15)和隔离变压器(16),所述双模cpu(1)通过推挽输入电路(15)与隔离变压器(16)电连接,所述隔离变压器(16)与mos驱动电路电连接。

4.根据权利要求3所述的sil4功能安全输出的自检电路,其特征在于:所述推挽输入电路(15)包括npn型三极管和pnp型三极管,所述双模cpu(1)与npn型三极管或pnp型三极管的基极电连接,npn型三极管的基极与pnp型三极管的基极电连接,npn型三极管的发射极与pnp型三极管的发射极电连接,npn型三极管的发射极或pnp型三极管的发射极与隔离变压器(16)电连接。

5.根据权利要求3所述的sil4功能安全输出的自检电路,其特征在于:所述mos驱动电路为mos驱动芯片(19),所述mos驱动芯片(19)的接地端为悬浮地(18),每个通道的上mos管(7)的源极和下mos管(8)的源极均与mos驱动芯片(19)的悬浮地(18)电连接,每个通道的上mos管(7)的栅极和下mos管(8)的栅极均与mos驱动芯片(19)的输入端电连接。

6.根据权利要求5所述的sil4功能安全输出的自检电路,其特征在于:每个通道的上mos管(7)的源极处和下mos管(8)的源极处均设置采样端(14),所述信号采集模块为光耦,所述采样端(14)通过光耦与所述双模cpu(1)电连接。

7.根据权利要求1所述的sil4功能安全输出的自检电路,其特征在于:所述自检电路中还包括自检电源(4),左侧自检电压输入端(5)、右侧自检电压输入端(6)、继电器和第二防护二极管(13),所述双模cpu(1)通过继电器与自检电源(4)电连接,所述自检电源(4)分别与左侧自检电压输入端(5)和右侧自检电压输入端(6)电连接,每个通道的上mos管(7)处的漏极还均连接有第二防护二极管(13),所述左侧自检电压输入端(5)通过第二防护二极管(13)与左通道(9)的上mos管(7)电连接,所述右侧自检电压输入端(6)通过第二防护二极管(13)与右通道(10)的上mos管(7)电连接。

技术总结

本技术公开了一种SIL4功能安全输出的自检电路,包括双模CPU,双通道IO输出模块,双通道IO输出模块包括左通道和右通道,左通道中和右通道中均设置有输入端、上MOS管、下MOS管和输出端,上MOS管和下MOS管串接于输入端和输出端之间,每一个MOS管处均设置隔离驱动模块和信号采集模块,隔离驱动模块内设置有悬浮地,每个通道的上MOS管和下MOS管均与悬浮地电连接,使得双通道IO输出模块类似于电气无关节点,可应用于不同电压等级的电路中,其电路上方和下方均可以接负载,用途更加广阔,并且满足SIL4的功能安全要求。

技术研发人员:郑智华,朱佳,王栋博,尹艳松,韩伟坤,孙海涛,尹星,左元堃,李政,王仕财

受保护的技术使用者:河南思维轨道交通技术研究院有限公司

技术研发日:20221212

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!