数字下垂检测器、其校准方法及半导体装置与流程

发明构思涉及数字下垂(droop)检测器、半导体装置及数字下垂检测器的校准方法。

背景技术:

1、随着半导体装置的集成度和/或大小增加并且工作速度提高,功耗也相应地增加。因此,半导体装置的低功耗性能正变得日益重要。诸如应用处理器的片上系统(soc)包括高性能功能块(或知识产权(ip)块、ip核等)。提供给这些功能块的电源电压可以根据工作环境或任务的级别而变化。一般而言,为了为电源电压大大地降低的下垂现象作准备,设置了向电源电压提供足够裕度(margin)的保护带。然而,设置相对高的保护带增加soc的功耗,这可能会削弱产品的竞争力。

2、集成数字电路消耗大量电力以高速度工作。此时,由于负载电流的突然改变而发生电源电压的下垂。通过检测电源电压的下垂并且调整时钟,可以迅速地恢复电源电压。为了减少和/或防止数字电路由于下垂而导致的故障,期望和/或有必要准确地检测下垂。

3、数字下垂检测器(在下文中,ddd)被广泛地使用,因为由于其在数字电路设计过程期间使用了数字标准单元库而能够被放置在数字电路周围。然而,ddd易受过程/温度改变影响。因此,需要能够有效地对在半导体装置的数字功能块中使用的ddd中的过程/温度的改变进行补偿的技术。

技术实现思路

1、发明构思的各种示例实施例涉及一种用于检测在电源电压中是否发生下垂的数字下垂检测器、一种包括所述数字下垂检测器的半导体装置和/或一种用于所述数字下垂检测器的校准方法等。

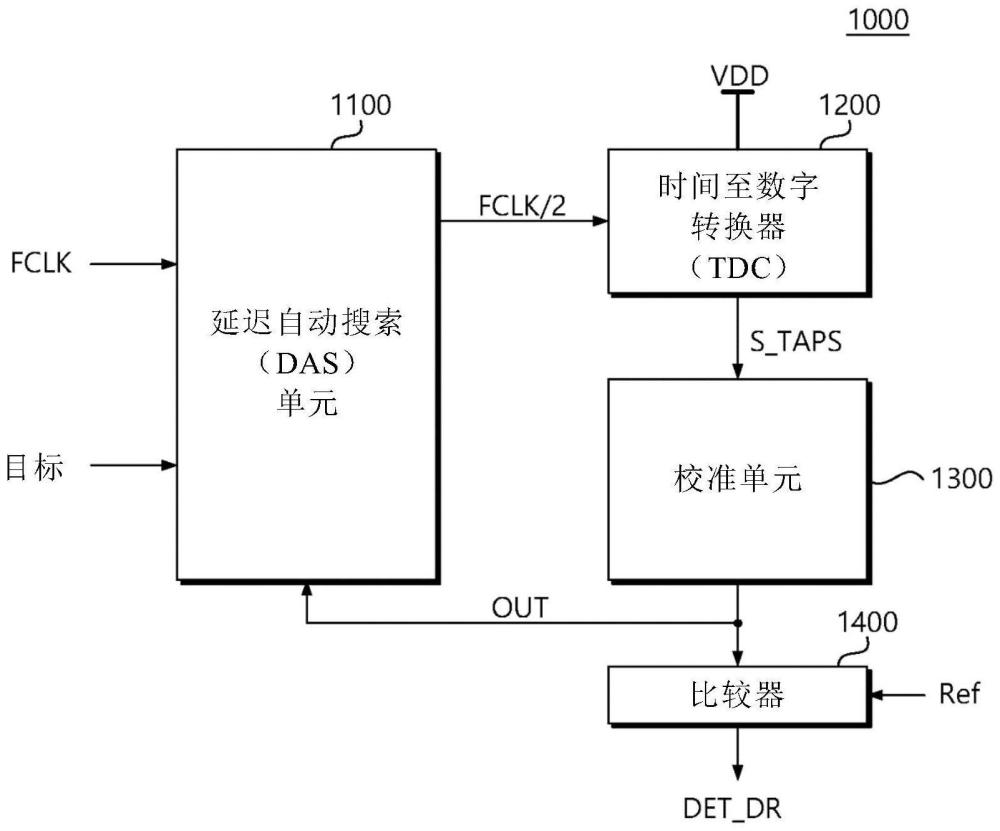

2、一种数字下垂检测器可以包括:处理电路,所述处理电路被配置为:响应于时钟信号来检测电源电压的电压电平改变,所述检测所述电压电平改变包括将所检测到的电压电平改变转换成第一代码;校正所述第一代码中包括的至少一个非线性,所述校正包括将所述第一代码转换成第二代码和目标范围;以及基于所述第二代码来调整所述时钟信号的延迟幅度。

3、一种半导体装置,所述半导体装置包括:至少一个ip核,所述至少一个ip核被配置为接收电源电压以执行至少一个处理操作,所述ip核即知识产权核;数字下垂检测器,所述数字下垂检测器被配置为检测所述电源电压的下垂并且输出下垂检测信号;时钟调制电路,所述时钟调制电路被配置为通过响应于所述下垂检测信号改变输入时钟信号的频率来基于所述输入时钟信号生成自适应时钟信号,并且将所述自适应时钟信号提供给所述ip核,并且所述数字下垂检测器进一步被配置为:将所述电源电压的电压电平改变转换成第一代码,基于目标范围将所述第一代码中包括的至少一个非线性转换成第二代码,以及基于所述第二代码来调整所述自适应时钟信号的延迟幅度。

4、一种数字下垂检测器的校准方法,所述方法包括:检测电源电压的电压电平改变;基于所检测到的电源电压的电压电平改变,生成输出代码;通过应用三点校准技术校正所述输出代码的过程变化相关非线性来生成过程校正代码;通过应用两点校准技术校正所述过程校正代码中的温度相关非线性来生成温度校正代码;以及基于所述过程校正代码来调整时钟信号的延迟。

技术特征:

1.一种数字下垂检测器,所述数字下垂检测器包括:

2.根据权利要求1所述的数字下垂检测器,其中,所述处理电路包括:

3.根据权利要求2所述的数字下垂检测器,其中,所述相位插值器链包括以多个层的级联形式连接的多个相位插值器,所述多个相位插值器被配置为:细分所述缓冲器的所述输入端子和所述输出端子之间的所述延迟时间。

4.根据权利要求1所述的数字下垂检测器,所述处理电路还被配置为:

5.根据权利要求4所述的数字下垂检测器,其中,所述处理电路进一步被配置为:通过对所述原始代码使用三点校准技术来生成所述过程校正代码,所述三点校准技术包括在所述电源电压的三个期望电压电平下校正与所述多个过程速度中的每一个过程速度相关联的所述原始代码的代码值。

6.根据权利要求4所述的数字下垂检测器,其中,所述处理电路进一步被配置为:通过对所述过程校正代码使用两点校准技术来生成所述温度校正代码,所述两点校准技术包括在所述电源电压的两个期望电压电平下校正与所述多个温度中的每一个温度相关联的所述过程校正代码的代码值。

7.根据权利要求4所述的数字下垂检测器,其中,所述处理电路进一步被配置为:使用校准单元来生成所述过程校正代码或所述温度校正代码。

8.根据权利要求4所述的数字下垂检测器,其中,所述处理电路进一步被配置为:使用查找表来生成所述过程校正代码或所述温度校正代码。

9.根据权利要求4所述的数字下垂检测器,其中,所述处理电路进一步被配置为被供应有用于校正所述原始代码或所述过程校正代码的非线性的外部计算的系数。

10.根据权利要求1所述的数字下垂检测器,其中,所述处理电路进一步被配置为:

11.根据权利要求1所述的数字下垂检测器,其中,所述处理电路进一步被配置为:

12.一种半导体装置,所述半导体装置包括:

13.根据权利要求12所述的半导体装置,其中,所述数字下垂检测器进一步被配置为:通过使用用于划分缓冲器的输入端子和输出端子之间的延迟的相位插值技术来生成所述第一代码。

14.根据权利要求12所述的半导体装置,其中,所述数字下垂检测器进一步被配置为:

15.根据权利要求14所述的半导体装置,其中,所述数字下垂检测器进一步被配置为:通过从校准单元接收所述过程校正代码或所述温度校正代码,来确定所述过程校正代码或者确定所述温度校正代码。

16.根据权利要求14所述的半导体装置,其中,所述数字下垂检测器进一步被配置为:使用在所述数字下垂检测器中存储的查找表,来确定所述过程校正代码或者确定所述温度校正代码。

17.根据权利要求12所述的半导体装置,其中,所述数字下垂检测器进一步被配置为:

18.一种数字下垂检测器的校准方法,所述方法包括:

19.根据权利要求18所述的方法,其中,所述三点校准技术或所述两点校准技术是使用校准单元或查找表来执行的。

20.根据权利要求18所述的方法,所述方法还包括:

技术总结

提供了数字下垂检测器、其校准方法及半导体装置。所述数字下垂检测器可以包括:处理电路,所述处理电路被配置为:响应于时钟信号来检测电源电压的电压电平改变,所述检测所述电压电平改变包括将所检测到的电压电平改变转换成第一代码;校正所述第一代码中包括的至少一个非线性,所述校正包括将所述第一代码转换成第二代码和目标范围;以及基于所述第二代码来调整所述时钟信号的延迟幅度。

技术研发人员:李相宪,申熙旭,李僖埈,李柾昊,曹永载,崔炳䝬

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!