一种FPGA芯片测试方法、装置、电子设备及存储介质与流程

本发明涉及芯片测试,尤其涉及一种fpga芯片测试方法、装置、电子设备及计算机可读存储介质。

背景技术:

1、fpga(field programmable gatearray,现场可编程门阵列)具有高性能、低能耗和可重构等特点,这使得基于fpga的产品在各类终端市场中广泛应用。终端用户在把产品推出市场前,会对产品所用芯片的功能性和可靠性进行严格的测试,以确保产品使用的稳定性;而且因为fpga可编程的特点,终端用户对fpga芯片版本的完整性和一致性有着很高的要求。fpga的可编程特性使得芯片集成的逻辑资源非常丰富,不同的终端用户会根据产品形态不同,选择不同逻辑资源组合实现多样化的功能。传统芯片的全资源检测只是针对逻辑单元的检测,并不能覆盖用户功能性测试,用户逻辑开发工程师的手动测试,往往也会出现测试效率低、测试覆盖率不足等问题。

技术实现思路

1、本发明的目的在于提供一种fpga芯片测试方法、装置、电子设备及计算机可读存储介质,以解决现有技术中测试效率低、测试覆盖率的技术问题。

2、本发明的技术方案如下,提供了一种fpga芯片测试方法,包括:

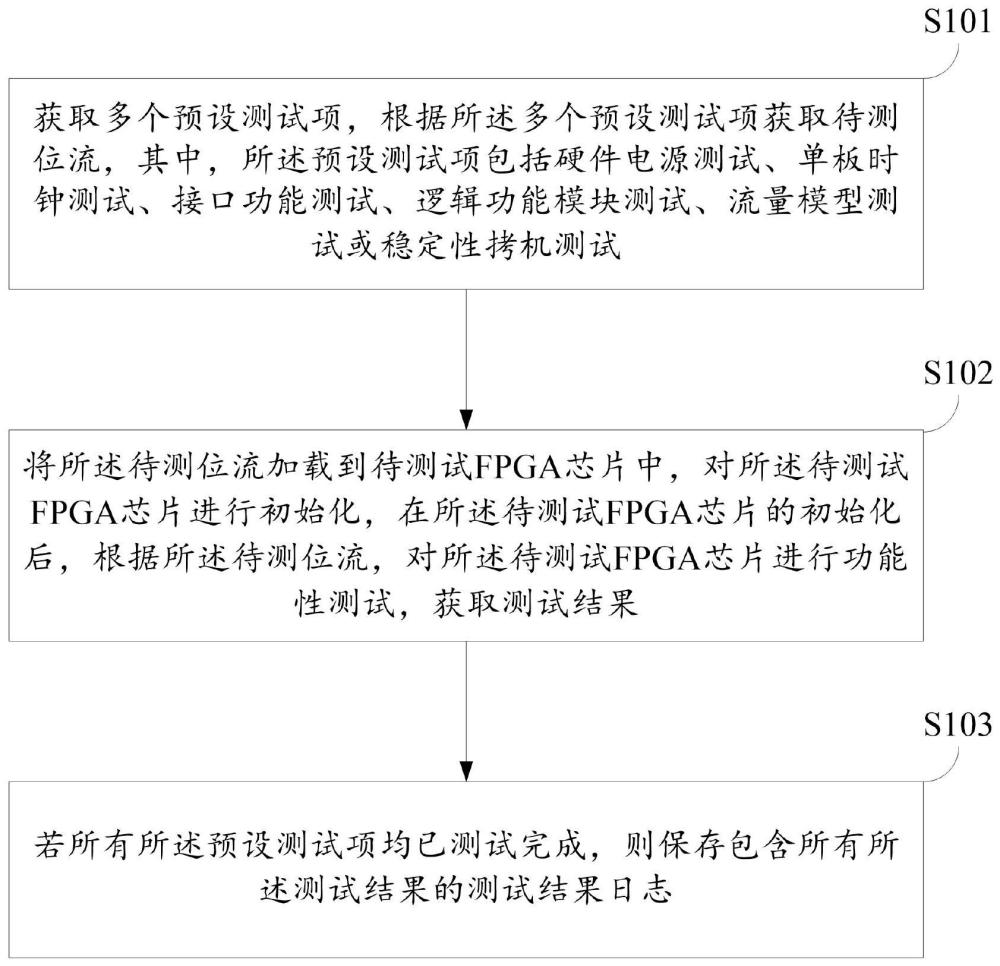

3、获取多个预设测试项,根据所述多个预设测试项获取待测位流,其中,所述预设测试项包括硬件电源测试、单板时钟测试、接口功能测试、逻辑功能模块测试、流量模型测试或稳定性拷机测试;

4、将所述待测位流加载到待测试fpga芯片中,对所述待测试fpga芯片进行初始化,在所述待测试fpga芯片的初始化后,根据所述待测位流,对所述待测试fpga芯片进行功能性测试,获取测试结果;

5、若所有所述预设测试项均已测试完成,则保存包含所有所述测试结果的测试结果日志。

6、进一步地,所述获取多个预设测试项,根据所述多个预设测试项获取待测位流,包括:

7、使上位机获取存储器中的多个预设测试项,并使所述上位机根据所述多个预设测试项从所述存储器中获取待测位流。

8、进一步地,使上位机获取存储器中的多个预设测试项之前,还包括,对所述上位机以及所述存储器进行初始化。

9、进一步地,将所述待测位流加载到待测试fpga芯片中,包括:使上位机通过配置总线将所述待测位流加载到待测试fpga芯片中。

10、进一步地,根据所述待测位流,对所述待测试fpga芯片进行功能性测试,获取测试结果,包括:根据所述待测位流对所述待测试fpga芯片进行功能性测试,使上位机通过控制总线获取测试结果,将所述测试结果存入至存储器中。

11、进一步地,根据所述多个预设测试项获取待测位流,包括:根据所述多个预设测试项获取测试硬件的位流、遍历接口功能的位流、验证逻辑功能的位流和验证统计信息的位流中的至少一个位流作为所述待测位流。

12、进一步地,根据所述待测位流,对所述待测试fpga芯片进行功能性测试,包括:

13、根据所述测试硬件的位流,对所述待测试fpga芯片进行硬件电源测试;根据所述遍历接口功能的位流,对所述待测试fpga芯片进行接口功能测试;根据所述验证逻辑功能的位流,对所述待测试fpga芯片进行逻辑功能模块测试;根据所述验证统计信息的位流,对所述待测试fpga芯片进行流量模型测试和/或稳定性拷机测试;根据所述测试硬件的位流、所述遍历接口功能的位流、所述验证逻辑功能的位流和所述验证统计信息的位流中的至少一个,对所述待测试fpga芯片进行单板时钟测试。

14、本发明的另一技术方案如下,还提供了一种fpga芯片测试装置,包括位流获取模块、测试模块以及存储模块;

15、所述位流获取模块,用于获取多个预设测试项,根据所述多个预设测试项获取待测位流,其中,所述预设测试项包括硬件电源测试、单板时钟测试、接口功能测试、逻辑功能模块测试、流量模型测试或稳定性拷机测试;

16、所述测试模块,用于将所述待测位流加载到待测试fpga芯片中,对所述待测试fpga芯片进行初始化,在所述待测试fpga芯片的初始化后,根据所述待测位流,对所述待测试fpga芯片进行功能性测试,获取测试结果;

17、所述存储模块,用于在所有所述预设测试项均已测试完成时,保存包含所有所述测试结果的测试结果日志。

18、本发明的另一技术方案如下,还提供了一种电子设备,包括存储器、处理器,所述存储器存储有可被所述处理器执行的计算机程序,所述处理器执行所述计算机程序时实现如上述任一项技术方案所述的fpga芯片测试方法。

19、本发明的另一技术方案如下,还提供了一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,所述计算机程序被处理器执行时实现如上述任一项技术方案所述的fpga芯片测试方法。

20、本发明的有益效果在于:通过获取多个预设测试项,根据所述多个预设测试项获取待测位流,其中,所述预设测试项包括硬件电源测试、单板时钟测试、接口功能测试、逻辑功能模块测试、流量模型测试或稳定性拷机测试;将所述待测位流加载到待测试fpga芯片中,对所述待测试fpga芯片进行初始化,在所述待测试fpga芯片的初始化后,根据所述待测位流,对所述待测试fpga芯片进行功能性测试,获取测试结果;若所有所述预设测试项均已测试完成,则保存包含所有所述测试结果的测试结果日志;通过上述技术方案,提高了fpga芯片的测试效率和测试覆盖率。

技术特征:

1.一种fpga芯片测试方法,其特征在于,包括:

2.根据权利要求1所述的fpga芯片测试方法,其特征在于,所述获取多个预设测试项,根据所述多个预设测试项获取待测位流,包括:

3.根据权利要求2所述的fpga芯片测试方法,其特征在于,使上位机获取存储器中的多个预设测试项之前,还包括,对所述上位机以及所述存储器进行初始化。

4.根据权利要求1所述的fpga芯片测试方法,其特征在于,将所述待测位流加载到待测试fpga芯片中,包括:使上位机通过配置总线将所述待测位流加载到待测试fpga芯片中。

5.根据权利要求1所述的fpga芯片测试方法,其特征在于,根据所述待测位流,对所述待测试fpga芯片进行功能性测试,获取测试结果,包括:根据所述待测位流对所述待测试fpga芯片进行功能性测试,使上位机通过控制总线获取测试结果,将所述测试结果存入至存储器中。

6.根据权利要求1所述的fpga芯片测试方法,其特征在于,根据所述多个预设测试项获取待测位流,包括:根据所述多个预设测试项获取测试硬件的位流、遍历接口功能的位流、验证逻辑功能的位流和验证统计信息的位流中的至少一个位流作为所述待测位流。

7.根据权利要求6所述的fpga芯片测试方法,其特征在于,根据所述待测位流,对所述待测试fpga芯片进行功能性测试,包括:

8.一种fpga芯片测试装置,其特征在于,包括位流获取模块、测试模块以及存储模块;

9.一种电子设备,包括存储器、处理器,所述存储器存储有可被所述处理器执行的计算机程序,其特征在于,所述处理器执行所述计算机程序时实现如权利要求1至7任一项所述的fpga芯片测试方法。

10.一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现如权利要求1至7任一项所述的fpga芯片测试方法。

技术总结

本发明提供了一种FPGA芯片测试方法、装置、电子设备及存储介质。本发明提供的FPGA芯片测试方法,包括:获取多个预设测试项,根据所述多个预设测试项获取待测位流,其中,所述预设测试项包括硬件电源测试、单板时钟测试、接口功能测试、逻辑功能模块测试、流量模型测试或稳定性拷机测试;将所述待测位流加载到待测试FPGA芯片中,对所述待测试FPGA芯片进行初始化,在所述待测试FPGA芯片的初始化后,根据所述待测位流,对所述待测试FPGA芯片进行功能性测试,获取测试结果;若所有所述预设测试项均已测试完成,则保存包含所有所述测试结果的测试结果日志。本发明提供的FPGA芯片测试方法,提高了FPGA芯片的测试效率和测试覆盖率。

技术研发人员:李庭权,何波

受保护的技术使用者:深圳市紫光同创电子有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!