一种延时测试电路、信号线路径延迟的测量方法及装置与流程

本发明涉及电路控制,具体涉及一种信号线路径延迟的测量方法及装置。

背景技术:

1、自动化测试设备(automatic test equipment,ate)在进行测试时连出大量的信号线,用于连接到被测器件(device under test,dut)上进行测试,由于不同用户的dut芯片千差万别,因此都是由用户自己设计一个线路板,将ate的信号线连接到dut上,板上的信号线的长度对于ate来说是未知的,但是ate又必须知道信号线上产生的路径延时,否则测试时,信号由于附加了一段未知的路径延时,测试很可能会出错。

2、然而,上述的延时值不仅包含了连接至dut板上信号线的延时值还包括了dut板自身的延时值,需要测量得到dut板自身的延时值后,才能真正的得到ate信号线的延时值,测量并不方便且还需要设计dut板。

技术实现思路

1、有鉴于此,本发明实施例提供了一种信号线路径延迟的测量方法及装置,以此解决现有技术中ate信号线路的路径延时测量不方便且成本较高的问题。

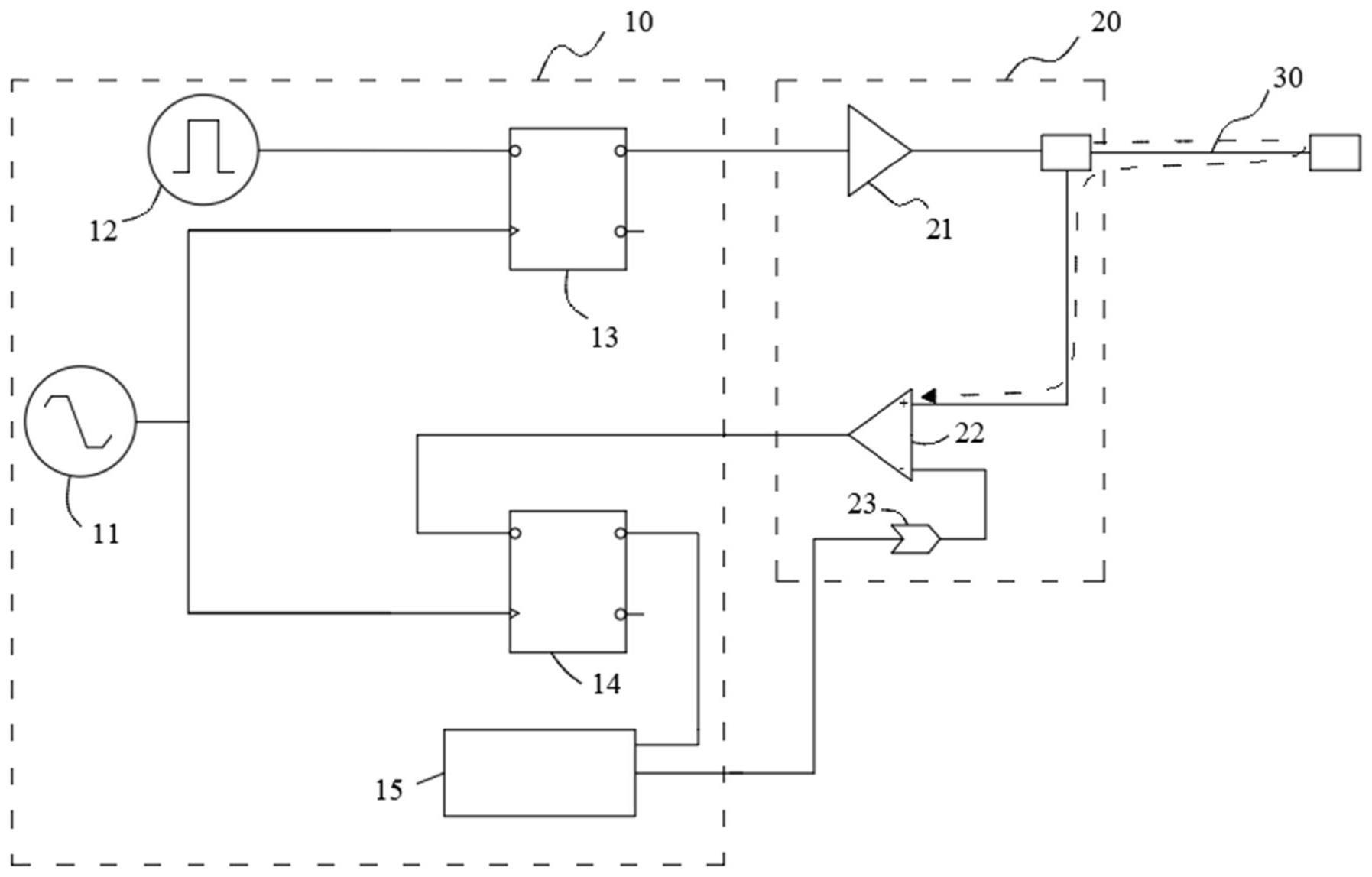

2、根据第一方面,本发明实施例提供了一种延时测试电路,包括:

3、集成在自动测试设备中的现场可编程门阵列芯片以及管脚电路芯片;

4、所述现场可编程门阵列芯片包括时钟信号发生器、脉冲信号发生器、脉冲发送触发器、结果采样触发器以及处理逻辑器,所述时钟信号发生器的输出端与所述脉冲发送触发器、所述结果采样触发器的输入端电性连接,所述脉冲信号发生器的输出端与所述脉冲发送触发器的输入端电性连接,所述处理逻辑器与所述结果采样触发器电性连接;

5、所述管脚电路芯片包括驱动器、比较器、数模转换器和连接端口,所述驱动器的输入端与所述脉冲发送触发器的输出端电性连接,所述驱动器的输出端与所述连接端口电性连接,所述连接端口与所述比较器的其中一个输入端电性连接,所述比较器的另一个输入端与所述数模转换器的输出端电性连接,所述比较器的输出端与所述结果采样触发器的输入端连接,所述处理逻辑器与所述数模转换器电性连接。

6、结合第一方面,在第一方面第一实施方式中,所述时钟信号发生器与所述结果采样触发器之间设有延时器,延时器与处理逻辑器电性连接。

7、结合第一方面,在第一方面第二实施方式中,所述脉冲信号发生器与所述脉冲发送触发器之间设有延时器,延时器与处理逻辑器电性连接。

8、结合第一方面,在第一方面第三实施方式中,所述比较器与所述结果采样触发器之间设有延时器,延时器与处理逻辑器电性连接。

9、结合第一方面,在第一方面第四实施方式中,所述时钟信号发生器与所述结果采样触发器之间、所述脉冲信号发生器与所述脉冲发送触发器之间、所述比较器与所述结果采样触发器之间的其中至少一处设有延时器,延时器与处理逻辑器电性连接。

10、根据第二方面,本发明实施例还提供了一种信号线路径延迟的测量方法,所述方法包括以下步骤:

11、将被测信号线连接至所述管脚电路芯片的所述连接端口;

12、所述时钟信号发生器按照预设时钟频率发送时钟信号以及所述脉冲信号发生器按照预设脉冲参数发送脉冲信号,通过所述管脚电路芯片的所述触发器向所述被测信号线发送所述脉冲信号;

13、利用时域反射技术,通过所述管脚电路芯片的所述比较器接收所述被测信号线返回的反射信号;所述处理逻辑器通过所述数模转换器控制所述比较器的比较门限,以对所述反射信号进行切片;

14、通过所述结果采样触发器对返回信号进行采样记录;所述采样记录时对采样时刻和/或脉冲输出时刻进行延时处理;

15、基于所述采样记录的结果,确定所述被测信号线的延时值以及连接质量。

16、结合第二方面,在第二方面第一实施方式中,所述通过所述结果采样触发器对返回信号进行采样记录,具体包括:

17、对时钟信号、所述脉冲信号、所述比较器返回的所述反射信号中的其中至少一种信号进行延时,通过所述结果采样触发器对返回信号进行采样记录。

18、结合第二方面第一实施方式,在第二方面第二实施方式中,通过所述延时器对时钟信号、所述脉冲信号、所述比较器返回的所述反射信号中的其中至少一种信号进行延时,所述延时器设置在所述现场可编程门阵列芯片内,所述延时器与所述处理逻辑器电性连接。

19、结合第二方面,在第二方面第三实施方式中,在所述比较器接收反射信号时通过所述处理逻辑器调整所述数模转换器的比较门限,所述比较门限的比较值位于预设比较范围内。

20、根据第二方面,本发明实施例还提供了一种信号线路径延迟的测量装置,所述装置包括:

21、第一测量模块,用于将被测信号线连接至所述管脚电路芯片的所述连接端口;

22、第二测量模块,用于所述时钟信号发生器按照预设时钟频率发送时钟信号以及所述脉冲信号发生器按照预设脉冲参数发送脉冲信号,通过所述管脚电路芯片的所述触发器向所述被测信号线发送所述脉冲信号;

23、第三测量模块,用于利用时域反射技术,通过所述管脚电路芯片的所述比较器接收所述被测信号线返回的反射信号;所述处理逻辑器通过所述数模转换器控制所述比较器的比较门限,以对所述反射信号进行切片;

24、第四测量模块,用于通过所述结果采样触发器对返回信号进行采样记录;所述采样记录时对采样时刻和/或脉冲输出时刻进行延时处理;

25、第五测量模块,用于基于所述采样记录的结果,确定所述被测信号线的延时值以及连接质量。

26、本发明的延时测试电路、信号线路径延迟的测量方法及装置,通过在集成至ate的现场可编程门阵列芯片设置时钟信号发生器、脉冲信号发生器、脉冲发送触发器、结果采样触发器以及处理逻辑器,且时钟信号发生器的输出端与脉冲发送触发器、结果采样触发器的输入端电性连接,脉冲信号发生器的输出端与脉冲发送触发器的输入端电性连接,处理逻辑器与结果采样触发器电性连接,同时,为集成至ate的管脚电路芯片设置驱动器、比较器、数模转换器和连接端口,驱动器的输入端与脉冲发送触发器的输出端电性连接,驱动器的输出端与连接端口电性连接,连接端口与比较器的其中一个输入端电性连接,比较器的另一个输入端与数模转换器的输出端电性连接,比较器的输出端与结果采样触发器的输入端连接,处理逻辑器与数模转换器电性连接,使得ate的在不增加ate硬件电路的情况下可以对信号线进行精细的tdr测量,不仅可以得出用户附加的dut板的路径延时,也可检查信号线整个路径上的连接质量,实现仅利用ate上现有的fpga和pe电路,进行路径延时的tdr测量。

技术特征:

1.一种延时测试电路,其特征在于,包括:

2.根据权利要求1所述的延时测试电路,其特征在于,所述时钟信号发生器与所述结果采样触发器之间设有延时器,延时器与处理逻辑器电性连接。

3.根据权利要求1所述的延时测试电路,其特征在于,所述脉冲信号发生器与所述脉冲发送触发器之间设有延时器,延时器与处理逻辑器电性连接。

4.根据权利要求1所述的延时测试电路,其特征在于,所述比较器与所述结果采样触发器之间设有延时器,延时器与处理逻辑器电性连接。

5.根据权利要求1所述的延时测试电路,其特征在于,所述时钟信号发生器与所述结果采样触发器之间、所述脉冲信号发生器与所述脉冲发送触发器之间、所述比较器与所述结果采样触发器之间的其中至少一处设有延时器,延时器与处理逻辑器电性连接。

6.一种基于权利要求1所述的延时测试电路实现的信号线路径延迟的测量方法,其特征在于,所述方法包括以下步骤:

7.根据权利要求6所述的信号线路径延迟的测量方法,其特征在于,所述通过所述结果采样触发器对返回信号进行采样记录,具体包括:

8.根据权利要求7所述的信号线路径延迟的测量方法,其特征在于,通过所述延时器对时钟信号、所述脉冲信号、所述比较器返回的所述反射信号中的其中至少一种信号进行延时,所述延时器设置在所述现场可编程门阵列芯片内,所述延时器与所述处理逻辑器电性连接。

9.根据权利要求6所述的信号线路径延迟的测量方法,其特征在于,在所述比较器接收反射信号时通过所述处理逻辑器调整所述数模转换器的比较门限,所述比较门限的比较值位于预设比较范围内。

10.一种基于权利要求1所述的延时测试电路实现的信号线路径延迟的测量装置,其特征在于,所述装置包括:

技术总结

本发明公开了一种延时测试电路、信号线路径延迟的测量方法及装置,涉及电路控制技术领域,该方法包括:时钟信号发生器按照预设时钟频率发送时钟信号以及脉冲信号发生器按照预设脉冲参数发送脉冲信号,通过管脚电路芯片的触发器向被测信号线发送脉冲信号;利用时域反射技术,通过管脚电路芯片的比较器接收被测信号线返回的反射信号;通过结果采样触发器对返回信号进行采样记录;采样记录时对采样时刻和/或脉冲输出时刻进行延时处理;基于采样记录的结果,确定被测信号线的延时值以及连接质量。本发明在不增加ATE硬件电路的情况下可以对信号线进行精细的TDR测量,不仅可以得出用户附加的DUT板的路径延时,也可检查信号线整个路径上的连接质量。

技术研发人员:陈立元

受保护的技术使用者:杭州至千哩科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!