一种光强检测电路及检测方法与流程

本发明涉及信息安全芯片,具体为一种光强检测电路及检测方法。

背景技术:

1、安全芯片在信息社会的各个领域中应用越来越广泛,其主要功能包括对关键数据的安全存储、加密、解密以及身份识别等,安全芯片除了面临来自反向工程、探针探测等侵入式攻击的威胁,还易受光分析等半侵入式攻击,在安全芯片应用场合,需要监测电路所处的可见光环境下光强是否在安全范围内,可配置为引起安全芯片系统复位,防止在异常可见光照下的攻击行为。

2、现有技术实现方案,利用感光二极管受光照后产生光生电流,通过电流/电压转换电路将光生电流转换为光生电压,利用比较模块将光生电压与一基准电压比较后,输出报警信号light_detect,电流/电压转换电路实现方案之一为感光二极管的寄生电容,当有光照发生时,光生电流对感光二极管的寄生电容充电,产生光生电压vsen_ld,当光生电压vsen_ld超过参考电压vref_ld时,输出报警信号。

3、但是,传统的光强检测电路存在以下缺点:

4、(1)传统的光强检测电路检测精度较低,感光元件上残留的电荷会影响检测结果;

5、(2)传统的光强检测电路检测光强阈值不方便调节。

技术实现思路

1、本发明的目的在于提供一种光强检测电路及检测方法,以解决上述背景技术中提出的传统的光强检测电路检测精度较低,感光元件上残留的电荷会影响检测结果;传统的光强检测电路检测光强阈值不方便调节的问题。

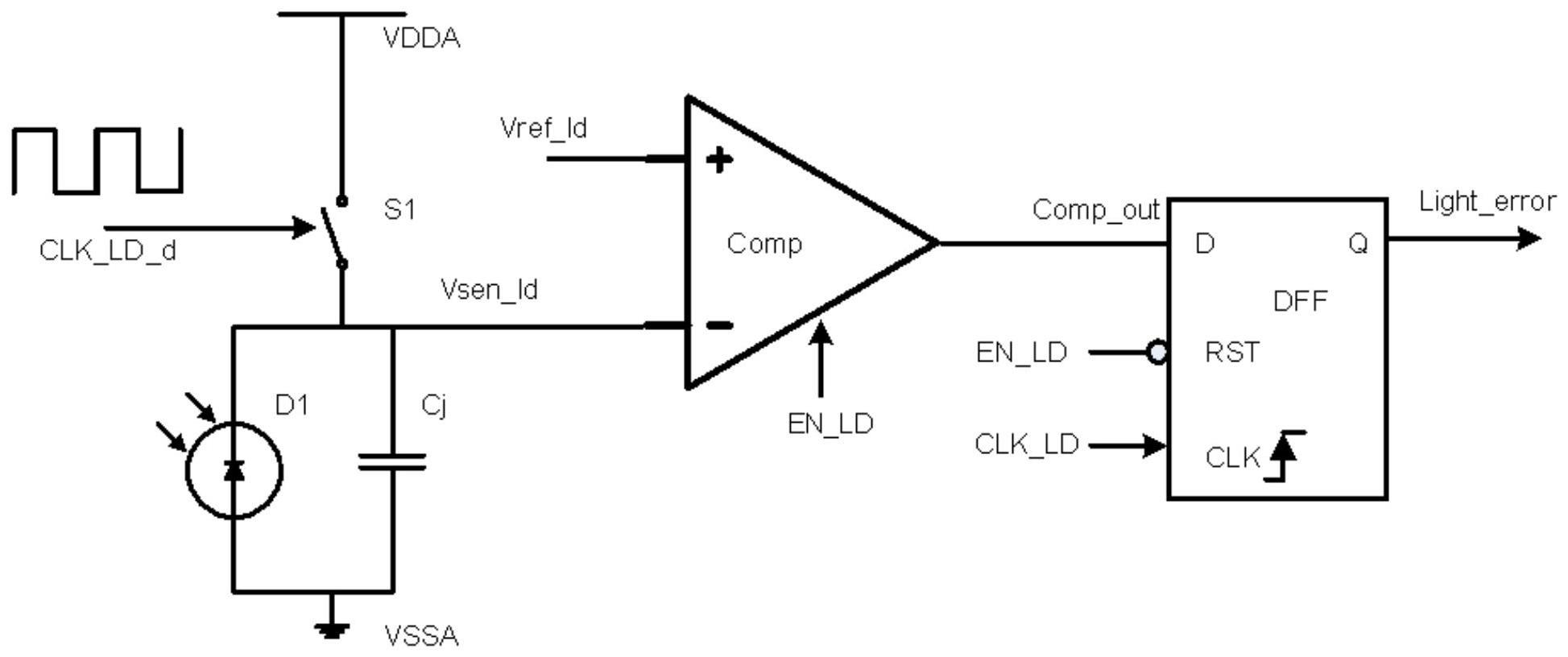

2、为实现上述目的,本发明提供如下技术方案:一种光强检测电路,包括电压比较器comp,所述电压比较器comp的正极通过导线连接有参考电压vref_ld,所述电压比较器comp的负极通过导线连接有反偏电压vsen_ld,所述反偏电压vsen_ld的一个端脚通过导线分别连接有开关s1和电容cj,所述电容cj的一个端脚通过导线连接有感光二极管d1,所述感光二极管d1远离电容cj的一个端脚和电容cj远离d1的一个端脚均通过导线连接有vssa,所述开关s1的一个端脚通过导线连接有clk_ld_d,所述开关s1的另一个端脚通过导线连接有电源电压vdda,所述电压比较器comp安装于检测芯片内部,所述电压比较器comp的一个端脚通过导线连接有电压比较器comp_out,所述电压比较器comp_out远离电压比较器comp的一端通过导线与d端脚正对的一侧连接,所述q端脚的一端通过导线连接有light_error,所述rst端脚通过导线连接有en_ld,所述clk端脚通过导线连接有clk_ld,所述en_ld的一侧通过导线与电压比较器comp正对的一侧连接。

3、作为本发明的一种优选技术方案,所述en_ld为总使能信号,高电平使能。

4、作为本发明的一种优选技术方案,所述clk_ld_d为时钟clk_ld经约5ns延时后的时钟信号。

5、作为本发明的一种优选技术方案,所述开关s1和电容cj构成动态上拉电路和放电电路。

6、作为本发明的一种优选技术方案,所述d端脚为触发端脚。

7、本发明一种光强检测电路的检测方法,包括以下步骤:

8、步骤一、上拉状态设定:当clk_ld_d为高电平时,开关s1闭合,反偏电压vsen_ld被上拉到电源电压vdda,感光二极管d1被反向偏置,由于反偏电压vsen_ld=电源电压vdda,高于参考电压vref_ld,所以比较器输出为低电平;

9、步骤二、感光状态设定:当clk_ld_d为低电平时,开关s1断开,当有光照发生时,反向光生电流对寄生结电容放电,从而导致反偏电压vsen_ld下降,下降时间为0.5/clk_ld_d,即时钟低电平的长度为0.5t_ld;

10、步骤三、电路检测:反偏电压vsen_ld和参考电压vref_ld通过电压比较器comp比较后经dff采样输出检测结果light_error。

11、作为本发明的一种优选技术方案,所述步骤三中检测的具体内容为:第一种情况,光生电流足够强,则会使反偏电压vsen_ld小于参考电压vref_ld,比较器输出为高,引发报警信号;第二种情况,光生电流比较微弱,在0.5t_ld这段时间内,反偏电压vsen_ld大于参考电压vref_ld,比较器输出经dff采样输出保持原来低的状态,不会引发报警;利用d触发器dff作为输出采样电路,当en_ld为低电平时,dff复位,光强检测输出light_error为低电平,当en_ld为高电平,且clk_ld上升沿,电压比较器comp_out信号经输出采样电路输出。

12、与现有技术相比,本发明的有益效果是:

13、1、利用时钟的高电平期间将感光二极管的负极电压vsen_ld上拉到电源电压及感光二极管的正极接地,并输入到电压比较器comp的负端,与一基准电压vref_ld进行比较,输出电压比较器比较结果comp_out为低电平,经采样输出电路输出低电平信号light_error;利用时钟的低电平期间,当感光二极管受到光照时,产生光生电流,感光二极管上寄生电容上的光生电压vsen_ld由于光生电流的作用缓慢放电,当vsen_ld小于vref_ld,电压比较器输出comp_out为高电平,经采样输出电路输出高电平报警信号light_error;

14、2、通过调节时钟频率,任意调节感光二极管的光强检测阈值,时钟高电平期间动态拉高感光二极管的负极电压vsen_ld到电源电压,利用时钟低电平期间光生电流放电机制检测光强,大幅提高了光强检测的可靠性;

15、3、采用时钟的高电平期间将感光二极管的负极电压vsen_ld上拉到电源电压及感光二极管的正极接地,大幅提高了光强检测的可靠性;

16、4、利用时钟的低电平期间,当感光二极管受到光照时,产生光生电流,感光二极管上寄生电容上的光生电压(vsen_ld)由于光生电流的作用缓慢放电,当放电到阈值以下时,输出报警信号;

17、5、通过调节时钟频率,即可任意调节光强检测阈值,检测结果经d触发器采样输出,进一步提高了光强检测的可靠性。

技术特征:

1.一种光强检测电路,包括电压比较器comp,其特征在于:所述电压比较器comp的正极通过导线连接有参考电压vref_ld,所述电压比较器comp的负极通过导线连接有反偏电压vsen_ld,所述反偏电压vsen_ld的一个端脚通过导线分别连接有开关s1和电容cj,所述电容cj的一个端脚通过导线连接有感光二极管d1,所述感光二极管d1远离电容cj的一个端脚和电容cj远离d1的一个端脚均通过导线连接有vssa,所述开关s1的一个端脚通过导线连接有clk_ld_d,所述开关s1的另一个端脚通过导线连接有电源电压vdda,所述电压比较器comp安装于检测芯片内,所述检测芯片内设有d端脚、q端脚、rst端脚、clk端脚和dff端脚,所述电压比较器comp的一个端脚通过导线连接有电压比较器comp_out,所述电压比较器comp_out远离电压比较器comp的一端通过导线与d端脚正对的一侧连接,所述q端脚的一端通过导线连接有light_error,所述rst端脚通过导线连接有en_ld,所述clk端脚通过导线连接有clk_ld,所述en_ld的一侧通过导线与电压比较器comp正对的一侧连接。

2.根据权利要求1所述的一种光强检测电路,其特征在于:所述en_ld为总使能信号,高电平使能。

3.根据权利要求1所述的一种光强检测电路,其特征在于:所述clk_ld_d为时钟clk_ld经约5ns延时后的时钟信号。

4.根据权利要求1所述的一种光强检测电路,其特征在于:所述开关s1和电容cj构成动态上拉电路和放电电路。

5.根据权利要求1所述的一种光强检测电路,其特征在于:所述d端脚为触发端脚。

6.根据权利要求1-5任一所述的一种光强检测电路的检测方法,其特征在于,包括以下步骤:

7.根据权利要求6所述的一种光强检测电路及检测方法,其特征在于:所述步骤三中检测的具体内容为:第一种情况,光生电流足够强,则会使反偏电压vsen_ld小于参考电压vref_ld,比较器输出为高,引发报警信号;第二种情况,光生电流比较微弱,在0.5t_ld这段时间内,反偏电压vsen_ld大于参考电压vref_ld,比较器输出经dff采样输出保持原来低的状态,不会引发报警;利用d触发器dff作为输出采样电路,当en_ld为低电平时,dff复位,光强检测输出light_error为低电平,当en_ld为高电平,且clk_ld上升沿,电压比较器comp_out信号经输出采样电路输出。

技术总结

本发明公开了一种光强检测电路及检测方法,包括电压比较器Comp,电压比较器Comp的正极通过导线连接有参考电压Vref_ld,电压比较器Comp的负极通过导线连接有反偏电压Vsen_ld,本发明利用时钟的高电平期间将感光二极管的负极电压Vsen_ld上拉到电源电压及感光二极管的正极接地,并输入到电压比较器Comp的负端,与一基准电压Vref_ld进行比较,输出电压比较器比较结果Comp_out,经采样输出电路输出光强检测信号Light_error;利用时钟的低电平期间,通过调节时钟频率,任意调节感光二极管的光强检测阈值,时钟高电平期间动态拉高感光二极管的负极电压Vsen_ld到电源电压,利用时钟低电平期间光生电流放电机制检测光强,大幅提高了光强检测的可靠性。

技术研发人员:张景,赵志凤,刘义,刘宝生,高丕涛

受保护的技术使用者:中云信安(深圳)科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!