一种测量FPGA芯片内部电压降的方法、装置和系统与流程

本发明属于电路失效分析领域,具体涉及一种测量fpga芯片内部电压降的方法、装置和系统。

背景技术:

1、在集成电路进入深亚微米制造阶段,芯片内部连接线的线宽越来越细,导致连线上的电阻随之上升。这种效应在芯片内部供电电路上累积,使得芯片内部电源网络的供电电压比预期的值偏低,从而拉低了整个电路的性能,严重时,芯片失效。

2、在现代集成电路的设计过程中,预防电压降是设计收敛的一个重要目标。电压降(ir-drop)一般分为两种类型:静态电压降,即晶体管漏电流(leakage)导致的电压降;动态电压降,即由于芯片内部大量晶体管同时开启或闭合,瞬态电流导致的电压降。预防电压降的通用办法中,一种是仿真来模拟实际电路的工作状况,分析电压降的影响;另一种是通过专用软件来分析电压降的风险;再一种是采用特殊的设计规则来设计供电网络(如图1所示的简化供电电路等)。然而,芯片一旦制造完成,所有的金属层都封装在管壳内部,缺乏实际的手段来测量电压降的影响。一旦遇到芯片工作异常,很难排查定位电压降导致的故障。

3、现有技术一般是通过以下方法来排查电压降故障:

4、1.从芯片内部引出电源线到引脚,直接测量;但引出电源线的方法相当昂贵,芯片的引脚是有限的,只能引出有限点位的电源信号;采用打开管壳,通过探针来探测电压的方式,既需要昂贵的设备,也无法在实际工况下测试。

5、2.给芯片抬高或降低外部供电电压,观察芯片的性能变化;但通过抬高或降低电压的方法只能粗略估计电压降的大致影响。

6、3.通过软件仿真来分析电压降的影响;但软件仿真依赖于测试条件的设置,往往无法反映真实的工作状况。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种测量fpga芯片内部电压降的方法、装置和系统。本发明要解决的技术问题通过以下技术方案实现:

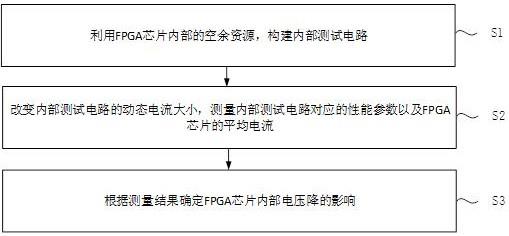

2、第一方面,本发明实施例提供了一种测量fpga芯片内部电压降的方法,所述方法包括:

3、利用fpga芯片内部的空余资源,构建内部测试电路;

4、改变所述内部测试电路的动态电流大小,测量内部测试电路对应的性能参数以及fpga芯片的平均电流;

5、根据测量结果确定fpga芯片内部电压降的影响。

6、在本发明的一个实施例中,所述利用fpga芯片内部的空余资源,构建内部测试电路,包括:

7、对fpga芯片的电路图进行分析,标记出未使用的内部空余资源;

8、将标记出的未使用的内部空余资源利用链式方法进行连接,以构建类似移位寄存器的方式构建内部测试电路。

9、在本发明的一个实施例中,未使用的内部空余资源,包括:

10、可配置逻辑功能块、可配置块状存储器、可配置数字信号处理单元,以及可配置时钟管理模块。

11、在本发明的一个实施例中,所述利用fpga芯片内部的空余资源,构建内部测试电路,利用预设的测试电路生成软件完成。

12、在本发明的一个实施例中,所述改变所述内部测试电路的动态电流大小,包括:

13、通过改变fpga芯片外部的可调节时钟信号发生器的频率,改变所述内部测试电路的动态电流大小。

14、在本发明的一个实施例中,内部测试电路的性能参数,包括:

15、最高工作频率、延迟。

16、在本发明的一个实施例中,测量fpga芯片的平均电流,利用fpga芯片供电电路上接入的电流计实现。

17、在本发明的一个实施例中,所述根据测量结果确定fpga芯片内部电压降的影响,包括:

18、绘制fpga芯片的平均电流和内部测试电路性能参数的对应曲线,根据所述对应曲线推测fpga芯片内部电压降的数值。

19、第二方面,本发明实施例提供了一种测量fpga芯片内部电压降的装置,所述装置包括:

20、内部测试电路构建模块,用于利用fpga芯片内部的空余资源,构建内部测试电路;

21、测量模块,用于改变所述内部测试电路的动态电流大小,测量内部测试电路对应的性能参数以及fpga芯片的平均电流;

22、电压降影响确定模块,用于根据测量结果确定fpga芯片内部电压降的影响。

23、第三方面,本发明实施例提供了一种测量fpga芯片内部电压降的系统,所述系统包括:

24、fpga芯片、外部供电电源、可调节时钟信号发生器、电流计和测试电路生成软件;其中,所述外部供电电源用于为所述fpga芯片供电;所述可调节时钟信号发生器的输出与所述fpga芯片的特定管脚连接;所述电流计接入在所述fpga芯片的供电电路上;

25、所述系统用于,利用fpga芯片内部的空余资源和所述测试电路生成软件,构建内部测试电路;通过改变所述可调节时钟信号发生器的频率,改变内部测试电路的动态电流大小,测量内部测试电路对应的性能参数,以及利用电流计测量fpga芯片的平均电流;根据测量结果确定fpga芯片内部电压降的影响。

26、本发明的有益效果:

27、本发明实施例所提供的测量fpga芯片内部电压降的方法,利用fpga芯片内部的空余资源,构建内部测试电路;改变所述内部测试电路的动态电流大小,测量内部测试电路对应的性能参数以及fpga芯片的平均电流;根据测量结果确定fpga芯片内部电压降的影响。可见,本发明实施例是利用fpga芯片内部未被使用的资源,在芯片内部实现一个可以调节大小的电流源,通过改变芯片内部电流的大小评估电压降的影响。本发明实施例既不需要芯片提供额外的引脚,也不需要昂贵的测试设备,直接利用内部资源评估fpga内部的电压降,能够在真实工作条件下测量电压降的影响,且提供电压降测量方式的准确性更高,由于这种方法可以直接施加大电流作用在芯片内部供电线路上,而仿真也需要实际测量校正才能保证正确性,因此本方法可以帮助芯片设计人员高效简单地进行问题分析和定位。

技术特征:

1.一种测量fpga芯片内部电压降的方法,其特征在于,包括:

2.根据权利要求1所述的测量fpga芯片内部电压降的方法,其特征在于,所述利用fpga芯片内部的空余资源,构建内部测试电路,包括:

3.根据权利要求2所述的测量fpga芯片内部电压降的方法,其特征在于,未使用的内部空余资源,包括:

4.根据权利要求3所述的测量fpga芯片内部电压降的方法,其特征在于,所述利用fpga芯片内部的空余资源,构建内部测试电路,利用预设的测试电路生成软件完成。

5.根据权利要求1-4任一项所述的测量fpga芯片内部电压降的方法,其特征在于,所述改变所述内部测试电路的动态电流大小,包括:

6.根据权利要求5所述的测量fpga芯片内部电压降的方法,其特征在于,内部测试电路的性能参数,包括:

7.根据权利要求1所述的测量fpga芯片内部电压降的方法,其特征在于,测量fpga芯片的平均电流,利用fpga芯片供电电路上接入的电流计实现。

8.根据权利要求1所述的测量fpga芯片内部电压降的方法,其特征在于,所述根据测量结果确定fpga芯片内部电压降的影响,包括:

9.一种测量fpga芯片内部电压降的装置,其特征在于,包括:

10.一种测量fpga芯片内部电压降的系统,其特征在于,包括:

技术总结

本发明公开了一种测量FPGA芯片内部电压降的方法、装置和系统,方法包括:利用FPGA芯片内部的空余资源,构建内部测试电路;改变内部测试电路的动态电流大小,测量内部测试电路对应的性能参数以及FPGA芯片的平均电流;根据测量结果确定FPGA芯片内部电压降的影响。本发明既不需要芯片提供额外的引脚,也不需要昂贵的测试设备,直接利用内部资源评估FPGA内部的电压降,能够在真实工作条件下测量电压降的影响,且提供电压降测量方式的准确性更高,因此可以帮助芯片设计人员高效简单地进行问题分析和定位。

技术研发人员:杨龙,贾弘翊,韦嶔,张红荣

受保护的技术使用者:西安智多晶微电子有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!