超导量子干涉装置的电阻测试方法及量子芯片与流程

本申请属于量子领域,特别是一种超导量子干涉装置的电阻测试方法及量子芯片。

背景技术:

1、超导量子芯片上的关键结构是超导量子比特,超导量子比特的关键结构是约瑟夫森结;将由约瑟夫森结并联形成的超导量子干涉装置(squid),与额外构建的电容极板并联,基于该并联结构形成的超导量子比特电路即作为量子芯片上执行量子计算的基本单元——超导量子比特。为了保证超导量子芯片的性能,就必须严格控制超导量子比特的频率参数,超导量子比特的常温电阻表征是反应频率参数的重要信息,而约瑟夫森结的电阻是超导量子比特的常温电阻表征的关键。

2、测试约瑟夫森结主要使用的是4探针或2探针扎入约瑟夫森结的两端,通过直流测试电流和电压来测试约瑟夫森结电阻以获得超导量子干涉装置的电阻。然而这种测试方法会破坏约瑟夫森结表面保护膜层,然后让测试仪器直接电连接约瑟夫森结进行性能参数测试,在测试后需要修复约瑟夫森结表面保护膜层以获得量子比特。整个过程中,增加了测试难度,降低了测试结果的可靠性,也对该超导约瑟夫森结所在的超导量子比特的完整性造成破坏,使其性能受到不可逆的影响,影响量子比特和量子芯片的生产效率。

技术实现思路

1、本申请的目的是提供一种超导量子干涉装置的电阻测试方法及量子芯片,解决了现有技术中测量超导量子干涉装置的电阻容易破坏物理结构的缺点,避免了对超导量子干涉装置的结构的破坏性。

2、本申请技术方案具体如下:

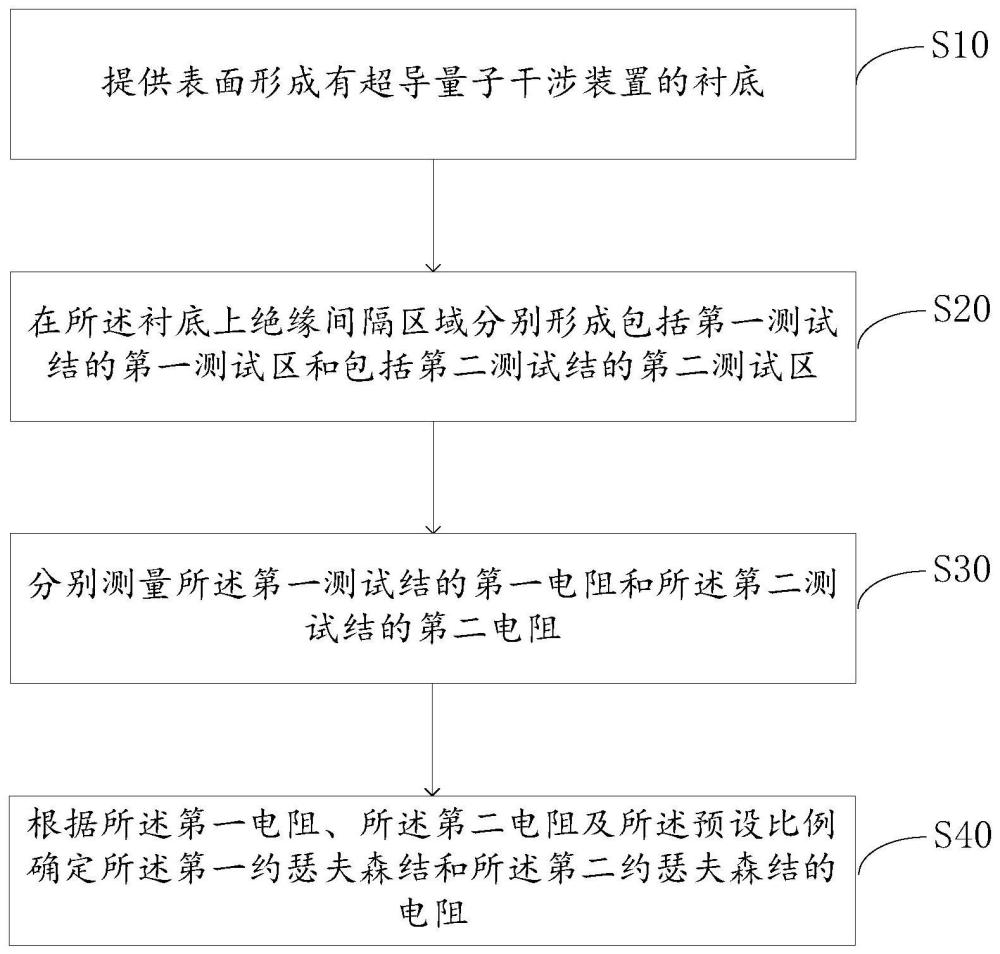

3、本申请一方面提供一种超导量子干涉装置的电阻测试方法,包括:

4、提供表面形成有超导量子干涉装置的衬底;其中,所述超导量子干涉装置包括结构面积非对称的第一约瑟夫森结和第二约瑟夫森结;

5、在所述衬底上绝缘间隔区域分别形成包括第一测试结的第一测试区和包括第二测试结的第二测试区;其中,所述第一测试结的尺寸与所述第一约瑟夫森结的尺寸按预设比例设置,且所述第二测试结的尺寸与所述第二约瑟夫森结的尺寸按预设比例设置;

6、分别测量所述第一测试结的第一电阻和所述第二测试结的第二电阻;

7、根据所述第一电阻、所述第二电阻及所述预设比例确定所述第一约瑟夫森结的电阻和所述第二约瑟夫森结的电阻。

8、如上所述的超导量子干涉装置的电阻测试方法,可选的,所述在所述衬底上绝缘间隔区域分别形成包括第一测试结的第一测试区和包括第二测试结的第二测试区,包括:

9、在所述衬底的外围形成包括第一测量触点和第二测量触点的第一测试区、及包括第三测量触点和第四测量触点的第二测试区;

10、在所述第一测量触点和所述第二测量触点之间形成第一测试结;

11、在所述第三测量触点和所述第四测量触点之间形成第二测试结。

12、如上所述的超导量子干涉装置的电阻测试方法,可选的,所述在所述衬底上绝缘间隔区域分别形成包括第一测试结的第一测试区和包括第二测试结的第二测试区,包括:

13、在所述衬底的外围形成包括第一测量触点的第一测试区、包括第二测量触点的第二测试区、及包括第三测量触点的第三测试区;

14、在所述第一测量触点和所述第二测量触点之间形成第一测试结;

15、在所述第一测量触点和所述第三测量触点之间形成第二测试结。

16、如上所述的超导量子干涉装置的电阻测试方法,可选的,所述第一约瑟夫森结的电阻大于所述第二约瑟夫森结的电阻,利用探针扎入所述第一测试结测量所述第一测试结的第一电阻的步骤,包括:

17、测量形成所述第一测试结之前的所述第一测量触点和所述第二测量触点的电阻值作为第三电阻;

18、依据所述第一电阻和所述第三电阻确定所述第一测试结的第四电阻。

19、如上所述的超导量子干涉装置的电阻测试方法,可选的,所述依据所述第一电阻和所述第三电阻确定所述第一测试结的第四电阻,包括:

20、依据所述第一电阻、所述第三电阻、及第一预设关系确定所述第四电阻;其中,所述第一预设关系表征所述第一电阻的导数为所述第三电阻的导数与所述第四电阻的导数的和。

21、如上所述的超导量子干涉装置的电阻测试方法,可选的,所述根据所述第一电阻、所述第二电阻及所述预设比例确定所述第一约瑟夫森结的电阻和所述第二约瑟夫森结的电阻,包括:

22、确定所述第四电阻与所述预设比例的商为所述第一约瑟夫森结的电阻;

23、确定所述第二电阻与所述预设比例的商为所述第二约瑟夫森结的电阻。

24、如上所述的超导量子干涉装置的电阻测试方法,可选的,所述根据所述第一电阻、所述第二电阻及所述预设比例确定所述第一约瑟夫森结的电阻和所述第二约瑟夫森结的电阻,包括:

25、确定所述第一电阻与所述预设比例的商为所述第一约瑟夫森结的电阻;

26、确定所述第二电阻与所述预设比例的商为所述第二约瑟夫森结的电阻。

27、如上所述的超导量子干涉装置的电阻测试方法,可选的,所述方法还包括:

28、分别测量所述第一测试结的第一面积、所述第一约瑟夫森结的第二面积、所述第二测试结的第三面积、所述第二约瑟夫森结的第四面积;

29、确定所述第一面积和所述第二面积的商为第一测量比例;

30、确定所述第三面积和所述第四面积的商为第二测量比例。

31、如上所述的超导量子干涉装置的电阻测试方法,可选的,所述根据所述第一电阻、所述第二电阻及所述预设比例确定所述第一约瑟夫森结的电阻和所述第二约瑟夫森结的电阻,包括:

32、依据所述第一测量比例和所述第二测量比例更新所述预设比例;

33、确定所述第一电阻与所述第一测量比例的商为所述第一约瑟夫森结的电阻;

34、确定所述第二电阻与所述第二测量比例的商为所述第二约瑟夫森结的电阻。

35、本申请另一方面提供一种量子芯片,所述量子芯片上集成若干个量子比特,每个量子比特均包括超导量子干涉装置和电容,所述超导量子干涉装置的电阻采用任一项上述的测试方法进行测量。

36、与现有技术相比,本申请具有以下有益效果:

37、本申请通过在衬底上绝缘间隔区域分别形成相互独立的包括第一测试结的第一测试区和包括第二测试结的第二测试区,避免测试时对量子比特电路造成影响;并分别对第一测试结的电阻和第二测试结的电阻进行测量,避免测量时测量探针直接扎入第一约瑟夫森结和第二约瑟夫森结的表面物理结构形成难以恢复的损坏,进而影响量子比特的性能;并结合测量结果和预设比例获得第一约瑟夫森结的电阻和第二约瑟夫森结的电阻,以实现对超导量子干涉装置中非对称的第一约瑟夫森结的电阻和第二约瑟夫森结的电阻的测量。

技术特征:

1.一种超导量子干涉装置的电阻测试方法,其特征在于,包括:

2.根据权利要求1所述的超导量子干涉装置的电阻测试方法,其特征在于,所述在所述衬底上绝缘间隔区域分别形成包括第一测试结的第一测试区和包括第二测试结的第二测试区,包括:

3.根据权利要求1所述的超导量子干涉装置的电阻测试方法,其特征在于,所述在所述衬底上绝缘间隔区域分别形成包括第一测试结的第一测试区和包括第二测试结的第二测试区,包括:

4.根据权利要求2或3所述的超导量子干涉装置的电阻测试方法,其特征在于,所述第一约瑟夫森结的电阻大于所述第二约瑟夫森结的电阻,利用探针扎入所述第一测试结测量所述第一测试结的第一电阻的步骤,包括:

5.根据权利要求4所述的超导量子干涉装置的电阻测试方法,其特征在于,所述依据所述第一电阻和所述第三电阻确定所述第一测试结的第四电阻,包括:

6.根据权利要求5所述的超导量子干涉装置的电阻测试方法,其特征在于,所述根据所述第一电阻、所述第二电阻及所述预设比例确定所述第一约瑟夫森结的电阻和所述第二约瑟夫森结的电阻,包括:

7.根据权利要求1所述的超导量子干涉装置的电阻测试方法,其特征在于,所述根据所述第一电阻、所述第二电阻及所述预设比例确定所述第一约瑟夫森结的电阻和所述第二约瑟夫森结的电阻,包括:

8.根据权利要求1所述的超导量子干涉装置的电阻测试方法,其特征在于,所述方法还包括:

9.根据权利要求8所述的超导量子干涉装置的电阻测试方法,其特征在于,所述根据所述第一电阻、所述第二电阻及所述预设比例确定所述第一约瑟夫森结的电阻和所述第二约瑟夫森结的电阻,包括:

10.一种量子芯片,其特征在于,所述量子芯片上集成若干个量子比特,每个量子比特均包括超导量子干涉装置和电容,所述超导量子干涉装置的电阻采用如权利要求1-9任一项所述的测试方法进行测量。

技术总结

本申请公开了一种超导量子干涉装置的电阻测试方法及量子芯片,所述测试方法包括:提供表面形成有超导量子干涉装置的衬底;在所述衬底上绝缘间隔区域分别形成包括第一测试结的第一测试区和包括第二测试结的第二测试区;利用探针扎入分别所述第一测试结和所述第二测试结测量所述第一测试结的第一电阻和所述第二测试结的第二电阻;根据所述第一电阻、所述第二电阻及所述预设比例确定所述第一约瑟夫森结的电阻和所述第二约瑟夫森结的电阻。本申请能在避免对超导量子干涉装置的结构的破坏性的情况下对非对称的约瑟夫森结的电阻进行测量。

技术研发人员:请求不公布姓名,请求不公布姓名,贾志龙

受保护的技术使用者:本源量子计算科技(合肥)股份有限公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!