一种针对芯片内部漏电失效进行EMMI定位的方法与流程

本发明属于芯片检测,涉及一种芯片内部漏电失效检测,尤其涉及采用emmi进行芯片内部漏电失效定位分析的方法。

背景技术:

1、集成电路在研制、生产和使用过程中失效不可避免,随着社会对产品质量和可靠性要求的不断提高,失效分析工作也显得越来越重要,通过芯片失效分析,可以帮助集成电路设计人员找到设计上的缺陷、工艺参数的不匹配或设计与操作中的不当等问题。

2、在芯片失效侦测定位的各种手段中,微光显微镜(也称为emmi)是一种效率较高的失效分析定位工具,emmi可侦测到半导体组件中电子-空穴对再结合时所发射出来的光线,侦测的波长在350nm-1100nm左右。emmi通过捕捉各种元件缺陷或异常所产生的漏电流可见光实现芯片失效点定位,目前已经广泛应用在侦测ic各种组件缺陷定位分析中。

3、因为给芯片内部漏电定位时常常需要上各种偏置电压来保证芯片的工作者状态。在这种情况下,就会出现很多和失效无关的芯片电路部分也有出现干扰亮点的情况,使得技术人员无法判断到底哪个亮点才是芯片的漏电点。

4、现有的技术方案,如中国专利申请cn111273164a、cn106646196a、cn103516340a,在面对芯片内部的漏电失效定位需要通过emmi(emission microscope,微光显微镜)分别定位好样品和失效样品在相同偏置条件下的失效亮点。两种样品的定位结果的差异亮点就是怀疑的失效点。

5、采用这种方法定位主要的缺点有:1,必须要一颗对比的好样品,在没有好样品,例如新产品研发失效的情况下,就需要研发人员花费大量的时间来一一分析繁多的失效亮点,耗时耗力且确定性不强;2,需要搭建两套系统并且分别需要对它们的亮点都进行放大留结果。可见,现有技术方案花费的时间成本和费用成本高昂。

技术实现思路

1、为解决现有技术中存在的不足,本发明提供了一种针对芯片内部漏电失效进行emmi定位的方法,以在没有好样品的情况下,仍然可以进行芯片失效定位分析。

2、本发明采用如下的技术方案。

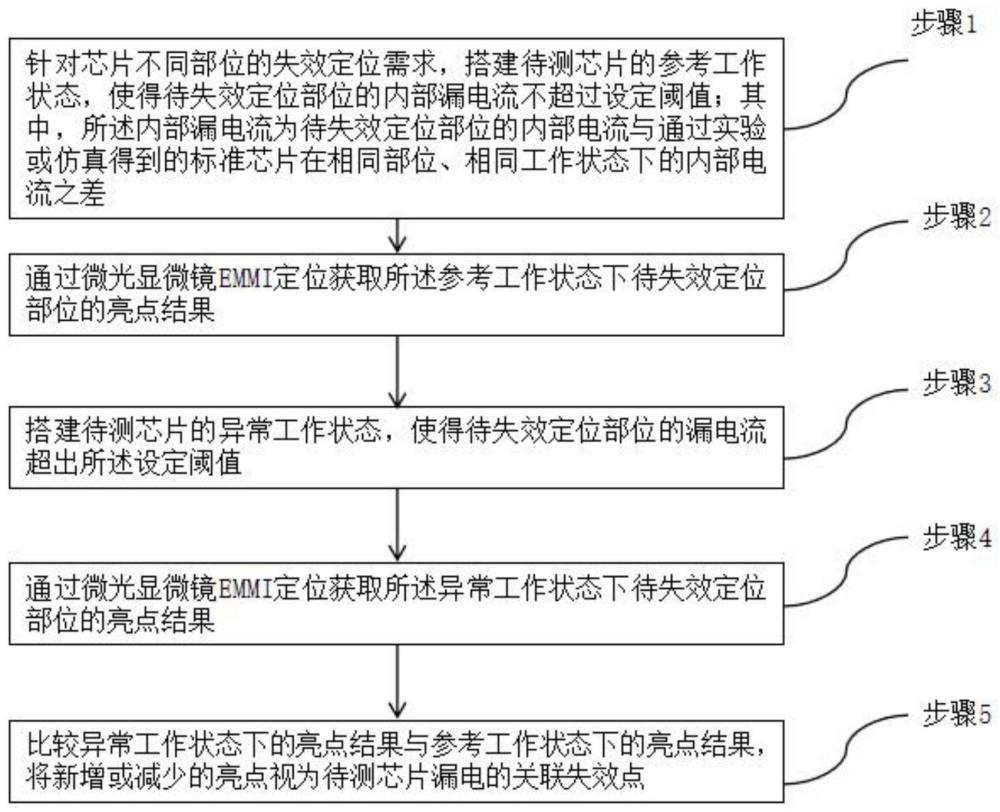

3、一种针对芯片内部漏电失效进行emmi定位的方法,所述方法包括以下步骤:

4、步骤1:针对芯片不同部位的失效定位需求,搭建待测芯片的参考工作状态,使得待失效定位部位的内部漏电流不超过设定阈值;其中,所述内部漏电流为待失效定位部位的内部电流与通过实验或仿真得到的标准芯片在相同部位、相同工作状态下的内部电流之差;

5、步骤2:通过微光显微镜emmi定位获取所述参考工作状态下待失效定位部位的亮点结果;

6、步骤3:搭建待测芯片的异常工作状态,使得待失效定位部位的漏电流超出所述设定阈值;

7、步骤4:通过微光显微镜emmi定位获取步骤3调整激励后待失效定位部位的亮点结果;

8、步骤5:比较步骤4得到的亮点结果与步骤2得到的亮点结果,将新增或减少的亮点视为待测芯片漏电的关联失效点。

9、进一步的,步骤5还包括:

10、如果步骤4得到的亮点结果与步骤2得到的亮点结果相比,不存在新增或减少的亮点,则重复步骤3-5,继续增加或减少激励,直到步骤4得到的亮点结果与步骤2得到的亮点结果相比,存在新增或减少的亮点,再将新增或减少的亮点确定为待测芯片漏电的关联失效点。

11、进一步的,在步骤1中,芯片不同部位的失效定位需求包括芯片本身的供电电源漏电失效定位和芯片io口漏电失效定位。

12、进一步的,步骤1还包括:针对芯片本身的供电电源漏电失效定位,通过将待测芯片的电源供电电压设置为参考供电电压来搭建待测芯片的参考工作状态;所述参考工作状态使得待测芯片的电源供电电流不超过通过实验或仿真得到的标准芯片在相同电源供电电压下对应电源供电电流的设定阈值。

13、进一步的,步骤3还包括:针对芯片本身的供电电源漏电失效定位,通过将待测芯片的电源供电电压设置为异常供电电压来搭建待测芯片的异常工作状态;所述异常工作状态使得待测芯片的io口的电流超过通过实验或仿真得到的标准芯片在相同偏置电压下对应io口的电流的设定阈值。

14、进一步的,步骤1还包括:针对芯片io口漏电失效定位,通过将待测芯片的io口的偏置电压设置为参考偏置电压来搭建待测芯片的参考工作状态;所述参考工作状态使得待测芯片的io口的电流不超过通过实验或仿真得到的标准芯片在相同偏置电压下对应io口的电流的设定阈值。

15、进一步的,步骤3还包括:针对芯片io口漏电失效定位,通过将待测芯片的io口的偏置电压设置为异常偏置电压来搭建待测芯片的异常工作状态;所述异常工作状态使得待测芯片的io口的电流超过通过实验或仿真得到的标准芯片在相同偏置电压下对应io口的电流的设定阈值。

16、进一步的,步骤1还包括:针对芯片io口漏电失效定位,通过将待测芯片的io口与负载断开以使得io口处于悬空状态来搭建待测芯片的参考工作状态;所述参考工作状态使得待测芯片的io口的电流不超过通过实验或仿真得到的标准芯片在相同偏置电压下对应io口的电流的设定阈值。

17、进一步的,步骤3还包括:针对芯片io口漏电失效定位,通过将待测芯片的io口与负载连接来搭建待测芯片的异常工作状态;所述异常工作状态使得待测芯片的io口的电流超过通过实验或仿真得到的标准芯片在相同偏置电压下对应io口的电流的设定阈值。

18、与现有技术相比,本发明能够在没有好样品,例如新产品研发失效的情况下,或者是好样品丢失的情况下,实现芯片的失效定位分析;同时,本发明无需分别针对好样品和失效样品搭建两套系统并保存相应的emmi定位亮点结果,从而大大降低了花费的时间、人力、物力成本。

技术特征:

1.一种针对芯片内部漏电失效进行emmi定位的方法,其特征在于,所述方法包括以下步骤:

2.根据权利要求1所述的针对芯片内部漏电失效进行emmi定位的方法,其特征在于:步骤5还包括:

3.根据权利要求1或2所述的针对芯片内部漏电失效进行emmi定位的方法,其特征在于:

4.根据权利要3所述的针对芯片内部漏电失效进行emmi定位的方法,其特征在于,步骤1还包括:

5.根据权利要求4所述的针对芯片内部漏电失效进行emmi定位的方法,其特征在于,步骤3还包括:

6.根据权利要3所述的针对芯片内部漏电失效进行emmi定位的方法,其特征在于,步骤1还包括:

7.根据权利要6所述的针对芯片内部漏电失效进行emmi定位的方法,其特征在于,步骤3还包括:

8.根据权利要3所述的针对芯片内部漏电失效进行emmi定位的方法,其特征在于,步骤1还包括:

9.根据权利要求8所述的针对芯片内部漏电失效进行emmi定位的方法,其特征在于,步骤3还包括:

技术总结

一种针对芯片内部漏电失效进行EMMI定位的方法,包括:针对芯片不同部位的失效定位需求,搭建待测芯片的参考工作状态,使待失效定位部位的内部漏电流不超过设定阈值;内部漏电流为待失效定位部位的内部电流与通过实验或仿真得到的标准芯片在相同部位、相同工作状态下的内部电流之差;通过微光显微镜EMMI定位获取参考工作状态下待失效定位部位的亮点结果;搭建待测芯片的异常工作状态,使待失效定位部位的漏电流超出所述设定阈值;通过微光显微镜EMMI定位获取异常工作状态下待失效定位部位的亮点结果;比较参考工作状态和异常工作状态下的亮点结果,将新增或减少的亮点视为待测芯片漏电的关联失效点。本发明能在没有好样品时实现芯片的失效定位分析。

技术研发人员:涂卓麟

受保护的技术使用者:江阴圣邦微电子制造有限公司

技术研发日:

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!