一种正余弦编码器及其角度解析方法与流程

本技术涉及编码器,尤其涉及一种正余弦编码器及其角度解析方法。

背景技术:

1、芯片产业的集成化和微型化发展,对于传感器等检测装置的尺寸,速度和功耗等性能指标愈加严格,通常是将模拟信号转化为数字信号处理,进一步对数字信号加以数字处理,从而达到提高性能指标的目的。在基于多相正余弦信号的角度解析方面,现有的角度解析方法可分为开环法和闭环法。

2、其中,开环法具有更好的瞬态响应能力而更适于高速检测。基于开环思想的角度解析又可为正切法和伪线性法,其中,正切法是将正余弦信号分别采样并做反正切计算中的除法计算,再通过查表法进行查表,从而得到最终角度值,即完成角度的线性解析。然而,这种方法需要两路adc(analog to digital converter,模数转换器)以及大量的数字资源,造成功耗大,延迟大,芯片尺寸大的问题。伪线性法是基于正弦曲线的部分区间线性特性完成线性逼近,但这种方法需要补偿信号的参与,仍然会造成消耗大量数字资源的问题。

技术实现思路

1、本技术提供一种旨在降低功耗、减少数字资源且减小延迟的正余弦编码器及其角度解析方法。

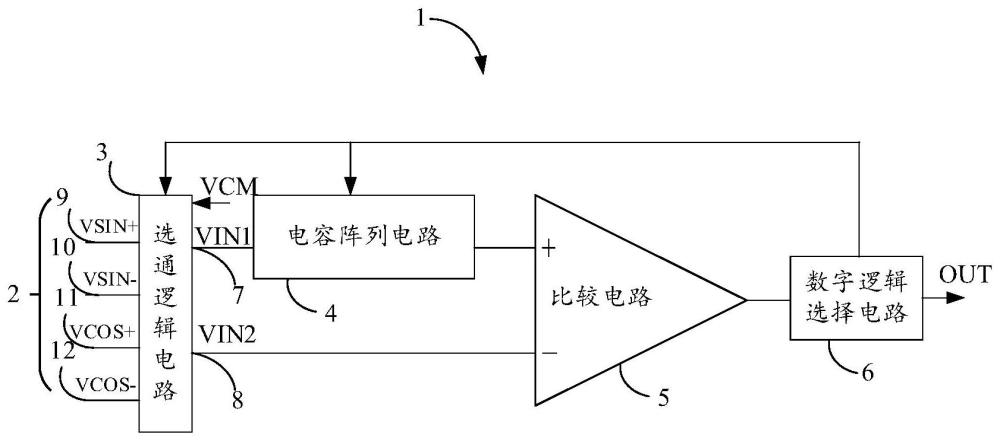

2、本技术提供一种正余弦编码器的角度解析电路,其中,包括:

3、用于分别提供四相输入电压信号的四个正余弦信号端;

4、选通逻辑电路,连接所述正余弦信号端,用于将所述四相输入电压信号与预设电压信号进行比较,且按照恒符合预设条件选择输出第一电压信号和第二电压信号;所述选通逻辑电路包括用于输出所述第一电压信号的第一输出端和输出所述第二电压信号的第二输出端;

5、电容阵列电路,连接所述第一输出端,用于根据预设缩放系数对所述第一电压信号进行电压缩放,以输出第一缩放电压信号;

6、比较电路,所述比较电路的正输入端连接所述电容阵列电路,所述比较电路的负输入端连接所述第二输出端,用于比较所述第一缩放电压信号和所述第二电压信号,以输出相应的实时电压比例值,且根据所述实时电压比例值获取相应的初步角度值;及

7、数字逻辑调节电路,连接所述比较电路的输出端、所述电容阵列电路及所述选通逻辑电路,用于根据所述实时电压比例值和所述初步角度值,并通过反馈调节所述预设缩放系数和所述选通逻辑电路的选择逻辑,以输出最终角度值。

8、可选的,所述电容阵列电路包括:

9、电压输入端,用于输入所述第一电压信号;

10、电压输出端,用于输出所述第一缩放电压信号;

11、采样开关、采样电容、至少八个充电电容及至少八个控制开关;其中,所述采样开关跨接于所述电压输入端和所述电压输出端之间;所述采样电容的一端接入所述预设电压信号,另一端连接于所述采样开关和所述电压输出端之间;每个所述充电电容的上级板对应连接每个所述控制开关,每个所述充电电容的下级板连接于所述采样开关和所述电压输出端之间;每个所述控制开关包括第一端子、第二端子及第三端子;每个所述控制开关的第一端子对应与每个所述充电电容的上极板连接,每个所述控制开关的第二端子与所述电压输入端连接,每个所述控制开关的第三端子接入所述预设电压信号。

12、可选的,所述至少八个充电电容依次按照先后顺序相互并联,其中前两个所述充电电容的容值均与所述采样电容的容值相同;

13、另外至少六个所述充电电容中的每个充电电容的容值是前一个所述充电电容的容值的两倍。

14、可选的,所述预设缩放系数a的计算公式为:

15、qtot=csvin; (1)

16、qtot=(cs+cn)vout+(cn-cn)(vout-vin); (2)

17、由公式(1)和(2),得到:

18、

19、其中,ctot=cs+cn;

20、qtot表示所述电容阵列电路中全部电容上的全部电荷;

21、cs表示采样电容;

22、vin表示采样电压;

23、cn表示所有充电电容中的上级板接到预设电压信号的所有电容总容值;

24、vout表示反馈调节后的电容上极板的电压值;

25、cn代表所有充电电容的电容总容值。

26、可选的,所述比较电路包括:

27、比较模块,所述比较模块的正输入端连接所述电容阵列电路的输出端,负输入端连接所述选通逻辑电路的所述第二输出端,用于比较所述第一缩放电压信号和所述第二电压信号,并输出比较结果;

28、正输出节点和负输出节点;

29、正反馈模块,连接所述比较模块及所述正输出节点、所述负输出节点,用于根据所述比较结果使所述正输出节点和所述负输出节点中的其中一个输出高电平,另一个输出低电平。

30、可选的,所述比较电路还包括:

31、启动模块,连接所述比较模块,且接入时钟信号,用于在时钟信号为高电平时,以启动所述比较模块工作;

32、复位模块,连接所述正反馈模块,且接入时钟信号,用于在时钟信号为低电平时,以复位所述正反馈模块为高电平。

33、可选的,所述比较电路还包括用于接入偏置电流的电流偏置端和电流镜模块;所述电流镜模块连接所述电流偏置端,以及通过所述启动模块连接所述比较模块,所述电流镜模块通过复制所述偏置电流,使所述比较模块中的电流产生偏置。

34、可选的,所述恒符合预设条件为所述第一电压信号大于所述第二电压信号,及所述第二电压信号大于所述预设电压信号。

35、可选的,所述四相输入电压信号包括正相正弦电压信号、负相正弦电压信号、正相余弦电压信号及负相余弦电压信号;所述四个正余弦信号端包括用于接入所述正相正弦电压信号的正相正弦信号端、用于接入所述负相正弦电压信号的负相正弦信号端、用于接入所述正相余弦电压信号的正相余弦信号端及用于接入所述负相余弦电压信号的负相余弦信号端;

36、所述选通逻辑电路还包括至少八个选通开关,所述至少八个选通开关至少包括第一选通开关、第二选通开关、第三选通开关、第四选通开关、第五选通开关、第六选通开关、第七选通开关、第八选通开关;

37、其中,所述第一选通开关和所述第二选通开关择一选择连接所述正相正弦信号端或所述负相正弦信号端;

38、所述第三选通开关和所述第四选通开关择一选择连接所述正相余弦信号端或所述负相余弦信号端;

39、所述第五选通开关连接于所述第一选通开关或第二选通开关,与所述第一输出端之间;所述第六选通开关连接于所述第一选通开关或第二选通开关,与所述第二输出端之间;

40、所述第七选通开关连接于所述第三选通开关或第四选通开关,与所述第一输出端之间;所述第八选通开关连接于所述第三选通开关或第四选通开关,与所述第二输出端之间。

41、本技术还提供一种正余弦编码器,其中包括如上述所述的角度解析电路。

42、本技术提供一种正余弦编码器的角度解析方法,包括用于分别提供四相输入电压信号的四个正余弦信号端、选通逻辑电路、电容阵列电路、比较电路及数字逻辑调节电路。选通逻辑电路用于将四相输入电压信号与预设电压信号进行比较,且按照恒符合预设条件选择输出第一电压信号和第二电压信号。电容阵列电路用于根据预设缩放系数对第一电压信号进行电压缩放,以输出第一缩放电压信号。比较电路用于比较第一缩放电压信号和第二电压信号,以输出相应的实时电压比例值,且根据实时电压比例值获取相应的初步角度值。数字逻辑调节电路用于根据实时电压比例值和初步角度值,并通过反馈调节预设缩放系数和选通逻辑电路的选择逻辑,以输出最终角度值。本技术通过电容阵列电路和比较电路完成反正切计算,并通过数字逻辑调节电路反馈调节预设缩放系数和选通逻辑电路的选择逻辑,从而获取高精度的最终角度值,如此,避免了采用两路adc进行反正切计算处理,从而有效降低功耗、减小检测延迟以及减小数字资源,且有利于减小正余弦编码器的尺寸。

43、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本技术。

- 还没有人留言评论。精彩留言会获得点赞!