测试系统的制作方法

本申请涉及信号处理,特别是涉及一种测试系统。

背景技术:

1、半导体自动化测试,指的是利用测试机对被测器件(device under test,dut)的各项参数指标进行检测,剔除残次品以控制半导体器件的出厂品质。传统的测试机中,时序生成和波形合成依赖于专用ic(integrated circuit,集成电路)芯片,实现结构复杂,存在设计复杂度高的缺点。

技术实现思路

1、基于此,有必要针对上述问题,提供一种可降低设计复杂度的测试系统。

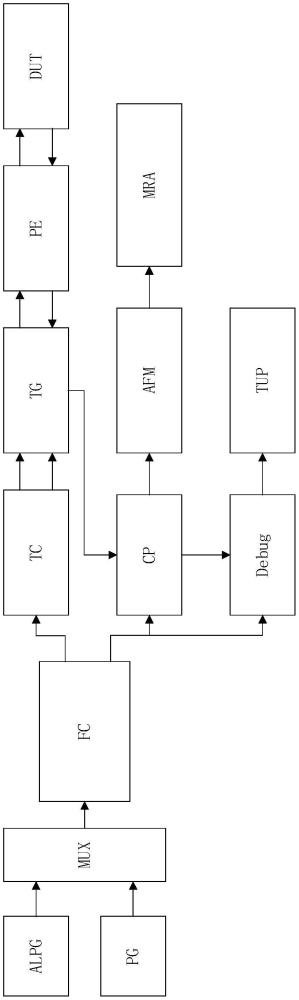

2、一种测试系统,包括:

3、至少两个输出数据源模块;

4、多路复用选择模块,连接各所述输出数据源模块,切换输出对应输出数据源模块的测试图形;

5、波形合成模块(format controller,fc模块),连接所述多路复用选择模块,接收所述多路复用选择模块输出的所述测试图形,输出合成波形;

6、时序生成模块(timing generator,tg模块),连接所述波形合成模块,接收所述波形合成模块输出的所述合成波形,生成输出波形;

7、引脚电路模块(pin electronics driver/comparator,pe模块),连接所述时序生成模块和待测试器件,接收所述时序生成模块生成的输出波形,输出激励信号至所述待测试器件。

8、在其中一个实施例中,所述输出数据源模块包括算法图形生成模块(algorithmicpattern generator,alpg模块)和图形生成模块(pattern generator,pg模块)。

9、在其中一个实施例中,测试系统还包括比较处理模块,所述比较处理模块连接所述时序生成模块和所述波形合成模块;

10、所述引脚电路模块接收所述待测试器件反馈的输入信号,输出比较信号至所述时序生成模块;

11、所述时序生成模块接收所述引脚电路模块输出的所述比较信号,输出采样信号至所述比较处理模块;

12、所述比较处理模块接收所述时序生成模块输出的所述采样信号,输出比较结果。

13、在其中一个实施例中,测试系统还包括对所述时序生成模块进行延时时间设置的时序控制模块(timing controller,tc模块),所述时序生成模块通过所述时序控制模块连接所述波形合成模块。

14、在其中一个实施例中,测试系统还包括错误地址存储器模块(address failmemory,afm模块),所述错误地址存储器模块连接所述比较处理模块。

15、在其中一个实施例中,测试系统还包括存储器错误修复分析模块(memory repairanalysis,mra模块),所述存储器错误修复分析模块连接所述错误地址存储器模块。

16、在其中一个实施例中,测试系统还包括调试模块,所述调试模块连接所述比较处理模块和所述波形合成模块。

17、在其中一个实施例中,测试系统还包括测试单元处理器(test unit processor,tup模块),所述测试单元处理器连接所述调试模块。

18、在其中一个实施例中,所述时序生成模块包括carry模块、idelay和odelay中的至少一种。

19、在其中一个实施例中,所述时序生成模块为数控延迟链芯片。

20、上述测试系统,多路复用选择模块选择相应的输出数据源模块输出测试波形,先通过波形合成模块接收测试图形进行波形合成得到合成波形,再通过时序生成模块生成输出波形。最后,引脚电路模块根据接收的输出波形生成激励信号发送至待测试器件。采用先进行波形合成,再进行时序生成的处理方式得到输出波形,降低了延时补偿误差,可采用通用芯片实现波形输出功能,降低了设计成本。

技术特征:

1.一种测试系统,其特征在于,包括:

2.根据权利要求1所述的测试系统,其特征在于,所述输出数据源模块包括算法图形生成模块和图形生成模块。

3.根据权利要求1所述的测试系统,其特征在于,还包括比较处理模块,所述比较处理模块连接所述时序生成模块和所述波形合成模块;

4.根据权利要求3所述的测试系统,其特征在于,还包括对所述时序生成模块进行延时时间设置的时序控制模块,所述时序生成模块通过所述时序控制模块连接所述波形合成模块。

5.根据权利要求3所述的测试系统,其特征在于,还包括错误地址存储器模块,所述错误地址存储器模块连接所述比较处理模块。

6.根据权利要求5所述的测试系统,其特征在于,还包括存储器错误修复分析模块,所述存储器错误修复分析模块连接所述错误地址存储器模块。

7.根据权利要求3所述的测试系统,其特征在于,还包括调试模块,所述调试模块连接所述比较处理模块和所述波形合成模块。

8.根据权利要求7所述的测试系统,其特征在于,还包括测试单元处理器,所述测试单元处理器连接所述调试模块。

9.根据权利要求1-8任意一项所述的测试系统,其特征在于,所述时序生成模块包括carry模块、idelay和odelay中的至少一种。

10.根据权利要求1-8任意一项所述的测试系统,其特征在于,所述时序生成模块为数控延迟链芯片。

技术总结

本申请涉及一种测试系统,包括:至少两个输出数据源模块;多路复用选择模块,连接各输出数据源模块,切换输出对应输出数据源模块的测试图形;波形合成模块,连接多路复用选择模块,接收多路复用选择模块输出的测试图形,输出合成波形;时序生成模块,连接波形合成模块,接收波形合成模块输出的合成波形,生成输出波形;引脚电路模块,连接时序生成模块和待测试器件,接收时序生成模块生成的输出波形,输出激励信号至待测试器件。采用先进行波形合成,再进行时序生成的处理方式得到输出波形,降低了延时补偿误差,可采用通用芯片实现波形输出功能,降低了设计成本。

技术研发人员:魏世龙,冯州,阮圣宽

受保护的技术使用者:杭州长川科技股份有限公司

技术研发日:20230615

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!