一种半导体芯片测试装置的制作方法

本技术涉及半导体,具体涉及一种半导体芯片测试装置。

背景技术:

1、由于芯片结构精细、制造工艺复杂、流程繁琐,不可避免地会在生产过程中留下潜在的缺陷,使制造完成的芯片不能达到标准要求,随时可能因为各种原因而出现故障。因此,厂商在芯片的生产制造过程中,通常会对封装后的芯片进行测试。

2、目前,在芯片封装完成后,需要对芯片进行测试且分bin等级,“分bin等级”则是对于芯片制造商而言其实就是一种筛选:通过测试设备对每颗芯片进行性能参数的测试,然后根据芯片电压值,波段值,功率值的不同进行分类。而大部分芯片制造商所使用的测试工具,通常需要采用人工的方式将芯片脚位与测试工具的测试端连接,进而通过测试工具完成对芯片的测试。但是该测试工具只能单次只能对单颗芯片进行测试,测试效率较低,且通过人工手动将芯片脚位与测试端对接,容易对芯片脚位或者测试端造成损坏,导致芯片良率下降。

3、有鉴于此,确有必要提供一种解决上述问题的技术方案。

技术实现思路

1、本实用新型的目的在于:提供一种半导体芯片测试装置,来解决上述测试工具存在测试效率较低的问题。

2、为了实现上述目的,本实用新型采用以下技术方案:

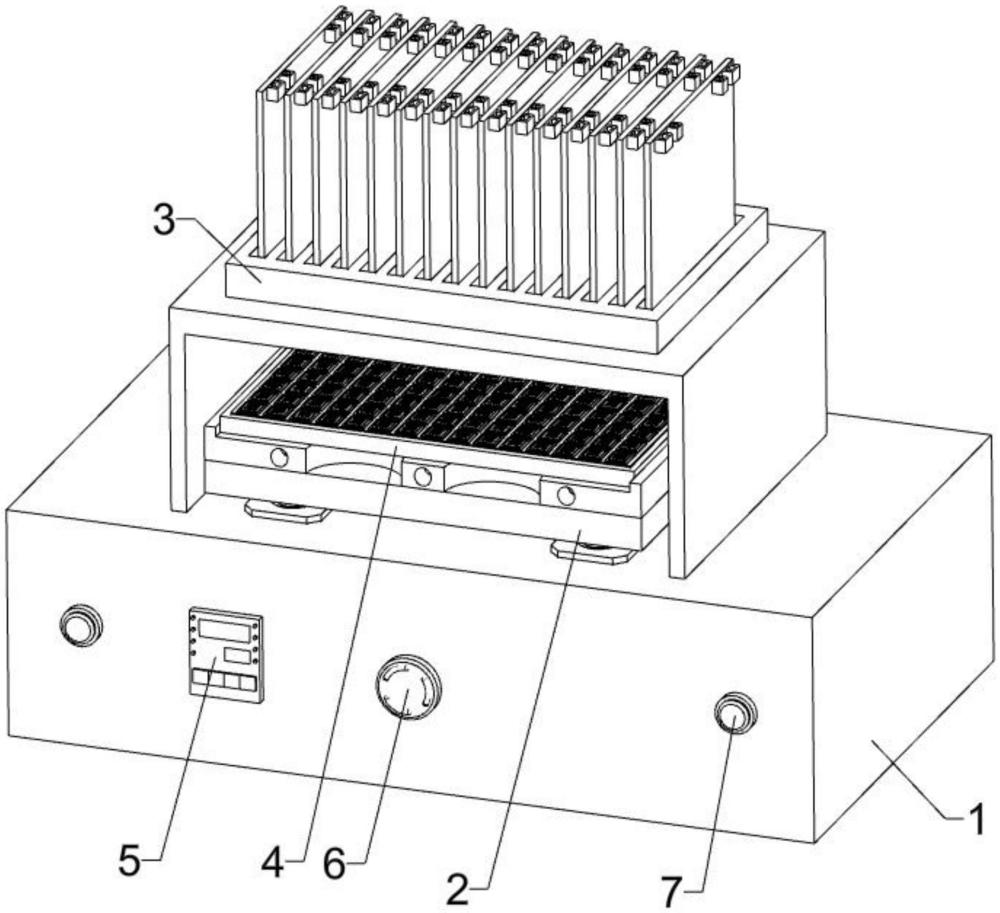

3、一种半导体芯片测试装置,包括机座以及设置在所述机座上的升降组件和测试部件,所述升降组件上卡接设置有放置座,位于所述测试部件的下方,所述放置座具有若干个用于放置芯片的容置槽,所述升降组件驱动所述放置座升降运动与所述测试部件配合,所述测试部件具有第一连接端和第二连接端,分别用于与所述放置座上的芯片脚位抵接后电性连接进行测试,以及作为输出端输出测试数据。

4、作为所述半导体芯片测试装置的一种改进,所述测试部件包括测试座和连接探针,所述测试座具有多个卡槽,所述卡槽内均安装有具有测试电路的测试板,所述连接探针设置有若干组,均位于所述测试座底部,分别与相应的容置槽位置对应,作为第一连接端,所述卡槽槽底均设置有连接电路,所述测试板通过所述连接电路与对应的多组所述连接探针电性连接。

5、作为所述半导体芯片测试装置的一种改进,所述测试板上具有电源接口以及作为所述第二连接端的输出接口,所述测试板通过所述电源接口与电源连接供电,所述输出接口用于与计算机设备连接传输测试数据。

6、作为所述半导体芯片测试装置的一种改进,所述机座包括机箱和固定架,所述固定架设置在所述机箱顶部,且用于安装所述测试座,所述放置座位于所述固定架的内侧。

7、作为所述半导体芯片测试装置的一种改进,所述升降组件包括固定座和升降件,所述放置座安装在所述固定座顶部,所述固定座底部设置滑杆,所述机箱上设置有与所述滑杆滑动连接的滑套,所述升降件设置在所述机箱内侧,与所述固定座连接,并可驱动所述固定座升降运动。

8、作为所述半导体芯片测试装置的一种改进,所述固定座底部四角位置均设置有所述滑杆,所述机箱与所述滑杆相应位置均设置有所述滑套。

9、作为所述半导体芯片测试装置的一种改进,所述固定座顶部具有限位部以及定位部,所述限位部具有至少两个,分别分布于所述固定座顶部相对的两侧,所述定位部位于两个所述限位部一侧端部之间,且靠近所述固定座顶部边缘。

10、作为所述半导体芯片测试装置的一种改进,所述固定座顶部端面至少一侧设置有开口。

11、作为所述半导体芯片测试装置的一种改进,所述升降件为气缸或者电动推杆。

12、相比于现有技术,本实用新型的有益效果在于:

13、1)本实用新型设置有可放置若干待测试芯片的放置座,并通过升降组件驱动,使得测试部件的第一连接端同时与放置座上若干待测试芯片的脚位抵接,同时对若干个芯片进行测试,有效的提高了测试效率,降低测试成本。

14、2)并且放置座通过卡接配合的方式固定在升降组件顶部,在测试过程中,可准备多个放置座,且均装满待测试芯片,当测试完其中一个放置座上的芯片后取出,将下一个装满待测试芯片的放置座卡接在升降组件顶部,然后对取出后的放置座上测试完的芯片取出分类,重新放置待测芯片,以此循环可不停的对芯片进行测试,更便于上下料,且提高了待测试芯片上料以及芯片测试完下料的速度。

技术特征:

1.一种半导体芯片测试装置,其特征在于,包括机座以及设置在所述机座上的升降组件和测试部件,所述升降组件上卡接设置有放置座,位于所述测试部件的下方,所述放置座具有若干个用于放置芯片的容置槽,所述升降组件驱动所述放置座升降运动与所述测试部件配合,所述测试部件具有第一连接端和第二连接端,分别用于与所述放置座上的芯片脚位抵接后电性连接进行测试,以及作为输出端输出测试数据。

2.根据权利要求1所述的半导体芯片测试装置,其特征在于,所述测试部件包括测试座和连接探针,所述测试座具有多个卡槽,所述卡槽内均安装有具有测试电路的测试板,所述连接探针设置有若干组,均位于所述测试座底部,分别与相应的容置槽位置对应,作为第一连接端,所述卡槽槽底均设置有连接电路,所述测试板通过所述连接电路与对应的多组所述连接探针电性连接。

3.根据权利要求2所述的半导体芯片测试装置,其特征在于,所述测试板上具有电源接口以及作为所述第二连接端的输出接口,所述测试板通过所述电源接口与电源连接供电,所述输出接口用于与计算机设备连接传输测试数据。

4.根据权利要求2所述的半导体芯片测试装置,其特征在于,所述机座包括机箱和固定架,所述固定架设置在所述机箱顶部,且用于安装所述测试座,所述放置座位于所述固定架的内侧。

5.根据权利要求4所述的半导体芯片测试装置,其特征在于,所述升降组件包括固定座和升降件,所述放置座安装在所述固定座顶部,所述固定座底部设置滑杆,所述机箱上设置有与所述滑杆滑动连接的滑套,所述升降件设置在所述机箱内侧,与所述固定座连接,并可驱动所述固定座升降运动。

6.根据权利要求5所述的半导体芯片测试装置,其特征在于,所述固定座底部四角位置均设置有所述滑杆,所述机箱与所述滑杆相应位置均设置有所述滑套。

7.根据权利要求5所述的半导体芯片测试装置,其特征在于,所述固定座顶部具有限位部以及定位部,所述限位部具有至少两个,分别分布于所述固定座顶部相对的两侧,所述定位部位于两个所述限位部一侧端部之间,且靠近所述固定座顶部边缘。

8.根据权利要求7所述的半导体芯片测试装置,其特征在于,所述固定座顶部端面至少一侧设置有开口。

9.根据权利要求5所述的半导体芯片测试装置,其特征在于,所述升降件为气缸或者电动推杆。

技术总结

本技术提供了一种半导体芯片测试装置,包括机座以及设置在所述机座上的升降组件和测试部件,所述升降组件上设置有放置座,位于所述测试部件的下方,所述放置座具有若干个用于放置芯片的容置槽,所述升降组件驱动所述放置座升降运动与所述测试部件配合,所述测试部件具有第一连接端和第二连接端,分别用于与所述放置座上的芯片脚位抵接后电性连接进行测试,以及作为输出端输出测试数据。本技术在提高芯片的测试效率的同时,也具备较高的上下料速度。

技术研发人员:张治强

受保护的技术使用者:广东长兴半导体科技有限公司

技术研发日:20230831

技术公布日:2024/4/29

- 还没有人留言评论。精彩留言会获得点赞!