晶体管测试设备及其测试方法与流程

本发明涉及半导体,尤其涉及一种可以测试晶体管的漏电电流的晶体管测试设备及其测试方法。

背景技术:

1、随着半导体技术的发展以及碳化硅(sic)金属-氧化物-半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,简称mosfet)等新产品的研发,对晶体管测试的要求也越来越高。碳化硅是一种具有出色的物理、化学和电性能特性的半导体材料,在功率半导体器件领域,特别是大功率、高电压条件下,具有很好的应用前景。晶体管的重要特性包括漏电极和源电极之间的漏电电流(idss)。

2、请参阅图1,其为现有高压晶体管测试的等效电路的示意图。如图1所示,通过电压源11在待测样品(dut)10的源电极s和漏电极d之间施加测试电压,通过电流检测仪19检测待测样品10的源电极s和漏电极d之间的测量电流作为漏电电流。

3、对于碳化硅高压晶体管产品,由于化合物产品设计电压较高,在进行测试时,需要让产品充分闭合后,再测试漏电极和源电极之间的漏电电流,从而通过对应的测试数据以更好的判断产品的性能。然而当前所用测试设备无法满足上述测试要求,故无法进行高压漏电电流(hvidsx)测试项目,x指代晶体管栅电极。

技术实现思路

1、本发明所要解决的技术问题是提供一种晶体管测试设备及其测试方法,可以在进行测试时让产品充分闭合后,以进行高压漏电电流测试,并能够使测试结果更加精准。

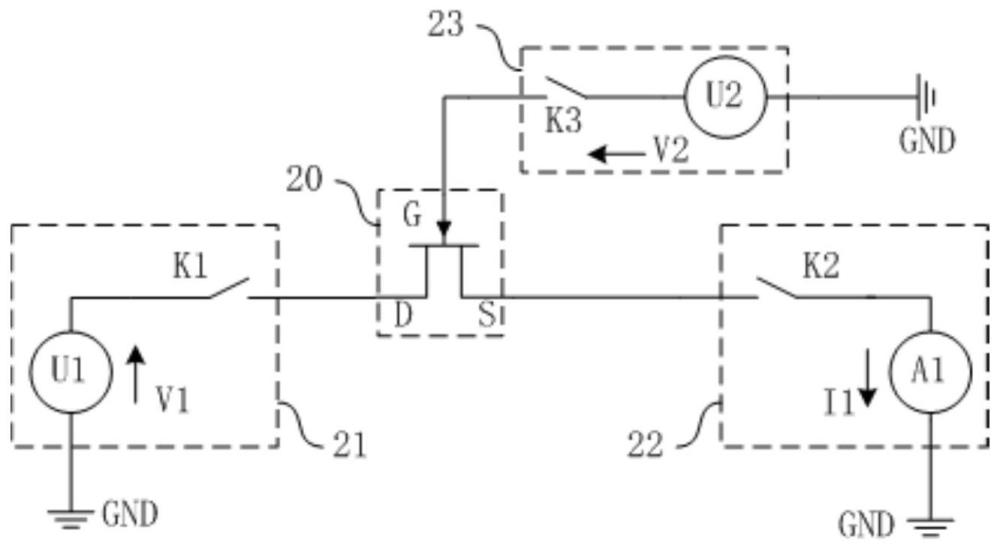

2、为了解决上述问题,本发明提供了一种晶体管测试设备,用于对待测样品进行测试,所述待测样品具有栅电极、源电极和漏电极;所述设备包括:第一测试支路,电连接在所述待测样品的所述漏电极和地端之间,所述第一测试支路包括串联的第一电压源以及第一开关,所述第一测试支路用于在所述第一开关闭合时通过所述第一电压源向所述待测样品的所述漏电极施加正向的第一测试电压;第二测试支路,电连接在所述待测样品的所述源电极和所述地端之间,所述第二测试支路包括串联的电流检测仪以及第二开关,所述第二测试支路用于在所述第二开关闭合时通过所述电流检测仪检测流过所述待测样品的所述源电极的检测电流,以获取所述待测样品的所述漏电极到所述源电极之间的漏电电流;第三测试支路,电连接在所述待测样品的所述栅电极和所述地端之间,所述第三测试支路包括串联的第二电压源以及第三开关,所述第三测试支路用于在所述第三开关闭合时通过所述第二电压源向所述待测样品的所述栅电极施加反向的第二测试电压,其中,所述第一测试电压的数量级大于所述第二测试电压的数量级。

3、为了解决上述问题,本发明还提供了一种晶体管测试方法,用于对待测样品进行测试,所述待测样品具有栅电极、源电极和漏电极;所述方法包括如下步骤:向所述待测样品的所述漏电极施加正向的第一测试电压,向所述待测样品的所述栅电极施加反向的第二测试电压,以及检测流过所述待测样品的所述源电极的检测电流,其中,所述第一测试电压的数量级大于所述第二测试电压的数量级;经过第一预设时间后,获取所述检测电流的电流值作为所述待测样品的所述源电极和所述漏电极之间的漏电电流。

4、上述技术方案,通过增设第三测试支路,采用第一测试支路在待测样品的漏电极到源电极之间加高压的同时,通过第三测试支路在待测样品的栅电极到源电极之间加负压以消耗其中的正离子,让产品充分闭合后,从而可以达到对待测试产品进行高压漏电电流测试项目的要求;且通过第三测试支路在待测样品的栅电极到源电极之间加负压,所获取的测试数据可以更好的判断产品的性能。进一步利用现有的低压设备中的电源引入高压设备中,以增加低压源提供负电压,并通过开关控制以使测试电压几乎完全同步的施加到待测样品的相应电极上,既实现了高压晶体管测试要求,又可以使测试结果更加精准,且简化并节省测试资源。

5、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本发明。对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为授权说明书的一部分。

技术特征:

1.一种晶体管测试设备,用于对待测样品进行测试,所述待测样品具有栅电极、源电极和漏电极;其特征在于,所述设备包括:

2.根据权利要求1所述的晶体管测试设备,其特征在于,所述待测样品为碳化硅金属-氧化物-半导体场效应晶体管。

3.根据权利要求1所述的晶体管测试设备,其特征在于,所述第一测试电压的范围为1000伏~3000伏,所述第二测试电压的范围为0伏~40伏。

4.根据权利要求1所述的晶体管测试设备,其特征在于,所述第一电压源以及所述第二电压源均采用可变电压源。

5.根据权利要求1所述的晶体管测试设备,其特征在于,所述第一开关、第二开关以及第三开关的导通/断开状态基本同步。

6.根据权利要求1所述的晶体管测试设备,其特征在于,所述第一开关、第二开关以及第三开关均采用继电器。

7.根据权利要求1所述的晶体管测试设备,其特征在于,采用高压测试盒中的高压源作为所述第一电压源,采用低压测试盒中的低压源作为所述第二电压源,且通过连接线将所述低压源连接至所述高压测试盒中,并于所述高压测试盒中增设所述第三开关;所述高压测试盒进一步连接至探针卡、并通过所述探针卡连接至所述待测样品的相应电极。

8.一种晶体管测试方法,用于对待测样品进行测试,所述待测样品具有栅电极、源电极和漏电极;其特征在于,所述方法包括如下步骤:

9.根据权利要求8所述的晶体管测试方法,其特征在于,所述第一测试电压的范围为1000伏~3000伏,所述第二测试电压的范围为0伏~40伏。

10.根据权利要求8所述的晶体管测试方法,其特征在于,

11.根据权利要求8所述的晶体管测试方法,其特征在于,

12.根据权利要求8所述的晶体管测试方法,其特征在于,所述方法进一步包括:经过第二预设时间后,停止向所述待测样品的所述漏电极施加正向的第一测试电压,停止向所述待测样品的所述栅电极施加反向的第二测试电压,以及停止检测流过所述待测样品的所述源电极的检测电流。

技术总结

本发明提供了一种晶体管测试设备及其测试方法。本发明通过增设第三测试支路,采用第一测试支路在待测样品的漏电极到源电极之间加高压的同时,通过第三测试支路在待测样品的栅电极到源电极之间加负压以消耗其中的正离子,让产品充分闭合后,从而可以达到对待测试产品进行高压漏电电流测试项目的要求;且通过第三测试支路在待测样品的栅电极到源电极之间加负压,所获取的测试数据可以更好的判断产品的性能。进一步利用现有的低压设备中的电源引入高压设备中,以增加低压源提供负电压,并通过开关控制以使测试电压几乎完全同步的施加到待测样品的相应电极上,既实现了高压晶体管测试要求,又可以使测试结果更加精准。

技术研发人员:刘士坤,周玲玲,邓攀,季鸣

受保护的技术使用者:上海积塔半导体有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!