一种多链并行分割高精度FPGA时间数字转换方法

一种多链并行分割高精度fpga时间数字转换方法

技术领域

1.本发明涉及高精度时间测量,尤其涉及一种应用在现场可编程逻辑器件fpga的tdc高精度实现方法。可应用于时间传输、基础研究等领域。

背景技术:

2.时间测量是现代社会各种重要技术的基础,常用于时间传输、时钟比对、定时同步、精密测量、光通信等领域。高精度的时间间隔测量技术,尤其是皮秒量级的技术更为重要。目前,应用最广泛的高精度时间间隔测量技术是时间数字转换技术(time to digital converter,tdc),相比于asic的tdc,fpga-tdc有着开发周期短、设计灵活等优点。在基于fpga的tdc设计中,使用加法进位链构成的延迟链对时钟周期进行内插的方法已被广泛使用。然而基于加法进位链构成的延迟链有以下两个特点:延迟单元的不一致性和存在较大延迟单元。其中延迟单元的不一致性是由fpga制造工艺决定的,较大延迟单元是由多余走线和跨时钟区域造成的。上述特点是限制tdc测量精度的主要因素。另外,环境温度和工作电压的改变也会影响内插单元的延时。

3.为了提高fpga-tdc的测量精度,人们提出了多种解决方案。在先技术一:wu,j.,and z.shi."the 10-ps wave union tdc:improving fpga tdc resolution beyond its cell delay."paper presented at the ieee nuclear science symposium conference record,2009.提出了wave union的方法来提高测量精度。该方法通过将待测信号转换为相应的周期信号,从而在单条延迟链上实现多次测量。由于每次测量的起始位置不同,所以每次落在的延迟单元也不同。这样通过在单条延迟链上进行多次测量就实现了不同延迟单元间的切割,从而将较大延迟单元切割成小的延迟单元。因此突破了延迟单元的固有物理时延,使tdc的分辨率和测量精度都得到了有效的提高。但是该方法会引入较大的死时间,因为每次测量至少花费一个时钟周期,那么n次测量就需要至少n个时钟周期。该结构的tdc在一些要求高吞吐量的场景下无法使用,并且其译码电路比较复杂。

4.在先技术二:qin,x.,l.wang,d.liu,y.zhao,x.rong,and j.du."a1.15-ps bin size and 3.5-ps single-shot precision time-to-digital converter with on-board offset correction in an fpga."ieee transactions on nuclear science 64,no.12(2017):2951-57.提出了多链并行测量求平均的方法。该方法将待测信号同时输入n条延迟链,把得到的n个时间戳求平均作为最终的细测量结果,理论上分辨率可以提高倍。该方法可以在一个时钟周期内完成n次测量,在改善tdc分辨率的同时兼顾了死时间。但是该结构tdc的多条延迟链带来大的资源开销,除此之外还需要复杂的校准模块和计算模块。校准模块不仅要校准、存储每条延迟链的真实时延,还需要校准不同链间的走线时延,最后通过计算模块来得到平均值。

技术实现要素:

5.为克服上述现有技术的不足,本发明提出了一种多链并行分割高精度fpga时间数

字转换方法,将多条并行延迟链分割合并为一条等效延迟链,使用该等效延迟链对一个时钟周期进行内插,从而实现高精度的tdc。

6.本发明原理如下:

7.使用原语将fpga内部相邻专用进位单元的cout与cin相连,由此级联形成延迟链。每个cout作为d触发器的输入,当系统时钟上升沿到来时,d触发器采样得到此时cout的数值,由此得到一串温度计码111..000,其中1的个数即为待测脉冲上升沿从进入延迟链到下一个系统时钟上升沿这段时间经过的延迟单元个数。

8.本发明的技术解决方案如下:

9.一种多链并行分割高精度fpga时间数字转换方法,其特点在于,

10.将待测脉冲输入n条并行的延迟链,设待测脉冲在第i个延迟链中从输入到被捕捉经过τi个延迟单元;

11.将每条延迟链得到的延迟单元τi相加,作为待测脉冲在等效延迟链中经过的延迟单元τ,即

12.将位置不同、各延迟单元不同的并行延迟链相互分割,最终合并得到一条等效延迟链。使用该等效延迟链对一个时钟周期内插,从而提高tdc的测量精度。等效延迟链的延迟单元约为单条延迟链的n倍,因此平均分辨率相较于单链tdc提高了n倍。

13.所述延迟链由fpga的专用进位单元级联构成。

14.将相邻的专用进位单元cin与cout相连,由此级联形成所述的延迟链,且每个专用进位单元cout作为d触发器的输入,当系统时钟上升沿到来时,d触发器对cout数据完成采样。

15.所述的等效延迟链经过校准阶段后将得到延迟单元信息构建为查找表存储在ram中;在测量阶段得到待测脉冲在等效延迟链中经过τ个延迟单元后,查表即可得到细测量时间。

16.本发明的特点和优点是:

17.1)本发明将n条延迟链分割合并成一条等效延迟链,不仅对较大延迟单元完成了分割,而且等效延迟单元增加了n倍。这样通过等效延迟链对一个时钟周期进行内插,使其平均分辨率增强了n倍,测量精度也得到有效提升。

18.2)本发明相对于在先技术一,在打破延迟单元物理时延,提高分辨率和测量精度的同时,没有引入多余的死时间。相对于在先技术二,只需校准、存储等效延迟链的真实时延,而且无需后续的求平均计算。大大简化了电路,节约了资源使用。

19.3)本发明得益于多链间的相互分割,等效延迟链有了颗粒度更小且数量更多的延迟单元,使得tdc分辨率对环境温度变化不敏感。

附图说明

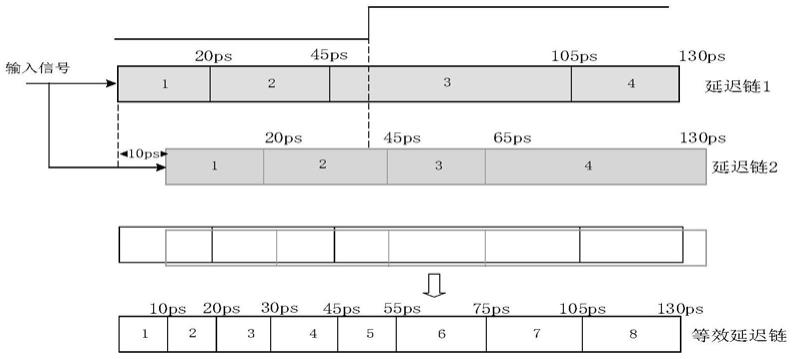

20.图1是本发明的多链分割合并为等效延迟链的原理图;

21.图2是本发明的电路功能框图。

22.图3是本发明中粗细测量时序图

具体实施方式

23.下面结合实施例和附图对本发明作进一步说明,但不应以此限制本发明的保护范围。

24.先请参阅图1,图1是本发明中多链分割合并为等效延迟链的原理图,由图可见,不同的矩形代表不同宽度的延迟单元。延迟链的延迟单元是不均匀的,两条延迟链之间也不相同。另一方面,不同的延迟链物理位置不同,则输入信号到每条延迟链之间的走线时延也是不同的。所以同一个输入信号在不同的延迟链上经过的延迟单元数是不同的。如图1所示,输入信号上升沿落在第一条链的第3个延迟单元,而落在第二条链的第2个延迟单元。将两条链的延迟单元数相加作为等效延迟链的延迟单元数,由此得到一条等效延迟链,则输入信号上升沿落在等效延迟链的第5个延迟单元。可以看到,两条链互相分割合并后的等效延迟链,其平均分辨率提高了两倍,且延迟链1中的第三个较大延迟单元也得到了有效分割。由此可知,将n条延迟链分割合并为一条等效延迟链后,其延迟单元为单链的n倍,则平均分辨率提高了n倍。同时单链里存在的较大延迟单元也被分割为正常大小,测量精度得到有效提升。链间分割同样改善了由环境温度改变对单链延迟单元大小造成的影响。

25.本发明的实施例如下:

26.利用本发明提出的多链并行分割法在赛灵思fpga上实现双通道tdc,tdc框图如图2所示,将待测脉冲1和待测脉冲2分别输入通道1和通道2,通道1和通道2的结构相同。以通道1来进行说明,使用原语调用carry4单元(如果是intel fpga,则为le的进位链单元),将前后carry4单元的cout和cin相连,实现将多个carry4单元级联为延迟链。延迟链的长度由系统时钟决定。延迟链的每个抽头接到d触发器的输入端,构成了触发器阵列。当系统时钟上升沿到来,触发器阵列对延迟链抽头进行采样,得到形如111

…

000的温度计码,再将温度计码输入译码电路,把1的个数转换为二进制值,也即是传输经过延迟单元的个数。使用同样的方法构造n条这样的延迟链,使其在fpga芯片上并行排列。校准模块得到等效延迟链,把等效延迟链延迟单元大小的查找表存放在ram中。粗计数模块由计数器构成,计数整周期的个数,实现大范围的时延测量。将粗测量结果和细测量结果都存储在ram中,当测量结束后,将粗测量结果和细测量结果组合得到最终的时延测量结果。

27.所述的校准模块将译码电路得到的n个值相加作为等效延迟链的值。在正式测量前,使用码密度法校准得到等效延迟链每个延迟单元的大小。由独立晶振产生的随机脉冲信号在延迟链上传输。对于一个校准信号上升沿,在不同延迟链上被不同延迟单元捕捉,将落在每条延迟链上的延迟单元数相加作为落在等效延迟链上的延迟单元数。经过大量随机脉冲信号校准后,通过统计方法得到等效延迟链每个延迟单元的大小,即其中n为校准脉冲信号的次数,k为落在每个延迟单元bin上的次数。由此便可得到等效延迟链每一个延迟单元的大小,将每个延迟单元对应的延迟大小作为查找表存放在ram中,完成对等效延迟链的校准。

28.校准完成后即可进行时延测量,将待测脉冲1和待测脉冲2分别接入tdc的通道1和通道2。当通道1细测量有效信号置高时,将细测量值和此时粗计数值n1存入ram。当通道2细测量有效信号置高时,将细测量值和此时粗计数值n2存入ram。细测量模块则记录了脉冲上升沿到下一个时钟上升沿之间经过了多少个延迟单元,由存储在ram中等效延迟链延迟单

元大小的查找表即可得知细测量时间t1和t2。图3是粗细测量时序图,如图所示,两个待测脉冲间的时间间隔即为ti=nt

clk

+t

1-t2,其中n=n

2-n1。

29.本发明将多条加法进位链采用链间分割合并成一条等效延迟链,实现对一个时钟周期的内插,完成细时间测量。合并得到的等效延迟链改善了单条延迟链延迟单元不均匀、有较大延迟单元的问题,使tdc的测量分辨率和测量精度得到明显提升,并且简化了电路,有效降低了环境温度变化带来的影响。本发明属于时间测量技术领域,可应用于时间传输、时钟比对、定时同步、精密测量、光通信等领域。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1