一种低压高精度CMOS带隙基准电路的制作方法

一种低压高精度cmos带隙基准电路

技术领域

1.本发明涉及基准电路,尤其涉及一种低压高精度cmos带隙基准电路。

背景技术:

2.在物联网和大多数无线通讯的应用中,相关接收电路或者发射电路等都是需要低功耗的,因此能产生低功耗的基准电路对整个应用来讲是非常关键和非常必要的。基准电路作为模拟电路的重要部分,一般需要在一个较宽的温度范围内正常工作,因此不仅要求功耗低,还需要性能稳定,有较好的温度特性。由于电源电压的降低,晶体管不匹配引起的随机误差对低压基准源的精度影响变得很大。这种由于集成电路工艺引起的本征误差是不可能完全消除的。

技术实现要素:

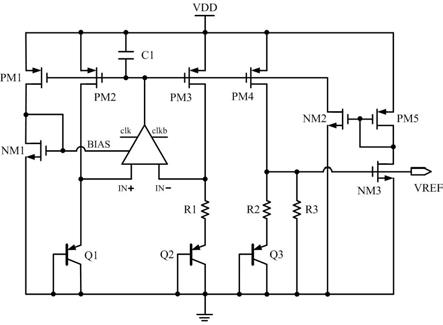

3.为克服上述现有技术存在的问题,本发明设计了用电流反馈、电阻二次分压和一级温度补偿技术实现了一种低压高精度cmos带隙基准电路,为了抑制器件失配对基准源精度的影响,负反馈放大器采用了斩波二级差分运放。精度高,结构简单,调整方便,非常符合高精度的设计要求。

4.为达上述及其它目的,本发明提供一种低压高精度cmos带隙基准电路,其至少包括:一启动电路,保证系统在上电时能稳定工作;一偏置电路,为所述运放提供偏置电流;一核心基准电路,运用了电流反馈、电阻二次分压和一级温度补偿技术,利用斩波调制技术消除了反馈运放的失调电压。

5.所述启动电路由第二nmos管nm2、第三nmos管nm3和第五pmos管pm5构成;pm5管的源极连接到电源电压vdd;pm5管的栅极与pm5管的漏极、nm2管的栅极和nm3管的漏极相连接;nm3管的栅极作为基准电压vref的输出端;nm2管的源极和nm3管的源极接地。

6.所述偏置电路由第一pmos管pm1、第一nmos管nm1构成;pm1管的源极连接电源电压vdd;pm1管的栅极连接到nm2管的漏极;pm1管的漏极与nm1管的栅极和nm1管的漏极相连接;nm1管的源极接地。

7.所述核心基准电路由第一电容c1、第二pmos管pm2、第三pmos管pm3、第四pmos管pm4、第一电阻r1、第二电阻r2、第三电阻r3、第一三极管q1、第二三极管q2、第三三极管q3和一运放电路构成;pm12管的源极、pm3管的源极、pm4管的源极和电容c1的一端都连接到电源电压vdd;pm2管的栅极与pm1管的栅极、pm3管的栅极、pm4管的栅极、电容c1的另一端和运放电路的输出端;pm2管的漏极与运放电路的同相输入端和q1管的发射极相连接;pm3管的漏极与运放电路的反相输入端和电阻r1的一端相连接;电阻r1的另一端连接到q2管的发射极;运放电路的偏置端连接到nm1管的栅极;运放电路还接入两个反相的周期方波信号clk和clkb;pm4管的漏极与电阻r2的一端、电阻r3的另一端和nm3管的栅极相连接;电阻r2的另一端连接到q3管的发射极;q1管的基极、q1管的集电极、q2管的基极、q2管的集电极、q3管的

基极、q3管的集电极和电阻r3的另一端都接地。

8.所述运放电路由第二电容c2、第七pmos管pm7、第八pmos管pm8、第九pmos管pm9、第四nmos管nm4、第五nmos管nm5、第六nmos管nm6、第七nmos管nm7、第八nmos管nm8、第九nmos管nm9、第十nmos管nm10、第十一nmos管nm11、第十二nmos管nm12、第十三nmos管nm13、第十四nmos管nm14和第十五nmos管nm15构成;nm4管的栅极、nm7管的栅极、nm9管的栅极、nm10管的栅极连接信号clk;nm5管的栅极、nm6管的栅极、nm8管的栅极、nm11管的栅极连接信号clkb;nm4管的源极连接nm6管的漏极,作为运放的同相输入端;nm5管的漏极连接nm7管的源极,作为运放的反相输入端;nm4管的漏极连接nm5管的源极,并标记为x1;nm6管的源极连接nm7管的漏极,并标记为x2;pm7管的源极、pm8管的源极和pm9管的源极都连接电源电压;pm7管的栅极与pm8管的栅极、pm9管的栅极、nm8管的源极和nm9管的漏极相连接;pm7管的漏极与nm8管的漏极、nm10管的源极和nm12管的漏极相连接;pm8管的漏极与nm9管的源极、nm11管的漏极和nm13管的漏极相连接;pm9管的漏极与电容c2的一端和nm15管的漏极相连接,其节点作为运放电路的输出端;nm15管的栅极与电容c2的另一端、nm10管的漏极和nm11管的源极相连接;nm12管的栅极连接到x1;nm13管的栅极连接到x2;nm12管的源极与nm13管的源极和nm14管的漏极相连接;nm14管的栅极作为运放的偏置端;nm14管的源极和nm15管的源极接地。

附图说明

9.构成本技术的一部分的附图用来提供对本发明的进一步理解,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中:图1为本发明一种低压高精度cmos带隙基准电路;图2为本发明中的运放电路。

具体实施方式

10.结合图1所示,在下面的实施例中,所述一种低压高精度cmos带隙基准电路,包括:一启动电路,保证系统在上电时能稳定工作;一偏置电路,为所述运放提供偏置电流;一核心基准电路,运用了电流反馈、电阻二次分压和一级温度补偿技术,利用斩波调制技术消除了反馈运放的失调电压。

11.所述启动电路由nm2管、nm3管和pm5管构成;保证系统在上电时能稳定工作。所述偏置电路由pm1管、nm1管构成;为运放电路提供偏置电流。

12.所述核心基准电路由电容c1、pm2管、pm3管、pm4管、电阻r1、电阻r2、电阻r3、q1管、q2管、q3管和一运放电路构成;q1管和q2管都是双极性器件,均作二极管连接,两管的基射极电压呈现负温度特性,基射极电压差呈现正温度特性,利用两者进行一级温度补偿;输出端引入一个分压电阻r3,确保能够获得较低的基准输出电压。

13.所述运放电路由电容c2、pm7管、pm8管、pm9管、nm4管、nm5管、nm6管、nm7管、nm8管、nm9管、nm10管、nm11管、nm12管、nm13管、nm14管和nm15管构成;运放电路提供深度负反馈,采用了一种动态补偿方式的低失调斩波调制运放老提高基准输出的精度。比如,当clk为高,clkb为低时(clk和clkb为两个反相的周期方波信号),pm7管镜像pm8管的电流,nm12管的栅极为反相端,nm13管的栅极为同相端;反之,nm12管的栅极为同相端,nm13管的栅极为

同相端;这样让输出端在两条支路之间轮流切换,动态补偿晶体管尺寸不匹配引起的误差。其中,差分输入级和密勒补偿电容c2起低通滤波作用,可以还原出被放大的初始信号,节省了占用面积和功耗。

14.本发明提出了一种低压高精度cmos带隙基准电路,基于smic 0.18um cmos工艺,在图1中,nm1管的宽长比是2um/2um,nm2的宽长比是2um/4um,nm3的宽长比是4um/4um,pm1的宽长比是2um/4um,pm2的宽长比是4um/4um,pm3的宽长比是4um/4um,pm4的宽长比是8um/4um,pm5的宽长比是4um/4um,电容c1是3.6pf,电阻r1是60k欧姆,电阻r2是650k欧姆,电阻r3是800k欧姆,晶体管q1发射极的面积是5um*5um,晶体管q2发射极的面积是8*5um*5um,晶体管q3发射极的面积是5um*5um。图2的运放中,nm4管的宽长比是5um/0.2um,nm5管的宽长比是5um/0.2um,nm6管的宽长比是5um/0.2um,nm7管的宽长比是5um/0.2um,nm8管的宽长比是5um/0.2um,nm9管的宽长比是5um/0.2um,nm10管的宽长比是5um/0.2um,nm11管的宽长比是5um/0.2um,nm12管的宽长比是10um/1um,nm13管的宽长比是10um/1um,nm14管的宽长比是40um/4um,nm15管的宽长比是20um/0.2um,pm7的宽长比是8um/4um,pm8的宽长比是8um/4um,pm9的宽长比是16um/4um。在0℃到80℃温度范围内,温度系数仅为15ppm/℃;当电源电压范围为0.9v到2.2v时,输出基准电压波动小于0.05mv,最大功耗小于7.2uw。

15.虽然本发明利用具体的实施例进行说明,但是对实施例的说明并不限制本发明的范围。本领域内的熟练技术人员通过参考本发明的说明,在不背离本发明的精神和范围的情况下,容易进行各种修改或者可以对实施例进行组合,这些也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1