一种衬底电位可控的低压差分驱动器电路的制作方法

[0001]

本发明创造涉及集成电路设计领域,提出了一种衬底电位可控的低压差分驱动器电路。

背景技术:

[0002]

随着通信技术及大规模集成电路的发展,人们对数据传输要求的提高,高速度,低功耗和低成本是集成电路模块传输的基本要求和选择。低压差分信号电路以其高速度、抗噪声的性能方便了与其他差分信号接口的传输与操作。低压差分信号(low voltage differential signaling,lvds)是低电压摆幅的差分信号传输结构的电路,电路表现为驱动器由一个恒流源驱动一对差分信号,电流几乎全部流过接收端100ω匹配电阻产生350mv左右的差分电压。lvds作为单芯片器件,本质是数字与模拟信号的相互转换和高速传输,与pecl、lvpecl、lvttl、lvcmos、gtl、btl、ctt、sstl、外部网络hstl输出电兼容。

[0003]

典型的lvds电路如图1所示。核心为一个3.5ma的恒流源驱动一对差分信号,包含m1,m2,m3,m4以及在接收端前的一个100ω的负载。其中,m1,m4管栅端接a1,b2,当a1,b2相同为高电平m1,m4导通使3.5ma电流顺时针流过终端电阻,当驱动状态相反时,a2,b1为低电平,m2,m3截止,流经终端电阻电流方向改变,于是在终端产生一个逻辑高电平和低电平。鉴于lvds收发器芯片工作环境多变,温度,噪声的变化导致基准电压和电流受到干扰,进而影响到芯片的收发逻辑,使能端口的稳定性,加之磁场干扰产生的波动使差分信号共模电压存在偏移,导致传统驱动器难以输出准确的共模电平。

技术实现要素:

[0004]

本发明创造提供一种衬底电位可控的低压差分驱动器电路,解决了现有技术中存在的传统驱动器难以输出准确的共模电平的技术问题。

[0005]

为了实现上述目的,本发明创造采用了如下技术方案:

[0006]

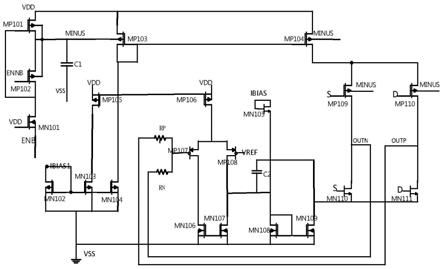

一种衬底电位可控的低压差分驱动器电路,包括有mp101-mp110,mn101-mn111:

[0007]

mp101栅端接mp102漏端;mp101衬底漏端相接,之后接到mp102源端,再接mp103、mp104、mp109、mp110的衬底;mn101栅端接vdd,源端接enb;mp102栅端接ennb,源端接mp101漏端,同时通过电容c1接地;

[0008]

驱动电流镜mn102的栅端接入偏置电流ibias1,并与mn102漏端、mn103栅端、mn104的栅端相接;mp105栅端与mp106栅端连接,mp105漏端接mn103源端,mp106漏端接mp107和mp108的源端;mp103栅漏相接且与mp104栅端相接,mp103漏端接mn104源端,mp104漏端接mp109和mp110的源端,mp103和mp104衬底相接并与mp101漏端连接;

[0009]

mp109与mn110栅端电位相同,mp110与mn111栅端电位相同;mp109与mp110源端相接,mp109与mn110漏端相接并与输出outn连接;mp110与mn111的漏端相接,并接输出outp;

[0010]

mp107栅端并联电阻rp和电阻rn,电阻rp另一端连接outp,电阻rn另一端连接outn;mp107源端与mp108源端相接,mp107漏端接mn106漏端;mp108栅端接参考电平,mp108

漏端接mn107漏端;mn106栅端与mn107栅端相接,差分放大器输出接电容c2,同时接mn108栅端源端;mn108栅端与mn109栅端相接,mn110和mn111源端相连,mn109漏端连接电容c2;

[0011]

mn105接偏置电流,栅端源端相接;mn108与mn109栅端相接,构成电流镜结构,将流经mn105的电流镜像到mn109;mn109漏端与mn110和mn111的源端相接。

[0012]

本发明创造的有益效果:

[0013]

1、与普通电流镜相比,采用控制衬底电位的电流镜,衬底电位可选择,减少对电源的依赖,同时降低静态功耗,通过多级电流镜像原理,为芯片的各个模块提供偏置电流,减小面积和功耗。

[0014]

2、驱动器电路模块采用衬底电位可控的pmos管,减少静态功耗。

附图说明

[0015]

图1为现有的lvds典型电路结构。

[0016]

图2为本发明驱动器电路结构示意图。

具体实施方式

[0017]

下面将结合本发明创造实施例中的附图,对本发明创造实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明创造一部分实施例,而不是全部的实施例。

[0018]

1、技术方案

[0019]

①

mp101与mp102衬底连接方式略有不同,控制mp103,mp104电流镜的衬底电位,控制逻辑传输管中mp109,mp110的衬底电位。mp101衬底漏端相接,接mp102源端和衬底,同时接mp103、mp104、mp109、mp110衬底,衬底电位是通过逻辑单元控制。mn101栅端接vdd,源端接enb。mp102栅端接ennb,源端接mp101漏端,通过接电容c1连接到地。

[0020]

②

mn102栅漏相连后与mn103栅端、mn104栅端相接,mn102栅端接入偏置电流ibias1。按照电流镜像比例,电流流经mn103、mn104,mp105、mp106构成电流镜,其中mp105栅漏端与mp106栅端相接,mp105漏端接到mn103源端,mp106漏端接到mp107和mp108的源端。mp103和mp104是基于衬底驱动的mos管组成的电流镜,其中mp103栅漏相接且与mp104栅端相接,mp103漏端接mn104源端,mp104漏端接mp109和mp110的源端,mp103和mp104衬底相接接到mp101的漏端。

[0021]

③

驱动器采用np互补型的电流模驱动形式,即驱动器电路采用pmos和nmos两种管子,略有不同的是除了通过内部逻辑控制mp109、mp110、mn110、mn111开关,mp109和mp110衬底电位也控制pmos晶体管。其中mp109、mn110栅端电位相同,mp110、mn111栅端电位相同。mp109、mp110漏端相接,mp109,mn110漏端相接并接输出outn;mn110、mn111源端相接,并接输出outp。采用np互补型开关减小漏电流,增加上面开关管的导通能力,布线很方便便于匹配。

[0022]

④

共模反馈回路由mp107、mp108、mn106、mn107、电容c2、mn108和mn109构成。mp107与mp108源端相接,mp107栅端并联电阻rp和rn,mp108栅端接参考电平。其中,参考电压由带隙基准电压源提供。mp107漏端接mn106漏端,mp108漏端接mn107漏端,mn106与mn105的栅端相接;差分放大器输出接电容c2,同时接mn108栅端和漏端,mn108与mn109栅端相接,mn109

漏端连接mn110和mn111源端。mn109漏端连接电容c2,增加电路的稳定性。

[0023]

mn105接偏置电流ibias,mn105栅端源端相接;mn108与mn109构成电流镜结构,mn108与mn109栅端相接,将流经mn105的电流镜像到mn109,mn109漏端与mn110和mn111的源端相接,形成3.5ma双电流源的整个电流回路。

[0024]

2、工作原理

[0025]

enb为低电平时,mn101栅端接高电平导通,mp101栅端接低电平,ennb为高电平,mp102截止,mp101输出为高电平,即mp103、mp104、mp109、mp110衬底为高电位;当enb为高电平,ennb为低电平时,mp101截止,mp102截止。mp109、mp110、mn110、mn111构成传输逻辑管;其中mp109和mn110、mp110和mn111分别为反相器连接方式。当enb为低电平,经过逻辑单元衬底电位为高电平时,正常工作,此时输入s为低电平,d为高电平时,即mp109、mn111导通,mp110、mn110截止,通过控制mp103和mp104的电流镜的比例,保证outn、outp输出电流为3.5ma,提供350mv典型值低压差分信号。

[0026]

驱动器电路模块接入偏置电流ibias1,mn102、mn103、mn104构成电流镜,通过电流镜产生镜像电流镜像到mn104。mp103、mp104构成电流镜,当衬底电位接高定平时,mp103电流镜像到mp104,驱动器内部逻辑模块控制s、d,使mp109和mn111导通或者使mp110和mn110导通,形成回路。流经rp、pn产生共模电压,将mp107栅级产生的共模电压和参考电压vref进行比较,输入到差分放大器,输出接到mn109漏端。mn105接基准电流,mn108、mn109构成电流镜,mn108的偏置电流通过电流镜镜像到mn109上,电阻r1和r2对提取出差分信号的共模电平进行调整,放大器通过比较基准电压vref和共模电平vcm的误差并反馈回输出传输逻辑管的电流镜,形成闭合反馈环路并保证vref≈vcm。通过逻辑单元电路控制将单端串行数据转双端数据s,d,通过s,d电平高低决定mn110、mn111打开与截止。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1