电压调节器的制作方法

1.本发明是有关于一种电压调节器,且特别是有关于一种在启动模式中可迅速提升输出电压的电压值的电压调节器。

背景技术:

2.现今的电压调节器设计趋势由以往的高功率朝向低功率及增加输出电流的方向发展。然而,这类的电压调节器通常内部组件的反应速度较慢,导致电压调节器将输出电压调节到所需电压值的时间较长。

技术实现要素:

3.本发明提供一种电压调节器,其可达成低功率、迅速启动及减少晶体管损坏的风险。

4.本发明的电压调节器包括输出端、第一晶体管、主驱动电路及次驱动电路。输出端用以输出一输出电压。第一晶体管包括第一端、第二端及控制端。第一晶体管的第一端耦接第一电压端用以接收第一电压,第一晶体管的第二端耦接电压调节器的输出端。主驱动电路包括第一输入端、第二输入端及输出端。主驱动电路的第一输入端耦接电压调节器的输出端用以接收输出电压,主驱动电路的第二输入端用以接收参考电压,主驱动电路的输出端耦接第一晶体管的控制端。次驱动电路包括第一端及第二端。次驱动电路的第一端耦接第一晶体管的控制端,次驱动电路的第二端耦接预定电压端。当电压调节器操作在启动模式时,由主驱动电路及次驱动电路驱动第一晶体管,第一晶体管的控制端与预定电压端透过次驱动电路而电性耦接。当电压调节器操作在正常模式时,由主驱动电路驱动第一晶体管,第一晶体管的控制端与预定电压端之间的电性耦接透过次驱动电路而被断开。

附图说明

5.图1是一种电压调节器的模块图。图2是绘示图1电压调节器在运作时的选定信号的波形图。图3是依照本发明的第一实施例的一种电压调节器的模块图。图4是本发明的第一实施例中次驱动电路的电路示意图。图5是绘示图4中电压产生电路的电路示意图。图6是绘示图3电压调节器在运作时的选定信号的波形图。图7是本发明的第一实施例中另一次驱动电路的电路示意图。图8是本发明的第一实施例中另一次驱动电路的电路示意图。图9是本发明的第二实施例的一种电压调节器的模块图。图10是本发明的第一实施例或第二实施例中另一次驱动电路的电路示意图。图11是本发明的第一实施例或第二实施例中另一次驱动电路的电路示意图。符号说明

100、300、900:电压调节器110:主驱动电路210:虚线圆框320、320-1~320-6:次驱动电路410:开关421-1~421-5:控制电路422-1、422-2:触发电路424-1、424-2:逻辑电路426、426-1、426-2:电压产生电路728-1、728-2:pn结组件990、vd1:分压电路c1:电容cl1:钳位电路cs1:控制信号d1、d2:二极管del1:延迟电路det1:侦测电路eamp:误差放大器im1~im4、m1~m4:晶体管in1、in2:主驱动电路的输入端inv1、inv2:反相器io:输出电流kn1、kn2、kn3:触发电路的第一端、第二端、输出端ln1、ln2、ln3:逻辑电路的第一端、第二端、输入端ln41、ln42:逻辑电路的输出端n990-1、n990-2、n990-3:分压电路的第一端、第二端、输出端nout:电压调节器的输出端nout2、nout3:控制电路的输出端out1:主驱动电路的输出端pd1~pd2:寄生二极管pg:操作信号pu1、pu2:上拉电路r1~r7:电阻rn1、rn2:控制电路的接收端t0:启动时点t1:工作时点tp1:启动模式tp2:正常模式v1、v2:电压

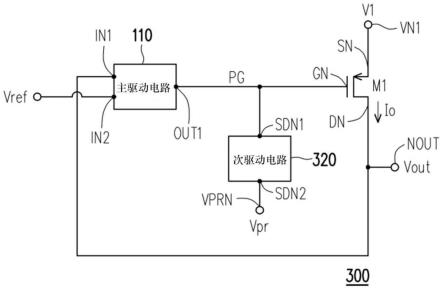

vin:输入电压vn1、vn2:电压端vgn1、vgn2、vgn3:电压产生电路的第一端、第二端、输出端vout:输出电压vprn:预定电压端vpr:预定电压vref:参考电压sdn1、sdn2:次驱动电路的第一端、第二端sn、dn、gn:晶体管的第一端、第二端、控制端

具体实施方式

6.图1是一种电压调节器100的模块图。电压调节器100可包括低压差稳压器(low-dropout regulator;ldo),用于将输出电压vout调节到所需的电压值。请参照图1,电压调节器100包括输出端nout、晶体管m1及主驱动电路110。输出端nout用以输出输出电压vout。于一些实施例中,电压调节器100的输出端nout可用以耦接负载,以对负载提供稳定的输出电压vout。此外,本发明可透过适当设计主驱动电路110,以使其在极低电流下仍可正常工作,如此一来,电压调节器100可具有低功率的特性。

7.晶体管m1可包括p型金属氧化物半导体(pmos)晶体管、p型场效晶体管(pfet)或pnp型双极性晶体管(bjt)。本实施例是以晶体管m1包括pmos晶体管作为举例说明。晶体管m1包括第一端sn、第二端dn及控制端gn。晶体管m1的第一端sn例如是源极端,第二端dn例如是漏极端,控制端gn例如是栅极端。晶体管m1的第一端sn耦接电压端vn1,用以接收电压v1。电压v1可为供电电压或系统电压。晶体管m1的第二端dn耦接电压调节器100的输出端nout。于一些实施例中,晶体管m1亦可以n型金属氧化物半导体(nmos)晶体管、n型场效晶体管(nfet)或npn型bjt来实现。

8.主驱动电路110包括输入端in1、输入端in2以及输出端out1。主驱动电路110的输入端in1耦接电压调节器100的输出端nout,用以接收输出电压vout。主驱动电路110的输入端in2用以接收参考电压vref。于一些实施例中,参考电压vref可为带隙(bandgap)参考电压。主驱动电路110的输出端out1耦接晶体管m1的控制端gn。主驱动电路110可用于比较输出电压vout及参考电压vref,以于输出端out1产生操作信号pg。操作信号pg可用于调节流经晶体管m1的输出电流io,进而调节输出电压vout。

9.图2是绘示图1电压调节器100在运作时的选定信号的波形图。请同时参见图1与图2,以便说明电压调节器100的运作方式。图2的横轴为时间,纵轴为电压值。在启动时点t0时,电压v1从0伏特(volt;v)迅速提升至接近6v,以为电压调节器100供电。晶体管m1的初始状态可设定为截止状态,因此操作信号pg在启动时点t0朝高位准提升,而电压调节器100的阻尼效应(damping effect)会使操作信号pg产生振荡(如虚线圆框210所示)。由于在极低电流下仍可正常工作的主驱动电路110具有较慢的反应速度,且本发明为使晶体管m1能够流经较大的输出电流io,从而采用尺寸较大的晶体管m1,因此主驱动电路110驱动晶体管m1的能力较弱,操作信号pg的位准将会缓慢的往下降,使得晶体管m1会缓慢的导通,亦即晶体管m1需较长的时间才可完全导通。另一方面,输出电压vout的位准对应操作信号pg缓慢下

降的位准而由0v缓慢的上升,导致电压调节器100需较长的时间才能将输出电压vout提升到所需的电压值。此外,电压v1相当于晶体管m1的第一端sn上的电压,输出电压vout相当于晶体管m1的第二端dn上的电压,由图2可得知,缓慢上升的输出电压vout的位准将使晶体管m1长时间承受较大的电压差,晶体管m1因而有损坏的风险。

10.图3是依照本发明的第一实施例的一种电压调节器300的模块图。电压调节器300与100不同之处在于,电压调节器300还包括次驱动电路320。次驱动电路320包括第一端sdn1及第二端sdn2。次驱动电路320的第一端sdn1耦接晶体管m1的控制端gn,第二端sdn2耦接预定电压端vprn。预定电压端vprn用以接收预定电压vpr。在一些实施例中,预定电压vpr可相关于输出电压vout,或是,预定电压vpr可与输出电压vout相同。应用本实施例者可依其需求适度调整预定电压vpr与输出电压vout之间的电压关系。特别说明的是,在预定电压vpr设定成与输出电压vout相同的实施例中,可将预定电压端vprn耦接电压调节器300的输出端nout,以用于接收输出电压vout。

11.当电压调节器300操作在启动模式时,可由主驱动电路110及次驱动电路320驱动晶体管m1,晶体管m1的控制端gn与预定电压端vprn可透过次驱动电路320而电性耦接。当电压调节器300操作于正常模式时,可由主驱动电路110驱动晶体管m1,晶体管m1的控制端gn与预定电压端vprn之间的电性耦接可透过次驱动电路320而被断开。在一些实施例中,电压调节器300可根据输出电压vout、预定电压vpr或电压v1来选择性地操作在启动模式或正常模式。次驱动电路320可根据输出电压vout、预定电压vpr或电压v1来判断电压调节器300的操作模式,从而选择性地将晶体管m1的控制端gn与预定电压端vprn电性耦接或电性断开。

12.本实施例可由多种电路结构来实现电压调节器300中的次驱动电路320,以下逐一说明。图4是本发明的第一实施例中次驱动电路320-1的电路示意图。次驱动电路320-1的第一端sdn1与第二端sdn2分别对应图3次驱动电路320的第一端sdn1与第二端sdn2。次驱动电路320-1包括开关410。开关410的第一端耦接次驱动电路320-1的第一端sdn1,第二端耦接次驱动电路320-1的第二端sdn2,控制端用以接收控制信号cs1。控制信号cs1用于控制开关410的导通状态,从而选择性地将晶体管m1的控制端gn与预定电压端vprn电性耦接或电性断开。也就是说,控制信号cs1相关于电压调节器300的操作模式。控制信号cs1可由次驱动电路320-1的内部电路或由次驱动电路320-1以外的外部电路提供。

13.图4是以控制信号cs1由次驱动电路320-1的内部电路提供作为举例说明。次驱动电路320-1还包括控制电路421-1。控制电路421-1包括接收端rn1、接收端rn2及输出端nout2。控制电路421-1的接收端rn1耦接电压端vn1,用以接收电压v1。控制电路421-1的接收端rn2耦接次驱动电路320-1的第二端sdn2,用以接收预定电压vpr。控制电路421-1的输出端nout2耦接开关410的控制端,用以输出控制信号cs1。

14.在此说明控制电路421-1的详细电路结构。控制电路421-1包括触发电路422-1。触发电路422-1包括第一端kn1、第二端kn2及输出端kn3。触发电路422-1的第一端kn1耦接控制电路421-1的接收端rn1,第二端kn2耦接控制电路421-1的接收端rn2,输出端kn3耦接控制电路421-1的输出端nout2。

15.详细来说,触发电路422-1包括上拉电路pu1及侦测电路det1。上拉电路pu1包括第一端及第二端。上拉电路pu1的第一端耦接触发电路422-1的第一端kn1,第二端耦接触发电路422-1的输出端kn3。上拉电路pu1可包括电阻或电流源,图4是以上拉电路pu1包括电阻r1

作为举例说明。

16.侦测电路det1包括第一端、第二端及输入端。侦测电路det1的第一端耦接上拉电路pu1的第二端,第二端耦接触发电路422-1的第二端kn2,输入端用以接收输入电压vin。输入电压vin可为固定电压或可变电压。此外,输入电压vin可由控制电路421-1的内部电路或由控制电路421-1以外的外部电路提供。侦测电路det1可包括晶体管m3。晶体管m3可由nmos晶体管、nfet或npn型bjt来实现。本实施例是以晶体管m3包括nmos晶体管作为举例说明。晶体管m3包括第一端、第二端及控制端。晶体管m3的第一端例如是漏极端,第二端例如是源极端,控制端例如是栅极端。晶体管m3的第一端耦接侦测电路det1的第一端,第二端耦接侦测电路det1的第二端,控制端耦接侦测电路det1的输入端。

17.本实施例的控制电路421-1可根据输出电压vout、预定电压vpr或电压v1来判断电压调节器300的操作模式,并据以输出控制信号cs1。详细来说,控制电路421-1可透过触发电路422-1来判断电压调节器300的操作模式,并据以输出控制信号cs1。进一步而言,图4是将预定电压vpr设定成与输出电压vout相同,且输入电压vin为固定电压作为举例说明。请同时参见图3与图4,触发电路422-1的第二端kn2可用以接收预定电压vpr,换句话说,晶体管m3的第二端上的电压相关于预定电压vpr,在本实施例中也即是,晶体管m3的第二端上的电压相关于输出电压vout。如此一来,可藉由晶体管m3的第二端上的电压与所设定的阈值之间的关系来判断电压调节器300的操作模式。特别说明的是,当晶体管m3的第二端上的电压小于阈值时,控制电路421-1可判断电压调节器300操作在启动模式;当晶体管m3的第二端上的电压大于阈值时,控制电路421-1可判断电压调节器300操作在正常模式。本实施例的阈值可设定为输入电压vin与晶体管m3的导通电压(turn-on voltage)的差值。应用本实施例者也可透过改变触发电路422-1的电路结构来调整阈值。

18.开关410可包括晶体管m2。晶体管m2可由nmos晶体管、nfet、npn型bjt、pmos晶体管、pfet、pnp型bjt来实现。图4是以晶体管m2为nmos晶体管作为举例说明。特别说明的是,当晶体管m2是由nmos晶体管、nfet或npn型bjt实现时,控制电路421-1还包括逻辑电路424-1,以对晶体管m2提供适当位准的控制信号cs1。在此情况下,触发电路422-1的输出端kn3透过逻辑电路424-1耦接控制电路421-1的输出端nout2。逻辑电路424-1包括第一端ln1、第二端ln2、输入端ln3及输出端ln41。逻辑电路424-1的第一端ln1耦接控制电路421-1的接收端rn1,第二端ln2耦接控制电路421-1的接收端rn2,输入端ln3耦接触发电路422-1的输出端kn3,输出端ln41耦接控制电路421-1的输出端nout2。逻辑电路424-1可包括反相器inv1。反相器inv1的第一端耦接逻辑电路424-1的第一端ln1,第二端耦接逻辑电路424-1的第二端ln2,输入端耦接逻辑电路424-1的输入端ln3,输出端耦接逻辑电路424-1的输出端ln41。反相器inv1可由晶体管im1及im2来实现。晶体管im1可为pmos晶体管、pfet或pnp型bjt,晶体管im2可为nmos晶体管、nfet或npn型bjt。换言之,当晶体管m2是以pmos晶体管、pfet或pnp型bjt实现时,则可省略设置逻辑电路424-1,并由触发电路422-1来对晶体管m2提供适当位准的控制信号cs1。

19.另一方面,图4是以输入电压vin由控制电路421-1的内部电路提供作为举例说明。控制电路421-1还包括电压产生电路426。电压产生电路426包括第一端vgn1、第二端vgn2及输出端vgn3。电压产生电路426的第一端vgn1耦接控制电路421-1的接收端rn1,第二端vgn2耦接电压端vn2,输出端vgn3耦接侦测电路det1的输入端,用以提供输入电压vin。电压端

vn2用以提供电压v2,电压v2可为接地电压或其它具有低位准的固定电压。

20.图5是绘示图4中电压产生电路426的电路示意图。图5(a)电压产生电路426-1的第一端vgn1、第二端vgn2与输出端vgn3分别对应图4电压产生电路426的第一端vgn1、第二端vgn2与输出端vgn3。电压产生电路426-1包括分压电路vd1。分压电路vd1包括电阻r2及r3。电阻r2及r3分别包括第一端及第二端。电阻r2的第一端耦接电压产生电路426-1的第一端vgn1,第二端耦接电压产生电路426-1的输出端vgn3。电阻r3的第一端耦接电阻r2的第二端,第二端耦接电压产生电路426-1的第二端vgn2。应用本实施例者可藉由适度调整电阻r2及r3的阻值,或是,可藉由选择具有适当阻值的电阻r2及r3,以使电压产生电路426-1于其输出端vgn3提拱适当的输入电压vin。

21.图5(b)电压产生电路426-2的第一端vgn1、第二端vgn2与输出端vgn3分别对应图4电压产生电路426的第一端vgn1、第二端vgn2与输出端vgn3。电压产生电路426-2包括钳位(clamp)电路cl1。钳位电路cl1包括上拉电路pu2及二极管d1。上拉电路pu2及二极管d1分别包括第一端及第二端。上拉电路pu2的第一端耦接电压产生电路426-2的第一端vgn1,第二端耦接电压产生电路426-2的输出端vgn3。本实施例的上拉电路pu2可以电阻r4实现。二极管d1的第一端耦接上拉电路pu2的第二端,第二端耦接电压产生电路426-2的第二端vgn2。应用本实施例者可藉由选择具有适当阻值的电阻r4以及具有适当顺向偏压(forward bias)的二极管d1以使电压产生电路426-2于其输出端vgn3提拱适当的输入电压vin。此外,虽然本实施例采用单个二极管d1来实现钳位电路cl1,应用本实施例亦可用多个二极管相互串联来实现钳位电路cl1。

22.图6是绘示图3电压调节器300在运作时的选定信号的波形图。请同时参见图3、图4与图6,以便说明电压调节器300的运作方式。图6的横轴为时间,纵轴为电压值。在启动时点t0时,电压v1从0v迅速提升至接近6v,以为电压调节器300供电。晶体管m1的初始状态可设定为截止状态,因此操作信号pg在启动时点t0朝高位准提升。然而,此时晶体管m3的第二端上的电压小于输入电压vin与晶体管m3的导通电压的差值,控制电路421-1便可判断电压调节器300操作在启动模式tp1。据此,晶体管m3为导通状态,使得逻辑电路424-1的输入端ln3被拉低至接近预定电压vpr而具有低位准,逻辑电路424-1的输出端ln41则提供具有高位准的控制信号cs1,从而导通晶体管m2。晶体管m1的控制端gn与预定电压端vprn可透过导通的晶体管m2而电性耦接,换句话说,晶体管m1的控制端gn被短路至预定电压端vprn。因此,原本应该继续朝高位准提升的操作信号pg迅速被拉低至接近预定电压vpr的位准,进而迅速导通晶体管m1。另一方面,输出电压vout的位准对应操作信号pg迅速下降的位准而由0v迅速的提升,于是,电压调节器300可在较短的时间内将输出电压vout提升到所需的电压值。也就是说,在启动模式tp1下,藉由主驱动电路110及次驱动电路320或320-1共同驱动晶体管m1,可缩短输出电压vout提升到所需的电压值的时间。值得注意的是,由于本实施例的预定电压vpr设定成与输出电压vout相同,因此于启动模式tp1内,操作信号pg的位准会跟随输出电压vout的位准变化,图6中操作信号pg的曲线会部分与输出电压vout的曲线重合。此外,操作信号pg因迅速被拉低至低位准也较不易产生振荡。不仅如此,电压v1相当于晶体管m1的第一端sn上的电压,输出电压vout相当于晶体管m1的第二端dn上的电压,由图6可得知,快速上升的输出电压vout的位准将使晶体管m1承受较小的电压差,减少晶体管m1损坏的风险。

23.当晶体管m3的第二端上的电压vpr大于输入电压vin与晶体管m3的导通电压的差值时,控制电路421-1便可判断电压调节器300操作在正常模式tp2(亦即电压调节器300进入工作时点t1)。据此,晶体管m3为截止状态,使得逻辑电路424-1的输入端ln3被拉升至接近电压v1而具有高位准,逻辑电路424-1的输出端ln41则提供具有低位准的控制信号cs1,从而截止晶体管m2。晶体管m1的控制端gn与预定电压端vprn之间的电性耦接可透过截止的晶体管m2而被断开。也就是说,在正常模式tp2下,是由主驱动电路110驱动晶体管m1,次驱动电路320或320-1将不易影响主驱动电路110与晶体管m1之间的控制回路(control loop)。由此可见,电压调节器300不仅可透过适当设计主驱动电路110而具有低功率的特性,还可透过设置次驱动电路320或320-1以达到在较短时间内将输出电压vout调节至所需的电压值的目的。简言之,电压调节器300可具有快速启动的特性。

24.在图4中,晶体管m2包括第一端、第二端、第三端及控制端。晶体管m2的第一端例如是漏极端,第二端例如是源极端,第三端例如是基体端(bulk),控制端例如是栅极端。晶体管m2的第一端耦接开关410的第一端,第二端耦接开关410的第二端,第三端可耦接晶体管m2的第二端(亦即晶体管m2的第三端和第二端被短路在一起)或电性浮接(electrically floating),控制端耦接开关410的控制端。本实施例以晶体管m2的第三端耦接其第二端为例进行说明。在此情况下,晶体管m2的第一端和第三端之间会存在寄生二极管(parasitic diode)pd1,寄生二极管pd1的阳极与阴极分别连接晶体管m2的第三端与第一端。详细来说,请同时参见图3与图4,当电压调节器300操作在正常模式,例如输出电压vout已调节至所需的电压值,假使负载此时为重载状态,负载将汲取更多的输出电流io,造成输出电压vout的电压值降低,电压调节器300则会将操作信号pg调节至较低的电压值,以提供更多的输出电流io。虽然晶体管m2在正常模式为截止状态,然而,当输出电压vout的电压值与操作信号pg的电压值的差值大于晶体管m2中的寄生二极管pd1的导通电压时,可能会使晶体管m2中的寄生二极管pd1形成导通路径,导致部分的输出电流io不当地从输出端nout经由晶体管m2中的寄生二极管pd1泄漏(leak)至晶体管m1的控制端gn,因而抬高操作信号pg的电压值,影响主驱动电路110驱动晶体管m1的能力。

25.为改善此种情况,本实施例的次驱动电路还可包括pn结(pn junction)组件。pn结组件可与晶体管m2中的寄生二极管pd1以背对背(back to back)方式串接于次驱动电路的第一端sdn1与第二端sdn2之间。举例来说,背对背方式可为pn结组件的其中一端耦接于寄生二极管pd1的相同极性端。本实施例可由多种电路结构来实现pn结组件,以下逐一说明。图7是本发明的第一实施例中另一次驱动电路320-2的电路示意图。次驱动电路320-2与320-1不同之处在于,次驱动电路320-2还包括pn结组件728-1。pn结组件728-1包括第一端及第二端。pn结组件728-1的第一端耦接次驱动电路320-2的第一端sdn1,第二端耦接晶体管m2的第一端。pn结组件728-1可包括二极管或晶体管,图7是以pn结组件728-1包括二极管d2作为举例说明。二极管d2的阳极耦接pn结组件728-1的第一端,阴极耦接pn结组件728-1的第二端。进一步而言,二极管d2的阴极耦接于寄生二极管pd1的阴极,二极管d2与寄生二极管pd1是以背对背方式串接于次驱动电路320-2的第一端sdn1及第二端sdn2之间。如此一来,可藉由二极管d2来提高晶体管m2的导通电压,以使输出电流io不易经由晶体管m2中的寄生二极管pd1泄漏至晶体管m1的控制端gn。在一些实施例中,可使用以二极管形式连接(diode connected)的晶体管取代二极管d2。

26.图8是本发明的第一实施例中另一次驱动电路320-3的电路示意图。次驱动电路320-3与320-2不同之处在于,次驱动电路320-3中的控制电路421-2的电路结构以及pn结组件728-2的电路结构。控制电路421-2与421-1所包含的组件相似,惟控制电路421-2还包括输出端nout3。触发电路422-1的输出端kn3还耦接控制电路421-2的输出端nout3。

27.另一方面,图8中pn结组件728-2包括晶体管m4。晶体管m4可由pmos晶体管、pfet或pnp型bjt来实现。晶体管m4包括第一端、第二端、第三端及控制端。晶体管m4的第一端耦接pn结组件728-2的第一端,第二端耦接pn结组件728-2的第二端,第三端耦接晶体管m4的第二端或电性浮接,控制端耦接控制电路421-2的输出端nout3。也就是说,晶体管m4的控制端透过控制电路421-2的输出端nout3耦接触发电路422-1的输出端kn3。如此一来,便可由触发电路422-1来对晶体管m4的控制端提供适当位准的信号,以控制晶体管m4的导通状态。特别说明的是,晶体管m2与m4于启动模式皆为导通状态,且于正常模式皆为截止状态,惟控制信号cs1的位准与晶体管m4的控制端所接收到的信号的位准为反相。

28.本实施例以晶体管m4包括pmos晶体管且晶体管m4的第三端耦接其第二端作为举例说明。晶体管m4的第一端例如是源极端,第二端例如是漏极端,第三端例如是基体端,控制端例如是栅极端。在此情况下,晶体管m4的第一端和第三端之间会存在寄生二极管pd2,寄生二极管pd2的阳极与阴极分别连接晶体管m4的第一端与第三端。进一步而言,寄生二极管pd2的阴极耦接于寄生二极管pd1的阴极,寄生二极管pd2与pd1是以背对背方式串接于次驱动电路320-3的第一端sdn1及第二端sdn2之间。如此一来,可藉由寄生二极管pd2来提高晶体管m2的导通电压,以使输出电流io不易经由晶体管m2中的寄生二极管pd1泄漏至晶体管m1的控制端gn。特别说明的是,本发明不限制晶体管m4与m2的工艺类型(如,晶体管m4与m2可以绝缘层上硅(silicon on insulator,soi)工艺制造或是以基底互补式金氧半(bulk complementary metal-oxide-semiconductor,bulk cmos)工艺制造),只要可以达到晶体管m4中的寄生二极管与晶体管m2中的寄生二极管是以背对背方式串接于次驱动电路320-3的第一端sdn1与第二端sdn2之间的功效即可。例如,可透过将晶体管m4的第三端耦接其第二端或电性浮接及/或将晶体管m2的第三端耦接其第二端或电性浮接的方式达到上述的功效。在一些实施例中,当晶体管m2是以soi工艺制造或是以bulk cmos工艺制造,且晶体管m2的第三端为电性浮接时,则可省略设置pn结组件728-1或728-2。

29.图9是本发明的第二实施例的一种电压调节器900的模块图。电压调节器900与300不同之处在于,电压调节器900还包括分压电路990。分压电路990包括第一端n990-1、第二端n990-2及输出端n990-3。分压电路990的第一端n990-1耦接电压调节器900的输出端nout,第二端n990-2耦接电压端vn2,输出端n990-3耦接主驱动电路110的输入端in1。分压电路990可由串接的电阻r5及r6来实现。藉此,应用本实施例者可依其需求适度调整电阻r5及r6的阻值(如,调整电阻r5及r6之间的阻值比例关系),从而调整输出电压vout的电压值。

30.另一方面,次驱动电路320-4与次驱动电路320-3不同之处在于,控制电路421-3中的逻辑电路424-2的电路结构以及控制电路421-3的输出端nout3的连结方式。图9中,逻辑电路424-2还包括输出端ln42及反相器inv2。逻辑电路424-2的输出端ln42耦接控制电路421-3的输出端nout3。反相器inv2的第一端耦接逻辑电路424-2的第一端ln1,第二端耦接逻辑电路424-2的第二端ln2,输入端耦接反相器inv1的输出端,输出端耦接逻辑电路424-2的输出端ln42。反相器inv2可由晶体管im3及im4来实现。晶体管im3可为pmos晶体管、pfet

或pnp型bjt,晶体管im4可为nmos晶体管、nfet或npn型bjt。此外,在本实施例中,晶体管m4的控制端耦接控制电路421-3的输出端nout3,如此一来,便可由反相器inv2来对晶体管m4的控制端提供适当位准的信号,以控制晶体管m4的导通状态,并由反相器inv1来对晶体管m2的控制端提供适当位准的控制信号cs1,以控制晶体管m2的导通状态。不仅如此,透过设置反相器inv2还可提高驱动晶体管m4的速度。应用本实施例者亦可将图9的次驱动电路320-4应用到符合本发明实施例的相应电压调节器中。例如,图3电压调节器300中的次驱动电路320可由次驱动电路320-4实现。

31.图9电压调节器900中的主驱动电路110包括误差放大器(error amplifier)eamp。主驱动电路110的输入端in1为误差放大器eamp的非反相输入端,输入端in2为误差放大器eamp的反相输入端,输出端out1为误差放大器eamp的输出端。

32.当图3电压调节器300中的次驱动电路320是由图4、图7、图8或图9的次驱动电路320-1~320-4来实现时,或者,当图9电压调节器900中的次驱动电路320-4是由图4、图7或图8的次驱动电路320-1~320-3来实现时,电压调节器300或900可根据输出电压vout、预定电压vpr或电压v1来选择性地操作在启动模式或正常模式。然而,在一些实施例中,电压调节器300或900亦可根据所设定的延迟时间(delay time)来选择性地操作在启动模式或正常模式,以下逐一说明。

33.图10是本发明的第一实施例或第二实施例中另一次驱动电路320-5的电路示意图。次驱动电路320-5与320-1不同之处在于,次驱动电路320-5中的控制电路421-4的电路结构。当图3或图9电压调节器300或900中的次驱动电路320或320-4是由图10的次驱动电路320-5来实现时,电压调节器300或900可根据所设定的延迟时间来选择性地操作在启动模式或正常模式。次驱动电路320-5可根据所设定的延迟时间来判断电压调节器300或900的操作模式,从而选择性地将晶体管m1的控制端gn与预定电压端vprn电性耦接或电性断开。

34.在此说明控制电路421-4的详细电路结构。控制电路421-4包括触发电路422-2。触发电路422-2包括第一端kn1、第二端kn2及输出端kn3。触发电路422-2的第一端kn1耦接控制电路421-4的接收端rn1,第二端kn2耦接控制电路421-4的接收端rn2,输出端kn3耦接控制电路421-4的输出端nout2。于一些实施例中,应用本实施例者可依其需求设计触发电路422-2的第二端kn2耦接控制电路421-4的接收端rn2或是电压端vn2。

35.触发电路422-2包括延迟电路del1。延迟电路del1包括第一端、第二端及输出端。延迟电路del1的第一端耦接触发电路422-2的第一端kn1,第二端耦接触发电路422-2的第二端kn2,输出端耦接触发电路422-2的输出端kn3。延迟电路del1包括电阻r7及电容c1。电阻r7及电容c1分别包括第一端及第二端。电阻r7的第一端耦接延迟电路del1的第一端,第二端耦接延迟电路del1的输出端。电容c1的第一端耦接电阻r7的第二端,第二端耦接延迟电路del1的第二端。应用本实施例者可依其需求设计电阻r7的阻值及电容c1的电容值,从而设定延迟时间的长度。

36.图10是以晶体管m2为nmos晶体管作为举例说明。在此情况下,控制电路421-4还包括逻辑电路424-1,以对晶体管m2提供适当位准的控制信号cs1。触发电路422-2的输出端kn3透过逻辑电路424-1耦接控制电路421-4的输出端nout2。逻辑电路424-1的电路结构与图4的逻辑电路424-1相近似,在此不予赘述。

37.本实施例的控制电路421-4可根据所设定的延迟时间来判断电压调节器300或900

的操作模式,并据以输出控制信号cs1。详细来说,控制电路421-4可透过延迟电路del1来判断电压调节器300或900的操作模式,并据以输出控制信号cs1。进一步而言,由于延迟电路del1中电阻r7的阻值及电容c1的电容值与延迟时间有关,因此,可藉由延迟电路del1的输出端上的电压与所设定的阈值之间的关系来判断电压调节器300或900的操作模式。特别说明的是,当延迟电路del1的输出端上的电压小于阈值时(即,未达所设定的延迟时间),控制电路421-4可判断电压调节器操300或900操作在启动模式;当延迟电路del1的输出端上的电压大于阈值时(即,已达所设定的延迟时间),控制电路421-4可判断电压调节器300或900操作在正常模式。本实施例的阈值可设定为逻辑电路424-1的转态电压(transition voltage)。应用本实施例者也可透过改变触发电路422-2的电路结构来调整阈值。

38.以下说明控制电路421-4的运作方式。图10是将预定电压vpr设定成与输出电压vout相同作为举例说明。在启动时点时,电压v1为电压调节器300或900供电,且电容c1开始对初始电压为0v的预定电压vpr充电,在本实施例中也即是,电容c1开始对初始电压为0v的输出电压vout充电。因此,延迟电路del1的输出端上的电压小于阈值,控制电路421-4可判断电压调节器300或900操作在启动模式。据此,逻辑电路424-1的输入端ln3被拉低至接近预定电压vpr而具有低位准,逻辑电路424-1的输出端ln41则提供具有高位准的控制信号cs1,从而导通晶体管m2。经过所设定的延迟时间,预定电压vpr及输出电压vout的位准已提升至接近所需的电压值。因此,延迟电路del1的输出端上的电压大于阈值,控制电路421-4可判断电压调节器300或900操作在正常模式。据此,逻辑电路424-1的输入端ln3被拉升至接近电压v1而具有高位准,逻辑电路424-1的输出端ln41则提供具有低位准的控制信号cs1,从而截止晶体管m2。

39.图11是本发明的第一实施例或第二实施例中另一次驱动电路320-6的电路示意图。次驱动电路320-6与320-5不同之处在于,次驱动电路320-6还包括pn结组件728-2以及次驱动电路320-6中控制电路421-5的电路结构。图11中的pn结组件728-2、控制电路421-5的输出端nout3链接方式、控制电路421-5中逻辑电路424-2的电路结构及功用与图9的pn结组件728-2、控制电路421-3的输出端nout3、逻辑电路424-2相近似,在此不予赘述。在一些实施例中,pn结组件728-2可包括二极管,在此情况下则可省略逻辑电路424-2中的反相器inv2,可参考图7的电路结构及相关叙述,在此不予赘述。在另一些实施例中,晶体管m4的控制端也可透过控制电路421-5的输出端nout3耦接触发电路422-2的输出端kn3,在此情况下亦可省略逻辑电路424-2中的反相器inv2,以由触发电路422-2来对晶体管m4的控制端提供适当位准的信号,从而控制晶体管m4的导通状态,可参考图8的电路结构及相关叙述,在此不予赘述。也就是说,图11的电路结构可藉由pn结组件728-2来提高晶体管m2的导通电压,以使输出电流io不易经由晶体管m2中的寄生二极管pd1泄漏至晶体管m1的控制端gn。

40.基于上述,电压调节器不仅可透过适当设计主驱动电路而具有低功率的特性,当电压调节器操作在启动模式时,本实施例可透过主驱动电路及次驱动电路来迅速提升输出电压的电压值,以使电压调节器具有快速启动的特性,并能减少晶体管损坏的风险。另一方面,当电压调节器操作在正常模式时,本实施例还可透过次驱动电路将晶体管的控制端与预定电压端电性断开,从而使主驱动电路与晶体管的间的控制回路不易受到次驱动电路的影响。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1