一种可穿戴立体眼镜控制电路的制作方法

[0001]

本实用新型涉及vr眼镜技术领域,更具体地说,涉及一种可穿戴立体眼镜控制电路。

背景技术:

[0002]

vr眼镜是利用头戴式显示设备将人的对外界的视觉、听觉封闭,引导用户产生一种身在虚拟环境中的感觉,其显示原理是左右眼屏幕分别显示左右眼的图像,人眼获取这种带有差异的信息后在脑海中产生立体感。目前,立体眼镜控制电路在控制mosfet管的导通及反向恢复的损耗较大,使得左右眼屏幕的画面出现眩晕,造成产品的使用体验感较差。

[0003]

因此,如何降低mosfet管的导通及反向恢复的损耗成为本领域技术人员亟需解决的技术问题。

技术实现要素:

[0004]

本实用新型要解决的技术问题在于,针对现有技术的上述mosfet管的导通及反向恢复的损耗较大的缺陷,提供一种调节同步且画面质量较佳的可穿戴立体眼镜控制电路。

[0005]

本实用新型解决其技术问题所采用的技术方案是:构造一种可穿戴立体眼镜控制电路,具备:pwm控制器,其配置于控制电路内,用于产生并输出pwm 脉冲信号;

[0006]

延迟线,其输入端耦接于所述pwm控制器的输出端,用于接收所述pwm 脉冲信号;

[0007]

微控制器,其用于输出控制信号;

[0008]

乘法器,其输入端与所述微控制器的输出端连接,其用于接收所述控制信号;

[0009]

计数器,其输入端与所述乘法器的输出端连接,其用于接收经所述乘法器处理后的所述控制信号;

[0010]

当所述微控制器输出的所述控制信号为高电平时,所述高电平用于触发 mosfet管导通;

[0011]

当所述微控制器输出的所述控制信号为低电平时,所述低电平用于控制所述mosfet管关断延迟。

[0012]

在一些实施方式中,所述乘法器包括第一乘法器、第二乘法器及第三乘法器,

[0013]

所述第一乘法器的输入端与所述微控制器的输出端连接,其用于接收所述控制信号,所述第一乘法器的输出端与所述计数器的输入端连接;

[0014]

所述第二乘法器的输入端与所述微控制器的输出端连接,其用于接收所述控制信号,

[0015]

所述第三乘法器的一输入端与所述第二乘法器的输出端连接,所述第三乘法器的输出端与所述mosfet管的栅极连接。

[0016]

在一些实施方式中,还包括低速比较器及高速比较器,

[0017]

所述低速比较器及所述高速比较器的输入端分别与微控制器的输出端连接,

[0018]

所述低速比较器的输出端耦接于所述第二乘法器的输入端,

[0019]

所述高速比较器的输出端耦接于所述第三乘法器的一输入端。

[0020]

在一些实施方式中,还包括与门电路,所述与门电路的一输入端与所述第二乘法器的输出端连接,

[0021]

所述与门电路的另一输入端与所述高速比较器的输出端连接,

[0022]

所述与门电路的输出端与所述第三乘法器的一输入端连接。

[0023]

在一些实施方式中,还包括非门电路,所述非门电路的输入端耦接于所述延迟线的输出端,所述非门电路的输出端与所述第三乘法器的另一输入端连接。

[0024]

在本实用新型所述可穿戴立体眼镜控制电路中,包括用于产生并输出 pwm脉冲信号的pwm控制器、用于输出控制信号的微控制器,当微控制器输出的控制信号为高电平时,高电平用于触发mosfet管导通;当微控制器输出的控制信号为低电平时,低电平用于控制mosfet管关断延迟。与现有技术相比,微控制器能够根据元件状态(mosfet管)的变化以调节同步整流mosfet管中的不可控的电容值,以及通过时间的延迟及温度变化对 mosfet管阈值的影响根据反馈环进行校正,进而可有效解决mosfet管的导通及反向恢复的损耗较大的问题。

附图说明

[0025]

下面将结合附图及实施例对本实用新型作进一步说明,附图中:

[0026]

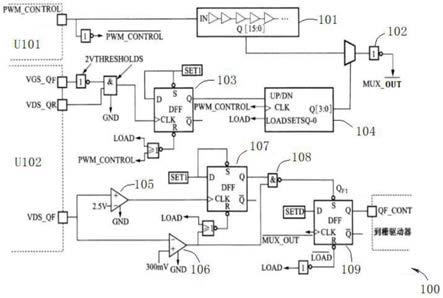

图1是本实用新型提供可穿戴立体眼镜控制电路一实施例的电路原理图;

[0027]

图2是本实用新型提供可穿戴立体眼镜控制电路一实施例可调延迟电路图;

[0028]

图3a是本实用新型提供可穿戴立体眼镜控制电路一实施例vr的开启波形图;

[0029]

图3b是本实用新型提供可穿戴立体眼镜控制电路另一实施例vr的开启波形图;

[0030]

图4a是本实用新型提供可穿戴立体眼镜控制电路一实施例vr的关断波形图;

[0031]

图4b是本实用新型提供可穿戴立体眼镜控制电路另一实施例vr的关断波形图;

[0032]

图5是本实用新型提供可穿戴立体眼镜控制电路一实施例vr预锁存波形图。

具体实施方式

[0033]

为了对本实用新型的技术特征、目的和效果有更加清楚的理解,现对照附图详细说明本实用新型的具体实施方式。

[0034]

如图1-图5所示,在本实用新型的可穿戴立体眼镜控制电路的第一实施例中,可穿戴立体眼镜控制电路100包括pwm控制器u101、微控制器u102、延迟线101、乘法器(对应103、107及109)及计数器104。

[0035]

其中,pwm控制器u101配置于控制电路100内,其用于产生并输出pwm 脉冲信号,并将该pwm脉冲信号输出至延迟线101。

[0036]

需要说明的是,pwm脉冲信号(pulse width modulation)是一种模拟控制方式,根据相应载荷的变化来调制晶体管基极或mos管栅极的偏置,来实现晶体管或mos管导通时间的改变,从而实现开关稳压电源输出的改变。

[0037]

延迟线101是指—在电压信号传输过程中可提供一已知延迟的装置。如声波延迟线,即为利用声波在固体内传播之速度十分小于光速的特性来做电压信号的延迟。声波延迟装置通常使用于雷达或电脑内之信号处理,利用此延迟装置,波形信号可以储存一段短

时间后再撷取出来做其他的显示或处理。

[0038]

延迟线101的输入端耦接于pwm控制器u101的输出端,其用于接收 pwm脉冲信号并对输入pwm脉冲信号进行延迟几个纳秒的处理。

[0039]

微控制器u102配置于控制电路100内,其用于产生并输出控制信号(对应高电平或低电平信号),并将产生的控制信号输出至乘法器(对应103、107 及109)。

[0040]

乘法器(对应103、107及109)是一种完成两个互不相关的模拟信号相乘作用的电子器件,其不仅作为乘法、除法、乘方和开方等模拟运算的主要基本单元,而且还广泛用于电子通信系统作为调制、解调、混频、鉴相和自动增益控制。

[0041]

乘法器(对应103)的输入端(对应clk端)与微控制器u102的一输出端(对应vgs-qf端)连接,其用于接收微控制器u102输出的控制信号,将输入的控制信号进行相乘或运算处理后,再输出至计数器104。

[0042]

计数器104是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能。

[0043]

计数器104的输入端(对应up/dn端)与乘法器103的输出端(对应q 端)连接,其用于接收经乘法器103处理后的控制信号。

[0044]

当微控制器u102输出的控制信号为高电平时,该高电平用于触发 mosfet管(即场效应管)导通,当微控制器u102输出至的控制信号为低电平时,低电平用于控制mosfet管关断延迟。

[0045]

示例性地,为减小mosfet管的导通损耗及反向恢复损耗,微控制器u102 将根据元件状态(对应mosfet管)的变化来特别调节同步整流mosfet管中的不可控的电容通过时间的延迟及温度变化对mosfet管阈值的影响根据反馈环进行校正。

[0046]

为控制栅极驱动的时间,如图2中所示的可调延迟的电路,从in到out 的延迟控制由微控制器u102来执行,微控制器u102加到乘法器的地址输入上。相反地,如果微控制器u102设置全部为0,则从in到out的延迟就为 0,即没有延迟。几种不同的延迟时间可以设定,给出几种开启延迟时间,关闭延迟时间,或对称的开启及关断延迟。

[0047]

如图3a及图3b所示,调节关断延迟,用一个或门在一个大约2v输入阈值,来检测vr的栅源电压和漏源电压两者是否都为低电平时的状态,从或门出来的高电平指示微控制器u102,告之延迟时间太长,微控制器u102就会在下一个开关周期减少延迟。

[0048]

或门输出被锁存、倒相并送至开启延迟计数器104的up/down输入端,该信号告诉计数器104向上记数或向下记数;若或门输出为高电平,则计数器 104向下记数,减少延迟时间。

[0049]

而或门为低电平输出时,计数器104向上记数,则增加延迟时间,计数器 104有效地保持该延迟信息给下一个工作周期,反馈环会调节开启延迟使之缩短,直到或门没有更长的输出脉冲,当计数器104工作在恒定负载和线路电压时,对下一个周期的开启延迟将稍微有些加长,或门将给出高输出脉冲,延迟将会缩短,在这种方式中,控制电路会在两个延迟时间之间抖动,一个长一些,另一个就会接近最佳状态。

[0050]

在一些实施方式中,乘法器包括第一乘法器103、第二乘法器107及第三乘法器109,其中,第一乘法器103的输入端(对应clk端)与微控制器u102 的输出端(对应vgs-qf端)连接,其用于接收控制信号,第一乘法器103 的输出端(对应q端)与计数器104的输入端

(对应up/dn端)连接,计数器104用于接收第一乘法器103输出的控制信号。

[0051]

第二乘法器107的输入端(对应clk端)与微控制器u102的输出端(对应vds-qf端)连接,其用于接收控制信号。

[0052]

第三乘法器109的一输入端(对应s端)与第二乘法器107的输出端(对应q端)连接,第三乘法器109的输出端(对应q端)与mosfet管的栅极 (对应qf-cont端)连接。

[0053]

示例性地,如图4a示出,当延迟设置太短时电路的工作状态;图4b示出最佳延迟状态;

[0054]

由于在vr导通中,关断延迟在某一值处于抖动状态,这就是太长以及最佳值的两个状态。

[0055]

开启延迟及关断延迟可否设置的短些,这是否会造成交叉导通,问题在于仔细地研究比较器的特性,及延迟线的每个元件的延迟,比较器仅能响应差分输入电压,此电压仅在转换间隔结点上有足够的时间总量才会存在。

[0056]

在一些实施方式中,还包括低速比较器105及高速比较器106,其中,低速比较器105及高速比较器106的输入端分别与微控制器u102的输出端(对应vds-qf端)连接,其用于接收微控制器u102输出的控制信号。

[0057]

低速比较器105的输出端耦接于第二乘法器107的输入端(对应clk端),第二乘法器107用于接收经低速比较器105处理后的控制信号。

[0058]

高速比较器106的输出端耦接于第三乘法器109的一输入端(对应s端),第三乘法器109用于接收经高速比较器106处理后的控制信号。

[0059]

具体而言,在控制驱动qf(对应第三乘法器109的s端)的执行时,在微控制器u102复位后即将qf开启,它独立于pwm脉冲信号的上升沿和下降沿,它不同于回流的mosfet管。此处,目标只不过是调节pwm控制器 u101的脉冲信号的上升沿及下降沿的时间,以减少高速比较器106的导通时间,并使之最小化。

[0060]

在一些实施方式中,还包括与门电路108,其中,与门电路108是执行“与”运算的基本逻辑门电路,其有多个输入端,一个输出端。当所有的输入同时为高电平(逻辑1)时,输出才为高电平,否则输出为低电平(逻辑0)。

[0061]

具体的,与门电路108的一输入端与第二乘法器107的输出端(对应q 端)连接,与门电路108的另一输入端与高速比较器106的输出端连接,与门电路108的输出端与第三乘法器109的一输入端(对应s端)连接。

[0062]

在一些实施方式中,还包括非门电路102,即,当其输入端为高电平(逻辑1)时输出端为低电平(逻辑0),当其输入端为低电平时输出端为高电平。

[0063]

具体的,非门电路102的输入端耦接于延迟线101的输出端,非门电路 102的输出端(对应mux-out端)与第三乘法器109的另一输入端(对clk 端)连接。

[0064]

上面结合附图对本实用新型的实施例进行了描述,但是本实用新型并不局限于上述的具体实施方式,上述的具体实施方式仅仅是示意性的,而不是限制性的,本领域的普通技术人员在本实用新型的启示下,在不脱离本实用新型宗旨和权利要求所保护的范围情况下,还可做出很多形式,这些均属于本实用新型的保护之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1