功能单元及控制装置的制作方法

功能单元及控制装置

1.本技术是基于2015年11月5日提出的中国国家申请号201580084288.8(pct/jp2015/081232)申请(功能单元及控制装置)的分案申请,以下引用其内容。

技术领域

2.本发明涉及与其他单元同步的功能单元及控制装置。

背景技术:

3.fa(factory automation)领域的设备通常是将多个种类的仪器组合而实现的。构成fa领域的设备的多个仪器,与整合了控制处理及信息处理的控制装置即可编程控制器连接。可编程控制器在fa领域的设备中分散配置。分散配置的可编程控制器基于从通信用总线以恒定的同步周期输入的触发信号而同步(参照专利文献1)。

4.专利文献1:日本特开2006

‑

285885号公报

技术实现要素:

5.关于构成可编程控制器的功能单元,提出了能够以比触发信号的同步周期短的控制周期进行功能处理的功能单元。但是,在专利文献1中示出的可编程控制器存在下述问题,即,功能单元在一个同步周期内仅进行一次功能处理,因此不能有效利用功能单元所具有的高速功能处理性能。并且,在与cpu单元连接有多个作为功能单元的输入单元和输出单元的情况下,针对该问题还存在下述解决方法,即,使用在最初的同步周期输入的触发信号而开始同步控制,之后按照搭载于各单元的内部控制处理器的控制周期而进行高速控制,但还产生新的问题,即,在每个内部控制处理器会分别产生控制周期的波动,因此在进行长时间的控制的情况下,该波动终究会变成不能忽视的大小。

6.本发明就是鉴于上述问题而提出的,其目的在于得到能够有效利用高速功能处理性能,且能够抑制控制周期的波动的功能单元。

7.为了解决上述问题,达成目的,本发明是基于从外部以同步周期输入的触发信号而与其他单元同步的功能单元。功能单元的特征在于,具有功能处理部,该功能处理部基于触发信号,以比同步周期短的控制周期实施功能处理,且在一个同步周期内反复实施所述功能处理而生成处理结果。功能单元的特征在于,具有输出控制部,该输出控制部基于触发信号,将功能处理部的处理结果汇总地输出。

8.发明的效果

9.本发明涉及的功能单元取得下述效果,即,能够有效利用高速功能处理性能,且能够抑制控制周期的波动。

附图说明

10.图1是表示控制系统的结构的图,该控制系统具有实施方式1涉及的控制装置。

11.图2是表示实施方式1涉及的控制装置的硬件结构的图。

12.图3是表示实施方式1涉及的控制装置的输入系统单元的硬件结构的图。

13.图4是表示实施方式1涉及的控制装置的输入系统单元的共享存储器的存储区域的图。

14.图5是表示实施方式1涉及的控制装置的动作的一个例子的时序图。

15.图6是表示实施方式1涉及的控制装置的输入系统单元的功能处理单元的处理的一个例子的流程图。

16.图7是表示实施方式1涉及的控制装置的输入系统单元的触发控制次数的设定画面的图。

17.图8是表示实施方式2涉及的控制装置的输出系统单元的硬件结构的图。

18.图9是表示实施方式2涉及的控制装置的输出系统单元的共享存储器的存储区域的图。

19.图10是表示实施方式2涉及的控制装置的动作的一个例子的时序图。

20.图11是表示实施方式2涉及的控制装置的输出系统单元的功能处理单元的处理的一个例子的流程图。

21.图12是表示实施方式3涉及的功能单元的硬件结构的图。

22.图13是表示实施方式3涉及的功能单元的动作的一个例子的时序图。

具体实施方式

23.下面,基于附图对本发明的实施方式涉及的功能单元及控制装置详细地进行说明。此外,本发明不限定于该实施方式。

24.实施方式1.

25.图1是表示控制系统的结构的图,该控制系统具有实施方式1涉及的控制装置。控制系统1构成fa(factory automation)领域的设备,如图1所示,具有:多个仪器2、3,它们设置于设备;控制装置5,其与多个仪器2、3连接;以及计算机6,其与控制装置5连接。在实施方式1中,控制系统1具有2个仪器2、3,但不限定于2个。在实施方式1中,仪器2是设置于设备的对流量、压力、浓度或温度进行检测的传感器,仪器3是设置于设备的开关、调节阀、电磁阀、电动机或泵,是实施动作的驱动仪器。

26.计算机6创建由控制装置5执行的控制程序,发送至控制装置5。控制装置5通过执行控制程序,从而对仪器2、3进行控制。在实施方式1中,控制装置5是可编程控制器(programmable controllers(plc))。可编程控制器是由jis(日本工业标准)b 3502:2011规定的。

27.实施方式1涉及的计算机6执行计算机程序,如图1所示,其包含:cpu(central processing unit)61、ram(random access memory)62、rom(read only memory)63、存储装置64、输入装置65、显示装置66、通信接口67。cpu 61、ram 62、rom 63、存储装置64、输入装置65、显示装置66及通信接口67经由总线b相互连接。

28.cpu 61一边将ram 62作为工作区域使用,一边执行存储于rom 63及存储装置64的程序。存储于rom 63的程序是bios(basic input/output system)或uefi(unified extensible firmware interface),但存储于rom 63的程序不限定于bios或uefi。在实施方式1中,存储于存储装置64的程序是操作系统程序及工程设计工具程序,但存储于存储装

置64的程序不限定于操作系统程序及工程设计工具程序。在实施方式1中,存储装置64是ssd或hdd,但存储装置64不限定于ssd或hdd。

29.输入装置65接收来自用户的操作输入。在实施方式1中,输入装置65是键盘或鼠标,但不限定于键盘或鼠标。显示装置66对文字及图像进行显示。在实施方式1中,显示装置66是液晶显示装置,但不限定于液晶显示装置。通信接口67与控制装置5进行通信。

30.图2是表示实施方式1涉及的控制装置的硬件结构的图。控制装置5如图2所示,具有:cpu单元10,其是进行控制程序的处理、执行的处理单元;以及输入系统单元20,其与作为传感器的仪器2连接,且实施对仪器2的检测结果进行加工的功能处理。另外,控制装置5具有:输出系统单元30,其与作为驱动仪器的仪器3连接,且将控制信号发送至仪器3;以及背板40,其将cpu单元10、输入系统单元20、及输出系统单元30相互连接。

31.背板40呈平板状。在背板40的表面部设置有多个对cpu单元10、输入系统单元20及输出系统单元30进行安装的未图示的槽。在背板40的各槽对cpu单元10、输入系统单元20、及输出系统单元30的任意者进行安装。能够适当地对背板40处的cpu单元10、输入系统单元20及输出系统单元30的安装位置进行选择。即使在背板40存在未安装cpu单元10、输入系统单元20及输出系统单元30这些单元的槽,控制装置5也能够动作。

32.背板40具有电路基板41和安装于电路基板41的控制电路42。控制电路42具有:同步时钟生成部42a,其使得cpu单元10、输入系统单元20及输出系统单元30的同步控制能够得以实现,由以图5所示的恒定的同步周期t传递触发信号ts的电路构成;以及通信中继控制部42b,其由用于在cpu单元10、输入系统单元20及输出系统单元30间进行数据收发的电路构成。

33.同步时钟生成部42a通过电气信号线s而与cpu单元10、输入系统单元20及输出系统单元30连接。同步时钟生成部42a以恒定的同步周期t生成用于使同步控制能够得以实现的触发信号ts,将生成的触发信号ts以同步周期t同时发送至cpu单元10、输入系统单元20及输出系统单元30。

34.通信中继控制部42b通过独立于电气信号线s设置的总线通信线l1、l2、l3而与cpu单元10、输入系统单元20及输出系统单元30连接。通信中继控制部42b对cpu单元10、输入系统单元20及输出系统单元30间的数据收发进行中继。

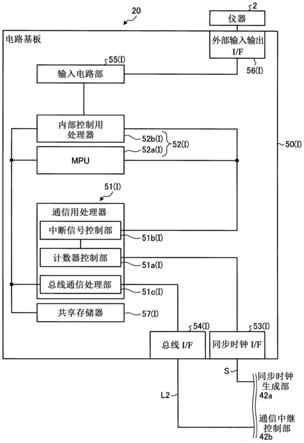

35.在实施方式1中,输入系统单元20是功能单元,输出系统单元30是其他单元。下面,由于cpu单元10、输入系统单元20及输出系统单元30的结构是相同的,因此参照图2,对cpu单元10、输入系统单元20及输出系统单元30的共通的结构进行说明。cpu单元10、输入系统单元20及输出系统单元30如图2所示,具有:电路基板50;通信用处理器51,其安装于电路基板50;以及功能处理单元52,其是安装于电路基板50的功能处理部。

36.cpu单元10、输入系统单元20及输出系统单元30的通信用处理器51经由总线通信线l1、l2、l3及通信中继控制部42b而相互连接。通信用处理器51在cpu单元10、输入系统单元20及输出系统单元30间进行数据收发。另外,通信用处理器51经由电气信号线s与同步时钟生成部42a连接。

37.在实施方式1中,通信用处理器51与在日本专利第5301041号公报中记载的技术同样地,具有由计数器(counter)构成的计数器控制部51a。在计数器控制部51a内置下述电路,即,如果经由电气信号线s接收到触发信号ts,则将计数器的值重置为零的电路。在实施

方式1中,计数器控制部51a在触发信号ts上升的定时将计数器的值重置为零,但也可以在触发信号ts下降的定时将计数器的值重置为零。

38.对于通信用处理器51而言,如果计数器控制部51a所计数的计数器的值成为任意的值,则通信用处理器51生成中断信号,将生成的中断信号发送至功能处理单元52。任意的值是通过cpu单元10的功能处理单元52设定的。中断信号是用于使功能处理单元52执行计算机程序的信号。使cpu单元10、输入系统单元20及输出系统单元30的通信用处理器51生成中断信号的任意的值是相同的。在实施方式1中,任意的值是“零”,但不限定于“零”。在实施方式1中,通信用处理器51与在日本专利第5301041号公报中记载的技术同样地,如果计数器控制部51a所计数的计数器的值成为任意的值,则生成中断信号,但不限定于该技术。

39.通过将使cpu单元10、输入系统单元20及输出系统单元30的通信用处理器51生成中断信号的计数器的任意的值设为相同,同步时钟生成部42a同时地将触发信号ts发送至cpu单元10、输入系统单元20及输出系统单元30的通信用处理器51,从而cpu单元10、输入系统单元20及输出系统单元30的功能处理单元52同步地执行计算机程序。通过通信用处理器51使功能处理单元52同步,从而输入系统单元20基于从输入系统单元20的外部以恒定的同步周期t输入的触发信号ts而与输出系统单元30同步。另外,通过通信用处理器51使功能处理单元52同步,从而输出系统单元30基于从输出系统单元30的外部以恒定的同步周期t输入的触发信号ts而与输入系统单元20同步。在实施方式1中,通信用处理器51由asic(application specific integrated circuit)或fpga(field

‑

programmable gate array)构成,但不限定于asic或fpga。

40.功能处理单元52具有:mpu(micro

‑

processing unit)52a,其存储计算机程序;以及内部控制用处理器52b,其实施硬件处理。如果mpu 52a与内部控制用处理器52b协作而接收到中断信号,则mpu 52a执行所存储的计算机程序。输入系统单元20的内部控制用处理器52b实施对从仪器2输入的检测结果进行加工的功能处理,将通过功能处理生成的处理结果设为在cpu单元10、输入系统单元20及输出系统单元30间收发的数据。输出系统单元30的内部控制用处理器52b实施对经由cpu单元10从计算机6输入的信息即处理对象进行加工的功能处理,将通过功能处理生成的处理结果作为控制信号发送至仪器3。在实施方式1中,内部控制用处理器52b由asic或fpga构成,但不限定于asic或fpga。

41.输入系统单元20及输出系统单元30的功能处理单元52由于具有存储计算机程序的mpu 52a和实施硬件处理的内部控制用处理器52b,因此能够以比触发信号ts的同步周期t短的图5所示的控制周期t1实施内部控制用处理器52b的功能处理,生成内部控制用处理器52b的处理结果。在实施方式1中,对于输入系统单元20及输出系统单元30的功能处理单元52而言,通过通信用处理器51使功能处理单元52同步,从而功能处理单元52基于从外部以恒定的同步周期t输入的触发信号ts,在触发信号ts的同步周期t内,反复实施多次内部控制用处理器52b的功能处理,生成多个处理结果。

42.在实施方式1中,对于输入系统单元20及输出系统单元30的功能处理单元52而言,如果计数器控制部51a所计数的计数器的值成为“零”,则功能处理单元52接收由通信用处理器51发送出的中断信号,内部控制用处理器52b实施功能处理。因此,在实施方式1中,输入系统单元20及输出系统单元30的功能处理单元52将触发信号ts作为起点,反复实施功能处理。另外,在实施方式1中,如果将控制周期设为t1,将输入系统单元20及输出系统单元30

的功能处理单元52在一个同步周期t内实施功能处理的实施次数设为n,则输入系统单元20及输出系统单元30的功能处理单元52满足下面的式1。

43.t>t1

×

n

…

式1

44.下面,在cpu单元10、输入系统单元20及输出系统单元30的各结构要素中的能够确定为cpu单元10的结构要素的结构要素的标号的末尾标记(c),在能够确定为输入系统单元20的结构要素的结构要素的标号的末尾标记(i),在能够确定为输出系统单元30的结构要素的结构要素的标号的末尾标记(o)。图3是表示实施方式1涉及的控制装置的输入系统单元的硬件结构的图。

45.接下来,参照图3,对输入系统单元20的在图2中省略的结构进行说明。输入系统单元20的通信用处理器51(i)在计数器控制部51a(i)的基础上,还具有中断信号控制部51b(i)和总线通信处理部51c(i)。中断信号控制部51b(i)与计数器控制部51a(i)、功能处理单元52(i)连接。中断信号控制部51b(i)接收计数器控制部51a(i)所计数的计数器的值。对于中断信号控制部51b(i)而言,如果计数器控制部51a(i)所计数的计数器的值成为通过cpu单元10的功能处理单元52设定的任意的值,则中断信号控制部51b(i)生成中断信号,发送至功能处理单元52(i)。总线通信处理部51c(i)与功能处理单元52(i)连接。总线通信处理部51c(i)在cpu单元10、输入系统单元20及输出系统单元30间对必要的数据进行收发。

46.输入系统单元20在电路基板50(i)、通信用处理器51(i)、功能处理单元52(i)的基础上,如图3所示,还具有:同步时钟接口53(i),其与同步时钟生成部42a连接;以及总线接口54(i),其与通信中继控制部42b连接。另外,输入系统单元20具有:输入电路部55(i),其与功能处理单元52(i)连接;外部输入输出接口56(i),其与仪器2连接;以及共享存储器57(i)。

47.同步时钟接口53(i)与电气信号线s、计数器控制部51a(i)连接。同步时钟接口53(i)使通信用处理器51(i)的计数器控制部51a(i)接收由同步时钟生成部42a生成的触发信号ts。总线接口54(i)与总线通信线l2、总线通信处理部51c(i)连接。

48.输入电路部55(i)与功能处理单元52(i)的内部控制用处理器52b(i)连接。输入电路部55(i)由a/d(analog/digital)转换器或数字i/o(input/output)构成。外部输入输出接口56(i)与仪器2、输入电路部55(i)连接。作为传感器的仪器2的检测结果经过外部输入输出接口56(i)而由输入电路部55(i)接收。仪器2的检测结果由内部控制用处理器52b(i)接收,由内部控制用处理器52b(i)实施功能处理。

49.共享存储器57(i)是存储数据的存储装置,输入系统单元20的功能处理单元52(i)的mpu 52a(i)、cpu单元10的mpu 52a(c)及输出系统单元30的mpu 52a(o)能够访问该共享存储器57(i)。图4是表示实施方式1涉及的控制装置的输入系统单元的共享存储器的存储区域的图。共享存储器57(i)与通信用处理器51(i)的总线通信处理部51c(i)、功能处理单元52(i)连接。在实施方式1中,共享存储器57(i)由ram构成,但不限定于ram。

50.共享存储器57(i)如图4所示,具有:触发控制次数存储区域57a(i),其是对触发控制次数n进行存储的设定功能部;以及处理结果存储区域57b(i),其存储功能处理单元52(i)的内部控制用处理器52b(i)的处理结果。触发控制次数n是在同步周期t内反复实施功能处理单元52(i)的功能处理的实施次数。在实施方式1中,从在mpu 52a(i)内存储的计算机程序将触发控制次数n写入至触发控制次数存储区域57a(i)。对于触发控制次数存储区

域57a(i)而言,从在mpu 52a(i)内存储的计算机程序写入的触发控制次数n,由功能处理单元52(i)的mpu 52a(i)进行参照。通过由触发控制次数存储区域57a(i)对触发控制次数n进行存储,从而对功能处理单元52(i)在一个同步周期t内实施功能处理的实施次数即触发控制次数n进行设定。在实施方式1中,触发控制次数n是从在mpu 52a(i)内存储的计算机程序写入的,但也可以预先公开触发控制次数存储区域57a(i),经由cpu单元10从计算机6写入。

51.在实施方式1中,通过功能处理单元52(i)的mpu 52a(i)将内部控制用处理器52b(i)的处理结果写入至处理结果存储区域57b(i),但也可以直接通过内部控制用处理器52b(i)写入处理结果。按照内部控制用处理器52b(i)进行处理的顺序将与触发控制次数n对应的量的处理结果写入至处理结果存储区域57b(i)。在实施方式1中,在接收到下一个触发信号ts的定时,由cpu单元10的mpu 52a(c)从处理结果存储区域57b(i)取得所存储的与触发控制次数n对应的量的处理结果,但也可以是输入系统单元20在接收到下一个触发信号ts的定时,将在共享存储器57(i)存储的与触发控制次数n对应的量的处理结果发送至cpu单元10的mpu 52a(c)。此外,处理结果存储区域57b(i)的地址预先设定于cpu单元10内。cpu单元10通过从预先设定的地址区域读取出值而读取与触发控制次数n对应的量的处理结果。

52.对于共享存储器57(i)而言,通过mpu 52a(i)将与触发控制次数n对应的量的处理结果写入至共享存储器57(i),在接收到下一个触发信号ts的定时由cpu单元10的mpu 52a(c)从共享存储器57(i)取得所存储的与触发控制次数n对应的量的处理结果,从而共享存储器57作为基于触发信号ts将功能处理单元52(i)的多个处理结果汇总地输出至输入系统单元20的外部的输出控制部起作用。在实施方式1中,将多个处理结果汇总是指,在触发信号ts输入后直至下一个触发信号ts输入为止的同步周期t内,设为能够由作为外部的cpu单元10取得多个处理结果的状态,或将多个处理结果发送至作为外部的cpu单元10。在实施方式1中,对于共享存储器57(i)的处理结果存储区域57b(i)而言,如果由cpu单元10的mpu 52a(c)取得了所存储的处理结果,则该处理结果存储区域57b(i)被cpu单元10的mpu 52a(c)清空,成为未存储信息的空的状态。

53.另外,在实施方式1涉及的控制装置5中,cpu单元10与图3所示的输入系统单元20,除输入电路部55(i)及外部输入输出接口56(i)以外呈相同的结构。在实施方式1涉及的控制装置5中,输出系统单元30与图3所示的输入系统单元20,除取代输入电路部55(i)而具有由d/a(digital/analog)转换器或数字i/o构成的输出电路部以外呈相同的结构。

54.接下来,基于附图对实施方式1涉及的输入系统单元20及控制装置5的动作的一个例子进行说明。图5是表示实施方式1涉及的控制装置的动作的一个例子的时序图。图6是表示实施方式1涉及的控制装置的输入系统单元的功能处理单元的处理的一个例子的流程图。

55.如图5所示,向实施方式1涉及的控制装置5,以恒定的同步周期t从背板40的同步时钟生成部42a输入触发信号ts。如果输入了触发信号ts,则输入系统单元20的功能处理单元52(i)在触发信号ts的上升的定时接收中断信号。内部控制用处理器52b(i)在控制周期t1内对仪器2的检测结果实施功能处理,mpu 52a(i)将处理结果写入至共享存储器57(i)的处理结果存储区域57b(i)(步骤st1)。功能处理单元52(i)的mpu 52a(i)参照在共享存储器57(i)的触发控制次数存储区域57a(i)存储的触发控制次数n,对是否已结束了与触发控制次数n对应的量的功能处理进行判定(步骤st2)。

56.mpu 52a(i)如果判定为与触发控制次数n对应的量的功能处理尚未结束(步骤st2:no),则回到步骤st1。mpu 52a(i)如果判定为与触发控制次数n对应的量的功能处理已结束(步骤st2:yes),则结束一个同步周期t份的功能处理。功能处理单元52(i)如果判定为与触发控制次数n对应的量的功能处理尚未结束(步骤st2:no),则通过重复步骤st1,从而如图5所示,实施与触发控制次数n对应的量的功能处理,将与触发控制次数n对应的量的处理结果写入至共享存储器57(i)的处理结果存储区域57b(i)。

57.如果下一个触发信号ts输入至控制装置5,则如图5所示,cpu单元10取得在共享存储器57(i)的处理结果存储区域57b(i)存储的处理结果。在实施方式1中,cpu单元10将表示日期时间的信息与所取得的多个处理结果相关联而在计算机6的存储装置64进行累积,但由cpu单元10取得的处理结果的处理不限定于此。在实施方式1中,cpu单元10是对下述的多个处理结果进行处理的处理单元,该多个处理结果是通过由cpu单元10取得,从而由输入系统单元20的共享存储器57(i)汇总地输出的。另外,如果下一个触发信号ts输入至控制装置5,则如图5所示,输入系统单元20与输入了前次的触发信号ts时同样地,实施功能处理。

58.图7是表示实施方式1涉及的控制装置的输入系统单元的触发控制次数的设定画面的图。在对实施方式1涉及的控制装置5的输入系统单元20的触发控制次数进行设定时,用户操作计算机6的输入装置65,将图7所示的触发控制次数设定画面100显示于显示装置66。触发控制次数设定画面100如图7所示,至少具有:对象单元显示区域101,其示出对触发控制次数n进行设定的对象的单元名即“输入系统单元”;以及触发控制次数设定区域102,其对“触发控制次数”进行设定。用户操作输入装置65,进行向触发控制次数设定区域102输入触发控制次数n的输入动作,如果进行将已输入的触发控制次数n确定下来的确定动作,则将确定下来的触发控制次数n通过计算机6的通信接口67发送至cpu单元10,依次发送至cpu单元10的通信用处理器51、总线通信线l1、背板40的通信中继控制部42b、总线通信线l2、输入系统单元20的通信用处理器51(i),写入至输入系统单元20的共享存储器57(i)的触发控制次数存储区域57a(i)。

59.根据实施方式1涉及的输入系统单元20及控制装置5,基于触发信号ts,功能处理单元52(i)以比触发信号ts的同步周期t短的控制周期t1实施功能处理。另外,根据输入系统单元20及控制装置5,设为将功能处理单元52(i)的处理结果写入至共享存储器57(i),能够将处理结果汇总地输出的状态。因此,对于输入系统单元20及控制装置5而言,由于在一个同步周期t内功能处理单元52(i)能够实施多次功能处理,并且将处理结果写入至共享存储器57(i),因此能够设为可在外部利用在一个同步周期t内生成的处理结果的状态。其结果,输入系统单元20及控制装置5能够有效利用输入系统单元20所具有的高速功能处理性能。另外,根据实施方式1涉及的输入系统单元20及控制装置5,能够以比同步周期t短的周期取得作为传感器的仪器2的检测结果。

60.另外,根据实施方式1涉及的输入系统单元20及控制装置5,功能处理单元52(i)将触发信号ts作为起点而反复实施功能处理,因此在一个同步周期t内能够实施尽量多的功能处理。并且,根据实施方式1涉及的输入系统单元20及控制装置5,功能处理单元52(i)将触发信号ts作为起点而反复实施功能处理,因此在系统内配置有多个输入系统单元20的情况下,还能够抑制由内部控制用处理器52b(i)产生的控制周期t1的波动。因此,在系统内配置有多个输入系统单元20的情况下,输入系统单元20能够以将由plc系统决定的同步周期t

进一步最小化而得到的周期进行同步,永久地进行控制。

61.另外,根据实施方式1涉及的输入系统单元20及控制装置5,能够在共享存储器57(i)的触发控制次数存储区域57a(i)对触发控制次数n进行设定,因此能够对同步周期t内的实施功能处理的次数进行变更。对于实施方式1涉及的输入系统单元20及控制装置5而言,触发控制次数n是从在mpu 52a(i)内存储的计算机程序写入的。因此,对于实施方式1涉及的输入系统单元20及控制装置5,即使将来同步周期t缩短,也能够灵活地进行应对而无需改变内部控制用处理器52b(i)。另外,对于输入系统单元20及控制装置5,在触发控制次数n是经由cpu单元10从计算机6写入的情况下,用户能够自由地设定与同步周期t相比进一步最小化而得到的功能处理的控制周期。其中,功能处理的控制周期的最短周期是控制周期t1。

62.根据实施方式1涉及的输入系统单元20及控制装置5,由于满足式1,因此能够抑制横跨多个同步周期t而实施由功能处理单元52(i)实施的功能处理的情况。

63.实施方式2.

64.接下来,基于附图对本发明的实施方式2涉及的控制装置5进行说明。图8是表示实施方式2涉及的控制装置的输出系统单元的硬件结构的图。图9是表示实施方式2涉及的控制装置的输出系统单元的共享存储器的存储区域的图。在图8及图9中,对与实施方式1相同的部分标注相同的标号而省略说明。

65.在实施方式2涉及的控制装置5中,输出系统单元30是功能单元,输入系统单元20是其他单元。在输出系统单元30中,取代实施方式1的输入系统单元20的输入电路部55(i)而具有输出电路部55

‑

2(o),外部输入输出接口56(o)与仪器3连接。输出电路部55

‑

2(o)由d/a转换器或数字i/o构成。

66.输出系统单元30的共享存储器57(o)如图9所示,具有:触发控制次数存储区域57a(o),其是对触发控制次数n进行存储的设定功能部;以及处理对象存储区域57c(o),其存储功能处理单元52(o)的内部控制用处理器52b(o)的功能处理的处理对象。触发控制次数存储区域57a(o)呈与实施方式1涉及的输入系统单元20的共享存储器57(i)的触发控制次数存储区域57a(i)相同的结构。

67.经由cpu单元10通过计算机6将通过功能处理单元52(o)的功能处理进行加工的处理对象写入至处理对象存储区域57c(o)。处理对象是按照进行功能处理的顺序而写入至处理对象存储区域57c(o)的。在处理对象存储区域57c(o),按照内部控制用处理器52b(o)的处理顺序写入与触发控制次数n对应的量的处理对象。由功能处理单元52(o)的mpu 52a(o)从处理对象存储区域57c(o)取得所存储的与触发控制次数n对应的量的处理对象。此外,处理对象存储区域57c(o)的地址预先设定于cpu单元10内。cpu单元10通过在预先设定的地址区域写入值而写入与触发控制次数n对应的量的处理对象。对于共享存储器57(o)而言,通过经由cpu单元10从计算机6将与触发控制次数n对应的量的处理对象写入至共享存储器57(o),从而共享存储器57(o)作为基于触发信号ts从输出系统单元30的外部汇总地输入功能处理单元52(o)的多个处理对象的输入控制部起作用。因此,在实施方式2中,cpu单元10是基于触发信号ts,将处理对象汇总地输入至共享存储器57的处理单元。此外,在实施方式2中,将多个处理对象汇总地输入是指,在触发信号ts输入后直至下一个触发信号ts输入为止的同步周期t内,由作为外部的cpu单元10将多个处理对象汇总地写入。

68.输出系统单元30的功能处理单元52(o)的内部控制用处理器52b(o)实施对在共享存储器57(o)的处理对象存储区域57c(o)存储的处理对象进行加工的功能处理。输出系统单元30的功能处理单元52(o)在由输出电路部55

‑

2(o)接收到通过功能处理生成的处理结果后,经过外部输入输出接口56(o)而作为控制信号发送至仪器3。

69.功能处理单元52(o)由于具有存储计算机程序的mpu 52a(o)和实施硬件处理的内部控制用处理器52b(o),因此能够以比触发信号ts的同步周期t短的控制周期t1实施处理对象的功能处理,生成仪器3的控制信号。对于功能处理单元52(o)而言,在触发信号ts的一个同步周期t的期间,内部控制用处理器52b(o)反复实施多次处理对象的功能处理,生成多次控制信号,发送至仪器3。

70.接下来,基于附图对实施方式2涉及的输出系统单元30及控制装置5的动作的一个例子进行说明。图10是表示实施方式2涉及的控制装置的动作的一个例子的时序图。图11是表示实施方式2涉及的控制装置的输出系统单元的功能处理单元的处理的一个例子的流程图。

71.如图10所示,向实施方式2涉及的控制装置5,以恒定的同步周期t从背板40的同步时钟生成部42a输入触发信号ts。如果输入了触发信号ts,则cpu单元10将从计算机6输入的处理对象写入至输出系统单元30的共享存储器57(o)的处理对象存储区域57c(o)。

72.如果下一个触发信号ts输入至控制装置5,则输出系统单元30的功能处理单元52(o)在触发信号ts的上升的定时从通信用处理器51(o)接收中断信号。功能处理单元52(o)的mpu 52a(o)从共享存储器57(o)的处理对象存储区域57c(o)取得多个处理对象(步骤st1

‑

2)。在实施方式2中,对于共享存储器57(o)的处理对象存储区域57c(o)而言,如果通过功能处理单元52(o)的mpu 52a(o)从处理对象存储区域57c(o)取得了所存储的处理对象,则处理对象存储区域57c(o)被功能处理单元52(o)的mpu 52a(o)清空,成为未存储信息的空的状态。

73.输出系统单元30的功能处理单元52(o)的内部控制用处理器52b(o)实施处理对象的功能处理,如图10所示,将控制信号输出至仪器3(步骤st2

‑

2)。功能处理单元52(o)的mpu 52a(o)参照在共享存储器57(o)的触发控制次数存储区域57a(o)存储的触发控制次数n,对是否已结束了与触发控制次数n对应的量的功能处理进行判定(步骤st3

‑

2)。

74.mpu 52a(o)如果判定为与触发控制次数n对应的量的功能处理尚未结束(步骤st3

‑

2:no),则回到步骤st2

‑

2。mpu 52a(o)如果判定为与触发控制次数n对应的量的功能处理已结束(步骤st3

‑

2:yes),则结束一个同步周期t份的功能处理。功能处理单元52(o)如果判定为与触发控制次数n对应的量的功能处理尚未结束(步骤st3

‑

2:no),则通过重复步骤st2

‑

2,从而如图10所示,实施与触发控制次数n对应的量的功能处理,将控制信号输出至仪器3。

75.另外,在输出系统单元30的功能处理单元52(o)的mpu 52a(o)通过步骤st1

‑

2从共享存储器57(o)的处理对象存储区域57c(o)取得多个处理对象后,cpu单元10将从计算机6输入的处理对象写入至输出系统单元30的共享存储器57(o)的被功能处理单元52(o)的mpu 52a(o)清空而成为未存储信息的空的状态的处理对象存储区域57c(o)。

76.另外,与实施方式1同样地设定实施方式2涉及的控制装置5的输出系统单元30的触发控制次数n。

77.根据实施方式2涉及的输出系统单元30及控制装置5,基于触发信号ts,功能处理单元52(o)以比触发信号ts的同步周期t短的控制周期t1实施功能处理。另外,根据输出系统单元30及控制装置5,将功能处理单元52(o)的处理对象从外部写入至共享存储器57(o),从而汇总地将处理对象输入。因此,对于输出系统单元30及控制装置5而言,在一个同步周期t内功能处理单元52(o)能够实施多次功能处理。其结果,输出系统单元30及控制装置5能够有效利用输出系统单元30所具有的高速功能处理性能。另外,根据实施方式2涉及的输出系统单元30及控制装置5,能够以比同步周期t短的周期将控制信号发送至作为驱动仪器的仪器3。

78.另外,根据实施方式2涉及的输出系统单元30及控制装置5,功能处理单元52(o)将触发信号ts作为起点而反复实施功能处理,因此在系统内配置有多个输出系统单元30的情况下,还能够抑制由内部控制用处理器52b(o)产生的控制周期t1的波动。因此,在系统内配置有多个输出系统单元30的情况下,输出系统单元30能够以将由plc系统决定的同步周期t进一步最小化而得到的周期进行同步,永久地进行控制。

79.对于实施方式2涉及的输出系统单元30及控制装置5而言,触发控制次数n是从在mpu 52a(o)内存储的计算机程序写入的,因此与实施方式1同样地,即使将来同步周期t缩短,也能够灵活地进行应对而无需改变内部控制用处理器52b(o)。另外,对于输出系统单元30及控制装置5而言,在触发控制次数n是经由cpu单元10从计算机6写入的情况下,用户能够自由地设定与同步周期t相比进一步最小化而得到的功能处理的控制周期。其中,功能处理的控制周期的最短周期是控制周期t1。

80.实施方式3.

81.接下来,基于附图对本发明的实施方式3涉及的功能单元70进行说明。图12是表示实施方式3涉及的功能单元的硬件结构的图。图13是表示实施方式3涉及的功能单元的动作的一个例子的时序图。在图12及图13中,对与实施方式1及实施方式2相同的部分标注相同的标号而省略说明。

82.在实施方式3中,功能单元70是在实施方式1及实施方式2中记载的输入系统单元20或输出系统单元30。功能单元70如图12所示,具有作为功能处理部的功能处理单元52,该功能处理单元52如果接收到触发信号ts,则在触发信号ts的上升的定时实施与输入系统单元20或输出系统单元30相同的功能处理。功能单元70具备与输入系统单元20或输出系统单元30相同的具有触发控制次数存储区域57a的共享存储器57。功能单元70的通信用处理器51与计算机6连接。

83.在实施方式3中,功能单元70如果接收到通过用户操作计算机6而输入的触发信号ts,则如图13所示,以与写入至触发控制次数存储区域57a的触发控制次数n对应的量实施功能处理。即,功能单元70的功能处理单元52将触发信号ts作为起点,以与触发控制次数n对应的量反复实施功能处理。在实施方式3中,从计算机6将触发信号ts输入至功能单元70,但不限定于此,只要将触发信号ts从功能单元70的外部在任意的定时输入,即,将触发信号ts非周期地输入即可。另外,在实施方式3中,功能单元70在触发信号ts的上升的定时以与触发控制次数n对应的量反复实施功能处理,之后,实施任意的处理,但也可以不实施任意的处理。

84.根据实施方式3涉及的功能单元70,与实施方式1及实施方式2同样地,将触发信号

ts作为起点,功能处理单元52反复实施功能处理,因此能够有效利用功能单元70所具有的高速功能处理性能。

85.以上的实施方式示出的结构表示的是本发明的内容的一个例子,既能够与其他公知的技术进行组合,也能够在不脱离本发明的主旨的范围内对结构的一部分进行省略、变更。

86.标号的说明

87.5控制装置,10 cpu单元(处理单元),20输入系统单元,30输出系统单元,52功能处理单元(功能处理部),57共享存储器,57a触发控制次数存储区域(设定功能部),70功能单元,t同步周期,t1控制周期,ts触发信号。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1