一种基于火电厂嵌入式智能控制的装置及方法与流程

1.本发明属于火电厂dcs嵌入式智能控制技术领域,具体涉及一种基于火电厂嵌入式智能控制的装置及方法。

背景技术:

2.目前,国内大多数火电厂采用的dcs控制系统是由控制功能分散的多个控制单元组组成,为了满足稳定性的要求,每个控制单元组又是由一对冗余的控制器构成,而每个控制器中只有一个嵌入式处理器。此嵌入式处理器大都采用amd、intel的x86架构,少部分采用powerpc、arm、mips、ultrasparc、alpha等处理器架构,单个控制器的全部计算都依赖采用复杂指令集的嵌入式处理器处理。现有智能算法计算的特点是单次计算方式简单但整体计算量非常庞大且耗时,而火电厂控制领域对实时性有比较高的要求,故常规情况下智能算法都是在上位机的处理器中进行智能算法计算的。因为上位机的处理器拥有更高的主频和更大的带宽,并且上位机的机体空间没大小限制,这样可以选择采用具有更多核心的处理器,还可以在高功耗的情况下采用更多更有效的散热方式以满足处理器稳定运行,然而上述各种嵌入式处理器的主频和功耗都无法和上位机处理器相比,要使普通dcs控制器运行智能算法,需要在传统的嵌入式硬件平台上解决如下几方面问题:1)对于通用架构的嵌入式处理器来说,提高这种处理器计算能力的两种简单的方式,一是提高主频,二是增加内核数量。然而现阶段成熟dcs控制系统中受到各种条件的限制,控制器的嵌入式处理器硬件大都采用单核嵌入式处理器,主频也只有区区几百mhz、内存只有几百mb,因此嵌入式控制器硬件级别很难满足嵌入式控制器的智能算法的计算要求。

3.2)现有控制器中嵌入式处理器大都采用复杂指令集的通用处理器架构,这种复杂指令集的通用处理器的计算方式都是先从内存中提取一小部分数据,放在寄存器或者缓存中,然后使用一系列指令对这些数据进行操作,操作完毕后将数据写回缓存,再由缓存写回内存,下一步提取另一小部分数据,再用一系列指令进行处理,以此循环往复。然而针对单次计算方式简单但整体计算量又非常大的智能算法来说,哪怕执行一条很简单的加减计算,对复杂指令集的通用处理器来说,也是执行了多条的指令序列,这种复杂指令集的通用嵌入式处理器架构大大增加了计算的复杂程度,执行效率十分低下,无法满足嵌入式控制器的智能算法计算的要求。

4.3)现阶段智能控制算法处于初期的探索阶段,各家的实现方式也不尽相同,当然也无法分析并总结出其中通用的规律。故此dcs厂家也不能为了提高效率,为所有智能算法定制特定的处理芯片,这样成本太高。传统嵌入式控制器采用的通用嵌入式处理器,从架构上决定了无法满足各种智能控制算法修改灵活、运行高效和低成本的要求。

技术实现要素:

5.为了解决在嵌入式智能控制器中运行智能控制算法的需求,本发明的目的是提出

一种基于火电厂嵌入式智能控制装置及方法。

6.为了实现上述目的,本发明采用以下技术方案:一种基于火电厂嵌入式智能控制的装置,包括嵌入式逻辑处理器、主存储器、第一协处理器以及第二协处理器;主存储器、第一协处理器以及第二协处理器均与嵌入式逻辑处理器相连。

7.进一步的,嵌入式逻辑处理器包括内存管理单元、第一pci

‑

e控制器、第二pci

‑

e控制器、第一直接存储器访问模块及第二直接存储器访问模块;第一直接存储器访问模块及第二直接存储器访问模块均与内存管理单元相连,内存管理单元、第一直接存储器访问模块及第二直接存储器访问模块均与主存储器相连;第一协处理器通过第一pci

‑

e控制器与第一直接存储器访问模块相连,第二协处理器通过第二pci

‑

e控制器与第二直接存储器访问模块相连。

8.进一步的,第一协处理器用于扩展网口和串口,其中,网口用于接收上位机dcs操作指令,并将上位机dcs操作指令通过第一pci

‑

e控制器与第一直接存储器访问模块存储到主存储器的共享内存;串口用于接收io卡件采集的数据,并将io卡件采集的数据通过第一pci

‑

e控制器与第一直接存储器访问模块存储到主存储器的共享内存。

9.进一步的,第一pci

‑

e控制器通过第一pci

‑

e总线与第一协处理器连接。

10.进一步的,第二pci

‑

e控制器通过第二pci

‑

e总线与第二协处理器连接。

11.进一步的,第一协处理器和第二协处理器均为国产fpga芯片。

12.进一步的,嵌入式逻辑处理器、第一协处理器与第二协处理器设置在带有散热孔的壳体内。

13.进一步的,壳体侧面设置有散热鳍。

14.进一步的,壳体材质为航空铝材。

15.一种基于火电厂嵌入式智能控制的方法,采用如上所述的装置,该方法包括以下步骤:第一协处理器将接收到的io卡件采集的数据通过第一pci

‑

e控制器与第一直接存储器访问模块存储到主存储器的共享内存中;第二协处理器通过第二pci

‑

e控制器与第二直接存储器访问模块从主存储器的共享内存获取数据,进行计算后,将计算结果通过第二pci

‑

e控制器与第二直接存储器访问模块存储到主存储器的共享内存中。

16.和现有技术相比较,本发明具备如下有益效果:本发明提出基于嵌入式逻辑处理器和第二协处理器并行分布式计算架构,充分利用第二协处理器运算速度的优势和电路配置灵活的特点,将大量简单的运算从嵌入式逻辑处理器分离出来,提高了运算效率,将控制器整体功耗控制在一个较低的水平,实现了在普通的嵌入式火电dcs控制器内运行复杂智能算法的可能。为了满足智能控制算法的实时计算和版本频繁迭代升级的要求,本发明通过灵活配置第二协处理器,能够将大量智能算法中简单但比较耗时的计算从传统的嵌入式逻辑控制器中分离出来,并将这部分数据交由第二协处理器进行处理,极大的提高了单位时间内的计算性能,同时降低了嵌入式逻辑处理器的负荷,在满足嵌入式智能控制功能要求的条件下,降低产品功耗,提高了单位时间内的处理能力,解决了普通嵌入式控制器在采用传统嵌入式处理器架构下,无法满足智能算法

计算量大的问题。本发明采用模块化设计架构,便于第一协处理器和第二协处理器的升级和扩展。

附图说明

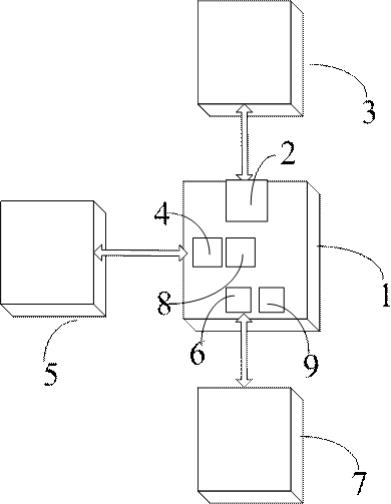

17.图1为本发明的基于火电厂嵌入式智能控制的装置框图。

18.图中,1为嵌入式逻辑处理器,2为内存管理单元,3为主存储器,4为第一pci

‑

e控制器,5为第一协处理器,6为第二pci

‑

e控制器,7为第二协处理器,8为第一直接存储器访问模块,9为第二直接存储器访问模块。

具体实施方式

19.下面结合附图对本发明进行详细说明。

20.参见图1,一种基于火电厂嵌入式智能控制的装置,包括嵌入式逻辑处理器1、主存储器3、第一协处理器5以及第二协处理器7,主存储器3、第一协处理器5以及第二协处理器7均与嵌入式逻辑处理器1相连。

21.具体的,嵌入式逻辑处理器1包括内存管理单元2、第一pci

‑

e控制器4、第二pci

‑

e控制器6、第一直接存储器访问模块8及第二直接存储器访问模块9;第一直接存储器访问模块8及第二直接存储器访问模块9均与内存管理单元2相连,内存管理单元2、第一直接存储器访问模块8及第二直接存储器访问模块9均与主存储器3相连;第一协处理器5通过第一pci

‑

e控制器4与第一直接存储器访问模块8相连,第二协处理器7通过第二pci

‑

e控制器6与第二直接存储器访问模块9相连。

22.第二协处理器7中配置了多种不同的硬件电路,这些硬件电路用于解决智能算法中类似矩阵计算等耗时的数学运算,从而使普通嵌入式控制器中能够运算预测控制算法、模糊控制预测控制、状态观测器预测控制算法、补偿控制预测控制算法和阀门自适应校正预测控制算法等原来只能在上位机中才能运行的智能控制算法。

23.嵌入式逻辑处理器1用于处理逻辑计算。逻辑计算的具体过程为:将数据采集器采集到的数据,通过io卡件传输给第一协处理器5,第一协处理器5将接收到的io卡件采集的数据通过第一pci

‑

e控制器4与第一直接存储器访问模块8存储到主存储器3的共享内存中。嵌入式逻辑处理器1根据不同的智能算法类型调用第二协处理器7中相应的硬件电路运算,将主存储器3的共享内存中第二协处理器7计算需要的数据通过内存管理单元2传输给嵌入式逻辑处理器1,第二协处理器7中用到的计算数据通过第二pci

‑

e控制器6与第二直接存储器访问模块9从主存储器3的共享内存获取,当第二协处理器7计算完毕后,将计算结果通过第二pci

‑

e控制器6与第二直接存储器访问模块9再回传给主存储器3的共享内存中。本发明将大量简单的数学运算从嵌入式逻辑处理器1解放出来,通过第二协处理器7中硬件电路进行计算,降低了嵌入式逻辑处理器1的负荷,提高了大量简单的数学运算的运算效率。

24.主存储器3用于存储数据,数据包括嵌入式逻辑处理器1的逻辑计算的计算结果,第一协处理器5及第二协处理器7的计算结果。

25.第一协处理器5用于扩展网口和串口,其中,网口用于接收上位机dcs操作指令,并将上位机dcs操作指令通过第一pci

‑

e控制器4与第一直接存储器访问模块8存储到主存储器3的共享内存。串口用于接收io卡件采集的数据,并将io卡件采集的数据通过第一pci

‑

e

控制器4与第一直接存储器访问模块8存储到主存储器3的共享内存。其中,io卡件采集的数据为火电厂现场设备采集的数据。

26.第一直接存储器访问模块8用于嵌入式逻辑处理器1和第一协处理器5之间的数据通信或数据交互。

27.第二直接存储器访问模块9用于嵌入式逻辑处理器1和第二协处理器7之间的数据通信或数据交互。

28.本发明的基于火电厂嵌入式智能控制的装置提供两个100管脚的cpci连接器,用于接插底座和用于冗余连接。

29.本发明通过第一协处理器5扩展四个千兆网口,通过上述cpci连接器的管脚对外相连,其中两个千兆网口用于两个冗余控制单元之间同步通讯,另外两个千兆网口用于每个控制单元对上位机的通讯。

30.本发明的基于火电厂嵌入式智能控制的装置集成一组指示灯,该指示灯与嵌入式逻辑处理器1连接,分别用于显示电源状态、同步状态、网络状态以及协处理器工作状态等信号。

31.嵌入式逻辑处理器1支持两个原生的千兆网卡,千兆网卡直接集成在嵌入式逻辑处理器1的主板上,千兆网卡对外提供一个用于连接调试装置的调试网口。

32.为了解决嵌入式逻辑处理器1、第一协处理器5以及第二协处理器7的散热问题,将嵌入式逻辑处理器1、第一协处理器5以及第二协处理器7设置在壳体内,壳体底部开设有散热孔,侧面设置有散热鳍,采用航空铝材作为壳体材料,通过壳体材料、散热孔和散热鳍的设置,提高了散热效率,从而保证稳定运行。

33.第一协处理器5和第二协处理器7均为国产fpga芯片。

34.为满足智能计算需要,给主存储器3配备4gb的ecc板载工业级内存芯片,满足了嵌入式智能控制器的功能需求,同时提高运行的稳定性和可靠性。

35.本发明的工作原理如下:基于火电厂嵌入式智能控制的装置加电后,嵌入式逻辑处理器1开始从nandflash上加入bootloader程序,此bootloader程序加载过程为:第一步,关闭嵌入式逻辑处理器1的内部指令、数据、中断以及看门狗等资源,接着开始配置pll以及主存储器3等;第二步,从nandflash上载入第一协处理器5的rbf文件,通过此文件加载网络协议站,激活phy芯片和mac芯片,利用gmii和lpc实现网络数据收发功能;第三步,开始从nandflash上载入第二协处理器7的rbf文件,通过此文件加载多个预置的硬件电路,例如多种矩阵计算电路与多种排序计算电路等,并初始化这些智能硬件电路和硬件电路中的寄存器,并将这些智能硬件电路的状态设置为空闲。

36.传统处理器架构下,通过机器指令码的形式处理计算和数据存取等操作,这些需要处理的计算和数据存取操作,首先逐条的被翻译成处理器能识别的机器指令码,由于传统处理器采用的是复杂指令集,一条计算将会被翻译成多条处理器指令码,然而智能算法本身又用到大量的数据计算,如果全部交由传统架构的嵌入式逻辑处理器处理的话,复杂度较高。在现有执行智能算法的上位机中,处理器基本上都是采用比嵌入式处理器更高的处理频率,或者采用比嵌入式处理器更多核心的处理器,提高主频和增加更多核心,意味着

计算能力的提高,但这样会造成处理器面积和功耗的不断增大,面积和速度是两个矛盾的组成部分,首先,面积不可能无限的增大,其次,面积增大的同时加剧了功耗的上涨,而功耗的增加会导致暗硅效应的产生,当然这些不利因素不满足火电dcs控制器使用场景的要求。为了解决这个问题,必须要采用一种芯片,此芯片能满足大量并行计算的要求,并且芯片的面积和功耗还不能太大。经过对多种处理架构算力、功耗、安全性、可持续发展等角度的总和评估后,第二协处理器7最终选择一款国产fpga芯片。首先,国产fpga芯片可将指令锁定在硬件架构上,采用硬件电路的方式实现,然后以持续处理数据流的方式完成计算,因为国产fpga芯片本身具有高速处理大并发数据流的能力;其次,国产fpga芯片自身也在不断发展,计算能力不断增强,功耗不断降低,为在智能控制器中实现更复杂的智能算法奠定了基础;现有智能算法处于初期设计阶段,设计思路和实现方式各异,会导致智能算法的修改比较频繁,国产fpga芯片具有的灵活性的特点,满足多变的智能算法的设计要求。

37.本发明一种基于火电厂嵌入式智能控制的装置的运行方法为:基于火电厂嵌入式智能控制的装置加电后,首先,由嵌入式逻辑处理器1从板载nand flash中加载uboot程序,uboot程序开始处理看门狗、关中断、设置时钟频率、关mmu初始化各个bank以及硬件 ecc 检测等工作,正常加载嵌入式逻辑处理器1、内存管理单元2以及主存储器3后,判断这三个设备配置状态是否正常,如果正常,点亮电源指示灯。

38.电源指示灯点亮后,uboot程序加载第一pci

‑

e控制器4、第一协处理器5以及第一直接存储器访问模块8。第一协处理器5加载过程中通过gmii和lpc初始化多个mac芯片与phy芯片的配置,并根据配置文件配置四个网口的默认ip,第一协处理器5加载好后配置第一pci

‑

e控制器4和第一直接存储器访问模块8。

39.然后加载第二pci

‑

e控制器6、第二协处理器7以及第二直接存储器访问模块9,第二协处理器7主要用于提供智能计算的硬件支持,第二协处理器7通过第二pci

‑

e控制器6(即ci

‑

express lanes控制器)总线与嵌入式逻辑处理器1相连,再初始化第二直接存储器访问模块9。

40.最后加载上层应用软件部分,上层应用软件部分包括组态、同步以及对时等基础dcs系统功能,点亮运行灯、同步灯以及对时灯等。上位机通过工程师站拖拽的方式,将图形化的智能算法块拖到程序组织单元pou中,当程序组织单元pou中的智能算法块起效后,判断此智能算法块是否需要第二协处理器7的加速,如果执行到需要加速的智能算法块后,嵌入式逻辑处理器1将智能计算数据(智能计算数据为水或者煤的采集量,或者是某一时刻的煤的采集量,或者是某一时刻的引风机的数量)通过主存储器3传输到第二直接存储器访问模块9,再由第二直接存储器访问模块9通过第二pci

‑

e控制器6传输给第二协处理器7,第二协处理器7计算后经反向存储到主存储器3中,嵌入式逻辑处理器1从主存储器3的共享内存中取得计算后的结果。

41.当程序组织单元pou执行完毕后,将程序组织单元pou中必要的中间计算结果,通过第一协处理器5扩展的网口,实时传输给备用智能控制器,从而为升级为主备冗余嵌入式智能控制器奠定基础。通过第二协处理器7配合嵌入式逻辑处理器1的方式,解决了传统嵌入式控制器中无法执行复杂智能算法的问题。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1