可编程逻辑器件的透传结构及可编程逻辑器件的制作方法

1.本发明属于电子电路技术领域,特别是涉及可编程逻辑器件技术领域。

背景技术:

2.可编程逻辑器件(programmable logic device,pld)具有低成本、集成度高以及方便工作扩展的优势,pld已成为越来越多复杂系统的首选解决方案。

3.一般情况下,可编程逻辑器件的链路架构都是通过一定的通道选择扩展器件(例如pca95系列的通道选择扩展器)去实现,但是由于可编程逻辑器件的电路板面积有限,布局紧张,在无法布设通道选择扩展器件时,难以实现可编程逻辑器件的通道的有效扩展。

技术实现要素:

4.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种可编程逻辑器件的透传结构及可编程逻辑器件,用于解决现有技术中可编程逻辑器件引进不足,输出通道难以扩展的技术问题。

5.为实现上述目的及其他相关目的,本发明的实施例提供一种可编程逻辑器件的透传结构,包括:上游三态门电路模块,下游三态门电路模块,总线方向解析模块以及多路输入的逻辑与操作模块;所述总线方向解析模块与上游信号总线、所述上游三态门电路模块相连,并通过反相器连接到所述下游三态门电路模块的使能控制端口,所述总线方向解析模块用于解析所述上游信号总线上总线信号的传输方向,并基于所述总线信号的传输方向生成三态门方向切换逻辑信号,以进行所述上游三态门电路模块和下游三态门电路模块的使能控制,实现上下游三态门信号传输方向的切换;所述多路输入的逻辑与操作模块分别与所述上游三态门电路模块和所述下游三态门电路模块相连,将所述下游三态门电路模块的下游输入信号进行逻辑与操作后,输入到所述上游三态门电路模块;所述上游三态门电路模块与所述上游信号总线、所述总线方向解析模块以及所述多路输入的逻辑与操作模块相连,根据所述三态门方向切换逻辑信号控制使能控制位,以实现上游信号总线的信号输入和所述多路输入的逻辑与操作模块的信号输出;所述下游三态门电路模块与下游从设备相连,根据所述下游三态门方向切换逻辑信号控制使能控制位,以实现上游信号总线的输入信号到所述下游从设备的传输,所述下游输入信号到所述多路输入的逻辑与操作模块的传输。

6.于本技术的一实施例中,所述信号总线包括上游时钟信号总线和上游数据信号总线。

7.于本技术的一实施例中,所述上游三态门电路模块包括:第一上游三态门电路,与所述上游时钟信号总线相连;第二上游三态门电路,与所述上游数据信号总线相连;所述下游三态门电路模块包括:第一下游三态门电路,包含多个三态门,与多个下游从设备相连,通过各所述三态门分别控制向对应的所述下游从设备传输时钟信号;第二下游三态门电路,包含多个三态门,与多个所述下游从设备相连,通过各所述三态门分别控制向对应的所

述下游从设备传输数据信号。

8.于本技术的一实施例中,所述总线方向解析模块包括:上游时钟信号总线方向解析模块,分别与所述上游时钟信号总线、所述上游数据信号总线以及所述第一下游三态门电路相连,用于解析所述上游时钟信号总线上信号的传输方向,并基于所述上游时钟信号总线上信号的传输方向生成控制所述第一上游三态门电路的使能控制位的第一上游三态门方向切换逻辑信号、控制所述第一下游三态门电路的使能控制位的第一下游三态门方向切换逻辑信号;上游数据信号总线方向解析模块,分别与所述上游时钟信号总线、所述上游数据信号总线以及所述第二下游三态门电路相连,用于解析所述上游数据信号总线上信号的传输方向,并基于所述上游数据信号总线上信号的传输方向生成控制所述第二上游三态门电路的使能控制位的第二上游三态门方向切换逻辑信号、控制所述第二下游三态门电路的使能控制位的第二下游三态门方向切换逻辑信号。

9.于本技术的一实施例中,所述多路输入的逻辑与操作模块包括:第一多路输入的逻辑与操作模块,分别与所述第一上游三态门电路和所述第一下游三态门电路相连,将所述第一下游三态门电路的第一下游输入信号进行逻辑与操作后,输出到所述第一上游三态门电路;第二多路输入的逻辑与操作模块,分别与所述第二上游三态门电路和所述第二下游三态门电路相连,将所述第二下游三态门电路的第二下游输入信号进行逻辑与操作后,输出到所述第二上游三态门电路。

10.于本技术的一实施例中,所述第一上游三态门电路根据所述第一上游三态门方向切换逻辑信号控制使能控制位,以实现上游时钟信号总线的信号输入和所述第一多路输入的逻辑与操作模块的信号输出;所述第二上游三态门电路根据所述第二上游三态门方向切换逻辑信号控制使能控制位,以实现上游数据信号总线的信号输入和所述第二多路输入的逻辑与操作模块的信号输出。

11.于本技术的一实施例中,所述第一下游三态门电路根据所述第一下游三态门方向切换逻辑信号控制使能控制位,以实现上游时钟信号总线的输入信号到所述第一下游从设备的传输,所述第一下游输入信号到所述第一多路输入的逻辑与操作模块的传输;所述第二下游三态门电路根据所述第二下游三态门方向切换逻辑信号控制使能控制位,以实现上游数据信号总线的输入信号到所述第二下游从设备的传输,所述第二下游输入信号到所述第二多路输入的逻辑与操作模块的传输。

12.于本技术的一实施例中,还包括:第一反相器,连接于所述第一下游三态门电路和所述上游时钟信号总线方向解析模块之间,所述第一上游三态门电路和所述第一下游三态门电路的时钟信号的传输方向互为逻辑反。

13.于本技术的一实施例中,第二反相器,连接于所述第二下游三态门电路和所述上游数据信号总线方向解析模块之间,所述第二上游三态门电路和所述第二下游三态门电路的时钟信号的传输方向互为逻辑反。

14.本发明的实施例还提供一种可编程逻辑器件,包括上所述的可编程逻辑器件的透传结构。

15.如上所述,本发明的可编程逻辑器件的透传结构及可编程逻辑器件,具有以下有益效果:

16.本发明中的透传结构可以实现对可编程逻辑器件的通信通道扩展的目的,本发明

不仅还可以提高可编程逻辑器件的资源利用率,根据外挂下游设备的数量来进行针对性扩展透传结构,可以节约产品的成本,节省电路板的布局空间。

附图说明

17.图1显示为本发明的可编程逻辑器件的透传结构的整体原理结构示意图。

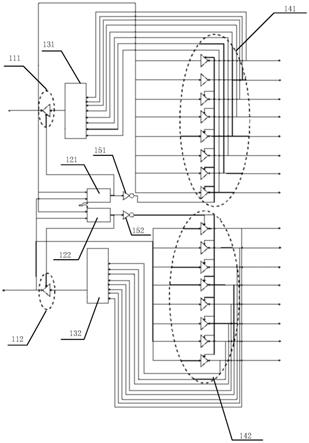

18.图2显示为本发明的可编程逻辑器件的透传结构的具体结构示意图。

19.元件标号说明

20.100

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

可编程逻辑器件的透传结构

21.110

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

上游三态门电路模块

22.111

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一上游三态门电路

23.112

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二上游三态门电路

24.120

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

总线方向解析模块

25.121

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

上游时钟信号总线方向解析模块

26.122

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

上游数据信号总线方向解析模块

27.130

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

多路输入的逻辑与操作模块

28.131

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一多路输入的逻辑与操作模块

29.132

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二多路输入的逻辑与操作模块

30.140

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

下游三态门电路模块

31.141

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一下游三态门电路

32.142

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二下游三态门电路

33.151

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一反相器

34.152

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二反相器

具体实施方式

35.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。

36.本实施例的目的在于提供一种可编程逻辑器件的透传结构100及可编程逻辑器件,用于解决现有技术中控制节点在控制机柜中出现混插时无法正常工作的技术问题。

37.以下将详细阐述本实施例的可编程逻辑器件的透传结构100及可编程逻辑器件的原理及实施方式,使本领域技术人员不需要创造性劳动即可理解本发明的可编程逻辑器件的透传结构100及可编程逻辑器件。

38.如图1所示,本实施例提供一种可编程逻辑器件的透传结构100,所述可编程逻辑器件的透传结构100包括:上游三态门电路模块110,下游三态门电路模块140,总线方向解析模块120以及多路输入的逻辑与操作模块130。

39.本实施例中的所述可编程逻辑器件的透传结构100将上游的信号总线主直接透给下游的多路信号总线,下游的多路信号总线分别与多路下游从设备,从而达到对可编程逻

辑器件的通信通道扩展的目的,达到通过上游的信号总线控制多路下游从设备的目的,实现透传。

40.如图2所示,于本实施例中,所述上游三态门电路模块110包括:第一上游三态门电路111和第二上游三态门电路112。

41.其中,具体地,于本实施例中,信号总线包括上游时钟信号总线和上游数据信号总线,所述第一上游三态门电路111与所述上游时钟信号总线相连,所述第二上游三态门电路112与所述上游数据信号总线相连。

42.于本实施例中,所述下游三态门电路模块140包括:第一下游三态门电路141,包含多个三态门(例如图2中所示的8个三态门),与多个下游从设备相连,通过各所述三态门分别控制向对应的所述下游从设备传输时钟信号;第二下游三态门电路142,包含多个三态门(例如图2中所示的8个三态门),与多个所述下游从设备相连,通过各所述三态门分别控制向对应的所述下游从设备传输数据信号。

43.于本实施例中,所述总线方向解析模块120解析的原理是根据上游时钟信号和上游数据信号,依据总线协议格式解析出上游时钟信号总和上游数据信号的传输的方向,解析出来的数据传输方向控制信号作为数据端口三态门的使能控制位。

44.具体地,于本实施例中,所述总线方向解析模块120与上游信号总线、所述上游三态门电路模块110相连,并通过反相器连接到所述下游三态门电路模块140的使能控制端口,所述总线方向解析模块120用于解析所述上游信号总线上总线信号的传输方向,并基于所述总线信号的传输方向生成三态门方向切换逻辑信号,以进行所述上游三态门电路模块110和下游三态门电路模块140的使能控制,实现上下游三态门信号传输方向的切换。

45.其中,所述反相器包括第一反相器151和第二反相器152。

46.所述第一反相器151连接于所述第一下游三态门电路141和所述上游时钟信号总线方向解析模块121之间,所述第一上游三态门电路111和所述第一下游三态门电路141的时钟信号的传输方向互为逻辑反;所述第二反相器152连接于所述第二下游三态门电路142和所述上游数据信号总线方向解析模块122之间,所述第二上游三态门电路112和所述第二下游三态门电路142的时钟信号的传输方向互为逻辑反。

47.具体地,于本实施例中,所述总线方向解析模块120包括:上游时钟信号总线方向解析模块121和上游数据信号总线方向解析模块122。

48.其中,所述上游时钟信号总线方向解析模块121分别与所述上游时钟信号总线、所述上游数据信号总线以及所述第一下游三态门电路141相连,用于解析所述上游时钟信号总线上信号的传输方向,并基于所述上游时钟信号总线上信号的传输方向生成控制所述第一上游三态门电路111的使能控制位的第一上游三态门方向切换逻辑信号、控制所述第一下游三态门电路141的使能控制位的第一下游三态门方向切换逻辑信号。

49.其中,所述上游数据信号总线方向解析模块122分别与所述上游时钟信号总线、所述上游数据信号总线以及所述第二下游三态门电路142相连,用于解析所述上游数据信号总线上信号的传输方向,并基于所述上游数据信号总线上信号的传输方向生成控制所述第二上游三态门电路112的使能控制位的第二上游三态门方向切换逻辑信号、控制所述第二下游三态门电路142的使能控制位的第二下游三态门方向切换逻辑信号。

50.于本实施例中,所述多路输入的逻辑与操作模块130分别与所述上游三态门电路

模块110和所述下游三态门电路模块140相连,将所述下游三态门电路模块140的下游输入信号进行逻辑与操作后,输入到所述上游三态门电路模块110;所述上游三态门电路模块110与所述上游信号总线、所述总线方向解析模块120以及所述多路输入的逻辑与操作模块130相连,根据所述三态门方向切换逻辑信号控制使能控制位,以实现上游信号总线的信号输入和所述多路输入的逻辑与操作模块130的信号输出;所述下游三态门电路模块140与下游从设备相连,根据所述下游三态门方向切换逻辑信号控制使能控制位,以实现上游信号总线的输入信号到所述下游从设备的传输,所述下游输入信号到所述多路输入的逻辑与操作模块130的传输。

51.具体地,于本实施例中,所述多路输入的逻辑与操作模块130包括:第一多路输入的逻辑与操作模块131和第二多路输入的逻辑与操作模块132。

52.其中,所述第一多路输入的逻辑与操作模块131分别与所述第一上游三态门电路111和所述第一下游三态门电路141相连,将所述第一下游三态门电路141的第一下游输入信号进行逻辑与操作后,输出到所述第一上游三态门电路111;第二多路输入的逻辑与操作模块132,分别与所述第二上游三态门电路112和所述第二下游三态门电路142相连,将所述第二下游三态门电路142的第二下游输入信号进行逻辑与操作后,输出到所述第二上游三态门电路112。

53.本实施例的可编程逻辑器件的透传结构100的工作原理如下:

54.1)所述第一上游三态门电路111根据所述第一上游三态门方向切换逻辑信号控制使能控制位,以实现上游时钟信号总线的信号输入和所述第一多路输入的逻辑与操作模块131的信号输出;所述第二上游三态门电路112根据所述第二上游三态门方向切换逻辑信号控制使能控制位,以实现上游数据信号总线的信号输入和所述第二多路输入的逻辑与操作模块132的信号输出。

55.2)所述第一下游三态门电路141根据所述第一下游三态门方向切换逻辑信号控制使能控制位,以实现上游时钟信号总线的输入信号到所述第一下游从设备的传输,所述第一下游输入信号到所述第一多路输入的逻辑与操作模块131的传输;所述第二下游三态门电路142根据所述第二下游三态门方向切换逻辑信号控制使能控制位,以实现上游数据信号总线的输入信号到所述第二下游从设备的传输,所述第二下游输入信号到所述第二多路输入的逻辑与操作模块132的传输。

56.此外,本发明的实施例还提供一种可编程逻辑器件,包括上所述的可编程逻辑器件的透传结构100。上述已经对可编程逻辑器件的透传结构100进行了详细说明,在此不再赘述。

57.综上所述,本发明中的透传结构可以实现对可编程逻辑器件的通信通道扩展的目的,本发明不仅还可以提高可编程逻辑器件的资源利用率,根据外挂下游设备的数量来进行针对性扩展透传结构,可以节约产品的成本,节省电路板的布局空间。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

58.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1