一种高电源纹波抑制比超低温度依赖带隙基准电路的制作方法

1.本发明涉及集成电子电路领域中的带隙基准电路,特别涉及高精度带隙基准电路。

背景技术:

2.带隙基准电路(bandgap reference,bgr)为片上系统soc(system on a chip)提供不随温度、供电压和工艺波动的稳定基准电压,为保证后续片上电路的精确工作,需满足一定精度设计:对温度波动不敏感、对供电压的波动敏感度低。

3.对于集成电路来说,其供电电源本身并不是理想的直流电压,会包含一定的交流噪声分量,而整个片上系统的其他电路,比如数字电路、数模混合电路等在工作时也会产生较大的噪声。这些噪声共同组成了电源噪声,对于模拟电路来说,电源噪声对其性能的影响是巨大的。psrr越高,代表电路对电源纹波的抵抗能力越好,从而高psrr的性能成为一个重要的诉求。在电路中使用共源共栅结构来提高psrr是很常用的方法。2014年,dongjunwang等人[dongjun wang,ping luo and pengfei liao,"high psrr low noise cmos bandgapvoltage reference,"[c].2014 ieee international conference on electron devices and solid-statecircuits,chengdu,2014,pp.1-2,doi:10.1109/edssc.2014.7061176.]在pmos的输入对管上使用共源共栅电流镜的结构,以及在输出端使用多个mos管来把它们当作电阻和电容使用,也大大提高了psrr。在低频时,其psrr高达-128db,并且在之后频率提升的过程中,其psrr最小也有-68.6db,可以看到效果很明显。温度范围在-40到125℃时,温度系数为 13.3ppm/℃。但是最小供电压被提高到了1.61v。除了在基准电路内部进行改进之外,在电源输入端减小电源噪声也成为了一个重要的研究热点。同样在2014年,yuanming zhu等人 [y.zhu,f.liu,y.yang,g.huang,t.yin and h.yang,"a-115db psrr cmos bandgapreference with a novel voltage self-regulating technique,"[c].proceedings of the ieee 2014custom integrated circuits conference,san jose,ca,2014,pp.1-4.]在不使用运算放大器或任何滤波电容的情况下,提出了一种新的电压自调节技术来提高带隙基准的psrr。实现该电路的技术简单,且电路总体功耗也很低。基准电压在直流电压时的psrr达到-115db,在交流电压频率为10mhz时也高达-90db。在-40℃到125℃范围内,得到了11.68ppm/℃的温漂系数,所提出的电压自调节电路消耗的电流为42μb,这个功耗较大,是这个设计的一个缺点。由此可知,引入了这种自我调节的电路,虽然大大提升了psrr,但它却要单独消耗更大的功率,且按照理论分析,其最低供电电压也被抬高了。为了解决这个问题,2017年, myungjun kim等人[m.kim and s.cho,"a 0.8v,37nw,42ppm/℃ sub-bandgap voltagereference with psrr of-81db and line sensitivity of 51ppm/v in 0.18um cmos,"[c].2017symposium on vlsi circuits,kyoto,2017,pp.c144-c145.]提出了一种内部反馈的ctat电路和一种双管ptat电路。为了提高温度曲线的线性灵敏度ls(line sensitivity,在本文的描述中称为line regulation)和psrr,采用了自供给调节反馈电路。这个设计相比于增加了反馈等环节,使用0.18μn的cmos工艺,使得

基准电压的平均温度系数达到42ppm/℃,在频率为50hz时psrr为-81db。线性灵敏度ls为51ppm/v,降低最小供电电压到 0.8v,在此时消耗的功率仅为37nw。

技术实现要素:

[0004]

本发明的目的在于克服现有技术的不足,实现了一种与电源电压、温度和工艺有最小相关度的高psrr带隙基准电路,在保证功耗、最低供电电压等性能在一定合理范围内的基础上,通过提高运算放大器的增益(增大运算放大器差分输入nmos对管的宽长比)、增大电流镜mos管的长度、以及加入mos低通滤波器等方法实现更高的psrr值和极低的温度依赖带隙输出,结构非常简单。

[0005]

本发明提供一种高psrr带隙基准电路,所述高psrr带隙基准电路至少包括:

[0006]

第一基准电路核心功能模块,其包括用于产生与绝对温度正比的第一bjt(双极性晶体管,q1)和第一电流的第一电阻,产生与绝对温度成反比的第二电流的第二bjt,以及用于与绝对温度无关的第三bjt和第三电流的第二电阻,其中第一bjt的发射结面积是第二bjt发射结面积的n倍,第一bjt的发射结面积是第三bjt发射结面积的n倍;其进一步包含运算放大器电路,第一电阻连接至运算放大器第一输入端,第二bjt的集电极连接至运算放大器第二输入端,第一mosfet和第零mosfet构成运放放大器的差分输入对管,第二mosfet 和第九mosfet构成所述第一电流镜,为运放提供偏置电流;第三mosfet和第四mosfet 构成所述第二电流镜,作为运放的负载,第三mosfet的漏极与栅极相连,第四mosfet 的漏极与第五mosfet和第六mosfet的栅极相连,第五mosfet和第六mosfet分别产出第一电流和第二电流,第八mosfet产生第三电流,第七mosfet与第六mosfet的栅极相连产生第四电流,为通过第九mosfet为第二mosfet提供偏置电流;

[0007]

第二启动功能模块,包括第一启动mosfet、第二启动mosfet和第三启动mosfet,其中第一启动mosfet和第二启动mosfet栅极相连接核心运放的第一输入端,它们的漏极连接第三启动mosfet的栅极,第三启动mosfet漏极连接基准核心功能模块的偏置管第五、六、七、八mosfet,产生第一、二、三、四电流。

[0008]

第三mos低通滤波模块,包括由第十mosfet和第十一mosfet形成的低通滤波器,其中第十mosfet栅极和源极相连,并连接第二电阻和第八mosfet的公共端;第十一 mosfet的栅极第十mosfet的漏极作为最终输出,其漏和源相接并连接到地。

[0009]

与已有技术相比,本发明有益效果体现在:

[0010]

本发明的一种高psrr基准带隙电路,通过提高运算放大器增益,增大电流镜的长度l 来提高psrr;适当减小了调零电阻的阻值,从而改变基准电压一阶补偿后温度曲线的曲率,降低温度系数;通过利用mos低通滤波器过滤高频噪声的特性改善基准电压高频时的psrr,这种mos低通滤波器的面积非常小,功耗极低。

附图说明

[0011]

图1是带隙基准电压实现零温度系数的结构。

[0012]

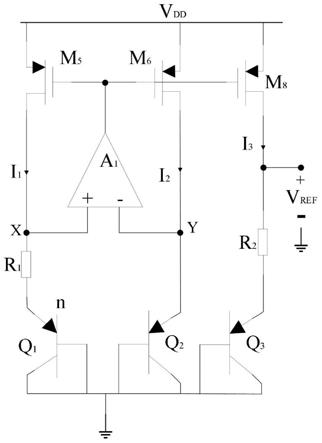

图2是本发明高psrr带隙基准原理图。

[0013]

图3是本发明的mos低通滤波器及其等效的rc滤波器

[0014]

图4是本发明高psrr带隙基准的启动过程仿真结果。

[0015]

图5是本发明的输出基准电压的温度特性仿真结果。

[0016]

图6是本发明的输出基准电压线性调整率仿真结果。

[0017]

图7是本发明高psrr带隙基准电压的psrr特性仿真图(接上mos低通滤波器之后的psrr仿真图)。

具体实施方式

[0018]

下列实施例是对本发明的进一步解释和补充,对本发明不构成任何限制。如附图2所示,高精度带隙基准电路包括第一核心基准电压产生模块、第二启动电路模块与第三mos低通滤波器模块。

[0019]

第一核心基准产生电路模块,利用产生ptat电流实现带隙基准结构。其包括用于产生与绝对温度正比的第一bjt(q1)和第一电流的第一电阻(r1),产生与绝对温度成反比的第二电流的第二bjt(q2),以及用于与绝对温度无关的第三bjt(q3)和第三电流的第二电阻(r2)。其中第一bjt的发射结面积是第二bjt发射结面积的7(m=7)倍,第一bjt的发射结面积是第三bjt发射结面积的7(m=7)倍;第五mofet(m5)、第六mofet(m6)和第八mofet(m8) 拥有相同的宽长比。第三电流i3流过电阻r2,产生ptat电压i3·

r2为正温度系数电压,将这个正温度系数电压,加到具有负温度系数的双极晶体管q3的基极-发射极电压v

be

上,就可获得一个零温度系数的基准电压:

[0020][0021]

当r1,r2,m和n满足关系:

[0022][0023]

则实现零温度依赖的基准电压。

[0024]

第一电阻r1和第二电阻r2需要满足下式:r2/r1≈17.2ln7=8.83。所以,r1=23k ω,则r2=203.09kω。

[0025]

核心基准产生电路模块进一步包含运算放大器电路,第一电阻连接至运算放大器第一输入端,第二bjt的集电极连接至运算放大器第二输入端,第一mosfet和第零mosfet构成运放放大器的差分输入对管,第二mosfet和第九mosfet构成所述第一电流镜,为运放提供偏置电流。通过进行电源波动分析,可以得出影响基准电压psrr的参数。根据图2 中电路的结构,定义运放第一输入端电压为vx,第二输入端电压为vy,可得到公式:

[0026]vg

=av(v

x-vy)+δv

dd

·add

ꢀꢀꢀꢀꢀꢀꢀꢀ

(3)

[0027]vref

=v

be,q3

+g

m8

·

(δv

dd-vg)

·

r2ꢀꢀꢀꢀꢀꢀ

(4)

[0028]

式中:δv

dd

——电源电压的交流电压,v;

[0029]av

——运算放大器的增益,db;

[0030]add

——运算放大器从电源电压到其输出端的增益,db;

[0031]vg

——运算放大器输出端的电压,v;

[0032]gm8

——m8的跨导,s(西门子)。

[0033]

可得:

[0034]vref

=v

be,q3

+g

m8

·

[δv

dd-av(v

x-vy)-δv

dd

·add

]

·

r2[0035]

=v

be,q3

+g

m8

·

[δv

dd

·

(1-a

dd

)-av(v

x-vy)]

·

r2ꢀꢀꢀꢀ

(5)

[0036]

x和y点的电位分别为:

[0037]vx

=g

m5

·

(δv

dd-vg)

·

(r

q1

+r1)

ꢀꢀꢀꢀꢀꢀ

(6)

[0038]vy

=g

m6

·

(δv

dd-vg)

·rq2

ꢀꢀꢀꢀꢀ

(7)

[0039]

式中,r

q1

——双极型晶体管q1的发射极对地的等效阻抗,ω;

[0040]rq2

——双极型晶体管q2的发射极对地的等效阻抗,ω。

[0041]

第五mosfet(m5)和第五mosfet(m6)具有相同的宽长比,所以g

m5

=g

m6

=gm,则运算放大器的差分输入电压(x和y点的电位差)为:

[0042]vx-vy=gm·

[δv

dd

·

(1-a

dd

)-av(v

x-vy)]

·

(r

q1

+r

1-r

q2

)

ꢀꢀꢀ

(8)

[0043]

令r0=r

q1

+r

1-r

q2

,则:

[0044]vx-vy=gm·

[δv

dd

·

(1-a

dd

)-av(v

x-vy)]

·

r0ꢀꢀꢀꢀꢀ

(9)

[0045]

进一步化简有:

[0046][0047]

将(10)代入(5)可得:

[0048][0049]

则基准电压和电源的交流电压比值为:

[0050][0051]

可以看出,需要增大运算放大器的增益来可以提高psrr。

[0052]

为了提高增益,需要增大第零mosfet(m0)和第一mosfet(m1)的跨导,对于偏置管第五mosfet(m5)和第五mosfet(m6),适当增大其长度l,也可以优化基准电压的 psrr。

[0053]

第二启动电路模块,当基准电路处于不理想的零电流状态时,第一mosfet(m0)不导通,所以它的栅源电压v

gs

小于阈值电压v

th

。因此,第二启动mofet(m

st2

)关闭,第一启动mofet (m

st1

)工作在线性区,则第三启动mofet(m

st3

)的栅源电压v

gs

被拉到电源v

dd

,则第三启动mofet(m

st3

)处于导通状态,并把第五mosfet(m5)、第六mosfet(m6)、第七 mosfet(m7)、第八mosfet(m8)的栅极电压拉低,从而将它们都导通。所以启动电路可以使得第五、六、七、八mosfet组成的偏置电路正常工作,从而避免了零电流状态。

[0054]

当基准电路稳定工作时,第二启动mofet(m

st2

)的栅源电压v

gs

处于一个较高的值,所以第二启动mofet(m

st2

)是导通状态,从而降低了第三启动mofet(m

st3

)的栅源电压。也就是说,第一启动mofet(m

st1

)和第二启动mofet(m

st2

)相当于一个cmos反相器,当基准电路正常工作时,反相器的输出会下降。又因为启动电路不能干扰到基准电路在稳定状态下的正

常运行,反相器的输出需要降到很低,从而使得第三启动mofet(m

st3

)在电路稳定工作的状态下关断。因此,当反相器输入从零上升到一个很高的电压值时,第三启动 mofet(m

st3

)的栅源电压必须低于阈值电压才能关断。所以在电路设计中,要求m

st2

的宽长比远大于m

st1

。

[0055]

第三mos低通滤波电路模块,针对电路的psrr在高频时下降得比较快,本发明尝试利用mos低通滤波器(mosfet low-pass-filter,mosfetlpf)来解决这个问题。在高频时, mos管的寄生电容对于psrr的提高有着重要的作用,且这种mosfetlpf的额外功耗非常小。由强反转的第十mosfet(mn1)和漏源连接的第十一mosfet(mp2)构成rc滤波器。图3为mos低通滤波器及其等效的rc滤波器,其传递函数为:

[0056][0057]

可以将其简化为:

[0058][0059]

其中r≈r

dsmp2

,c1=c

gdmp2

+c

bdmp2

,c2=c

gsmn1

+c

gdmn1

。

[0060]

本发明中设第十一mosfet(mp2)的宽长比为2μm/2μm,第十mosfet(mn1)的宽长比为2μm/4μm。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1