一种高适配性的多功能板控制系统的制作方法

1.本实用新型涉及多功能板技术领域,具体涉及一种高适配性的多功能板控制系统。

背景技术:

2.现在的电路板的应用领域越来越广,而多功能电路板是一种新型的电路板,由电路实验板和电路元件所组成。而现在的多功能电路板由信号处理控制单元输出pwm信号控制高速光耦的导通,并通过信号处理控制单元检测光耦是否导通;信号处理控制单元输出信号控制驱动板的风扇、蓄电器、接触器等驱动并检测风扇、蓄电器、接触器驱动等工作状态。

3.上述功能板的单元是由多个单元单独工作,且当数据传输较多时,容易造成系统崩溃。此外,这样的操作复杂,且只能针对某个系统,应用范围小,适配性不高。

技术实现要素:

4.针对现有技术存在的不足,本实用新型的目的在于提供一种高适配性的多功能板控制系统,该系统作为采集信号处理的中转站,能够适配多种系统,应用范围广泛。

5.为了实现上述目的,本实用新型提供如下技术方案:

6.一种高适配性的多功能板控制系统,包括

7.至少两组232通讯单元,所述232通讯单元用于接收外设的采集数据;

8.缓冲器单元,每两组232通讯单元与一组所述缓冲器单元连接,用于存放采集的数据;

9.cpu单元,所述cpu单元与所述缓冲器单元电连接,用于对提取并处理采集的数据。

10.在本实用新型中,进一步的,还包括驱动单元和继电器单元,所述cpu单元通过所述驱动单元与所述继电器单元电连接,所述cpu单元用于控制驱动单元驱动继电器单元动作以控制输出设备。

11.在本实用新型中,进一步的,还包括译码器单元以及电源单元,所述译码器单元、电源单元均与所述cpu单元电连接,所述译码器单元用于对cpu单元的输出数据进行转换并存储于所述缓冲器单元,所述电源单元与所述cpu单元电连接,所述电源单元用于为系统提供所需要的电源。

12.在本实用新型中,进一步的,所述232通讯单元设有六组,每组所述232通讯单元包括232通讯接口,六组所述232通讯接口分别用于接收下位数据、上传数据、上传显示器、传输拨码盘数据、连接指示灯以及获取sd数据,所述232通讯接口连接有通讯芯片,所述232通讯接口、通讯芯片均与所述缓冲器单元连接。

13.在本实用新型中,进一步的,所述缓冲器单元设有三组,每一组所述缓冲器单元与两组所述232通讯单元连接,每组所述缓冲器单元包括四个缓冲器,其中一组的四个缓冲器分别为缓冲器u2a、缓冲器u2b、缓冲器u2c、缓冲器u2d,所述缓冲器u2a的2脚、缓冲器u2d的

11脚连接一组所述232通讯单元,所述缓冲器u2b的5脚、缓冲器u2c的8脚连接另外一组所述232通讯单元。

14.在本实用新型中,进一步的,所述cpu单元包括主控芯片u1,所述主控芯片u1的p1.6、p1.7端口与所述缓冲器单元连接,用于实现主控芯片u1与缓冲单元的数据传输,所述主控芯片u1的p0.0至p0.7端口连接有时钟单元,所述时钟单元用于给主控芯片u1提供脉冲信号。

15.在本实用新型中,进一步的,所述驱动单元包括锁存器uio4以及驱动器uio2,所述锁存器uio4的输入端与所述主控芯片u1连接,用于对主控芯片u1传输的数据进行缓存,所述锁存器uio4的输出端与所述驱动器uio2的输入端连接,所述驱动器uio2输出端与所述继电器单元连接,所述驱动器uio2用于提取锁存器uio4中的数据并驱动继电器单元中的继电器工作。

16.在本实用新型中,进一步的,所述继电器单元包括继电器k1至继电器k4,所述继电器k1至继电器k4的输入端分别与所述驱动器uio2的out1至out4端口对应连接。

17.在本实用新型中,进一步的,所述译码器单元白包括译码器uio6,所述译码器uio6的a至c端口与所述主控芯片u1的p1.3至p1.5端口对应连接,所述译码器uio6的输出端与所述缓冲器单元连接。

18.在本实用新型中,进一步的,所述电源单元包括电源接口j3,所述电源接口j3连接有用于滤去信号干扰的滤波电路。

19.与现有技术相比,本实用新型的有益效果是:

20.本实用新型通过232通讯单元接收外设的采集数据,缓冲单元对数据进行存放,cpu单元提取缓冲单元的数据并处理后,控制驱动单元驱动继电器单元中的继电器动作。本系统作为采集信号处理的中转站,能够对多种采集到的信号进行缓存,以防止信号过多直接给cpu单元造成崩溃。本系统通过设置六组232通讯接口分别用于接收下位数据、上传数据、上传显示器、传输拨码盘数据、连接指示灯以及获取sd数据,能够连接多种设备获取不同设置的采集信号,能够适配多种系统,应用范围广泛。

附图说明

21.附图用来提供对本实用新型的进一步理解,并且构成说明书的一部分,与本实用新型的实施例一起用于解释本实用新型,并不构成对本实用新型的限制。在附图中:

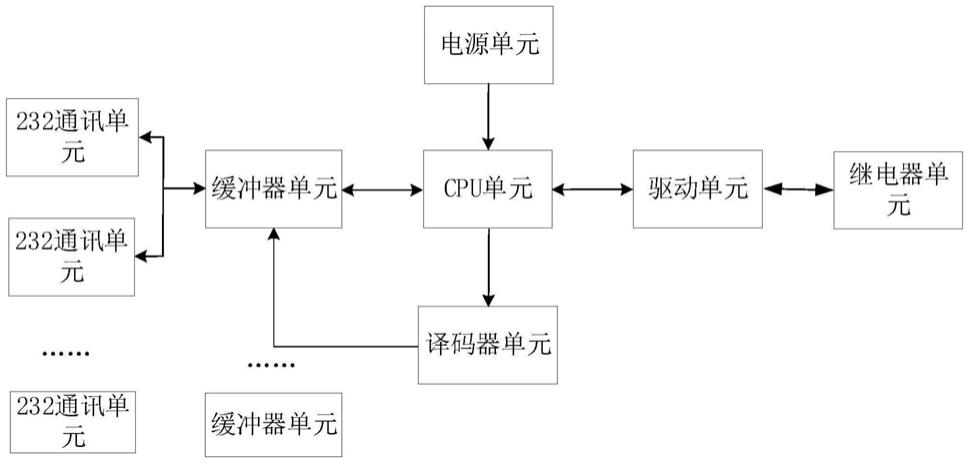

22.图1是本实用新型的的整体结构框图;

23.图2是本实用新型的cpu单元的电路图;

24.图3是本实用新型的232通讯接口的电路图;

25.图4是本实用新型的通讯芯片的电路图;

26.图5是本实用新型的缓冲器单元的电路图;

27.图6是本实用新型的继电器单元的电路图;

28.图7是本实用新型的驱动单元的电路图;

29.图8是本实用新型的译码器单元的电路图;

30.图9是本实用新型的电源单元的电路图。

具体实施方式

31.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

32.需要说明的是,当组件被称为“固定于”另一个组件,它可以直接在另一个组件上或者也可以存在居中的组件。当一个组件被认为是“连接”另一个组件,它可以是直接连接到另一个组件或者可能同时存在居中组件。当一个组件被认为是“设置于”另一个组件,它可以是直接设置在另一个组件上或者可能同时存在居中组件。本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。

33.除非另有定义,本文所使用的所有的技术和科学术语与属于本实用新型的技术领域的技术人员通常理解的含义相同。本文中在本实用新型的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本实用新型。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

34.请参见图1,本实用新型一较佳实施方式提供一种高适配性的多功能板控制系统,包括一种高适配性的多功能板控制系统,包括

35.至少两组232通讯单元,所述232通讯单元用于接收外设的采集数据;

36.缓冲器单元,每两组232通讯单元与一组所述缓冲器单元连接,用于存放采集的数据;

37.cpu单元,所述cpu单元与所述缓冲器单元电连接,用于对提取并处理采集的数据。

38.具体的,在本实施例中,通过232通讯单元接收外设的采集数据,缓冲单元对数据进行存放,cpu单元提取缓冲单元的数据并处理,cpu单元作为本系统的核心,用于控制整个数据传输以及指令的流程。本系统作为采集信号处理的中转站,缓冲器单元能够对多种采集到的信号进行缓存,以防止信号过多直接给cpu单元造成系统崩溃。

39.在本实用新型中,进一步的,还包括驱动单元和继电器单元,所述cpu单元通过所述驱动单元与所述继电器单元电连接,所述cpu单元用于控制驱动单元驱动继电器单元动作以控制输出设备。继电器单元用于控制继电器等设备动作,以控制设备得失电。

40.在本实用新型中,进一步的,还包括译码器单元以及电源单元,所述译码器单元、电源单元均与所述cpu单元电连接,所述译码器单元用于对cpu单元的输出数据进行转换并存储于所述缓冲器单元,所述电源单元与所述cpu单元电连接,所述电源单元用于为系统提供所需要的电源。

41.在本实用新型中,请参见图2,具体的,所述cpu单元包括主控芯片u1,主控芯片u1的型号为stc11f48,所述主控芯片u1的p1.6、p1.7端口与所述缓冲器单元连接,用于实现主控芯片u1与缓冲单元的数据传输,主控芯片u1的p0.0至p0.7端口连接有时钟单元,时钟单元用于给主控芯片u1提供脉冲信号,具体的时钟单元包括时钟芯片u6,时钟芯片u6的型号为ds12887,时钟芯片u6的13、14、15引脚分别与主控芯片u1的26、27、12引脚对应连接,用于给主控芯片u1提供准确的时钟信号,以保证主控芯片u1内部程序的准确运行。

42.在本实用新型中,进一步的,请参见图3、4,所述232通讯单元设有六组,每组所述232通讯单元包括232通讯接口,六组所述232通讯接口分别为,接口j1、接口j2、接口jio2、

接口j5、接口jio3、接口j6,分别用于接收下位数据、上传数据、上传显示器、传输拨码盘数据、连接指示灯以及获取sd数据,232通讯接口连接有通讯芯片,通讯芯片包括芯片u4、芯片u5以及芯片uio3,三个通讯芯片的型号均max232,每个通讯芯片分别与上述两个通讯接口连接,用于对通讯接口获取的数据进行转换,以芯片u4为例,芯片u4的13、14引脚与接口j1连接,芯片u4的9、10引脚与主控芯片u1的5、7引脚对应连接,用于实现主控芯片u1与通讯芯片u4之间信号的传输。

43.本系统通过设置六组232通讯接口分别用于接收下位数据、上传数据、上传显示器、传输拨码盘数据、连接指示灯以及获取sd数据,能够连接多种设备获取不同设置的采集信号,能够适配多种系统,应用范围广泛。

44.在本实用新型中,进一步的,请参见图5,所述缓冲器单元设有结构相同的三组,每一组所述缓冲器单元与两组所述232通讯单元连接,每组所述缓冲器单元包括四个缓冲器,以其中一组为例,其中一组四个缓冲器分别为缓冲器u2a、缓冲器u2b、缓冲器u2c、缓冲器u2d,所述缓冲器u2a的2脚、缓冲器u2d的11脚分别连接通讯芯片u4的12脚、11脚,所述缓冲器u2b的5脚、缓冲器u2c的8脚连接通讯芯片u45的12、11脚,缓冲器u2a的3脚、缓冲器u2b的6脚连接后与主控芯片u1的p1.6端口连接,主控芯片u1用于控制缓冲器信号的接收,缓冲器u2c的12脚、缓冲器u2d的9脚连接后与与主控芯片u1的p1.7端口连接,主控芯片u1用于控制缓冲器信号的提取。

45.在本实用新型中,进一步的,请参见图7,所述驱动单元包括锁存器uio4以及驱动器uio2,锁存器uio4的型号为74hc573,所述锁存器uio4的输入端与所述主控芯片u1连接,用于对主控芯片u1传输的数据进行缓存,所述锁存器uio4的输出端与所述驱动器uio2的输入端连接,所述驱动器uio2输出端与所述继电器单元连接,驱动器uio2的型号为uln2803a,所述驱动器uio2用于提取锁存器uio4中的数据并驱动继电器单元中的继电器工作。具体的,主控芯片u1的数据先经过锁存器uio4进行缓冲,驱动器uio2通过对锁存器uio4中的数据进行提取,以控制继电器单元完成相对应的操作指令。

46.在本实用新型中,进一步的,请参见图6,所述继电器单元包括继电器k1至继电器k4,所述继电器k1至继电器k4的输入端分别与所述驱动器uio2的out1至out4端口对应连接,驱动器uio2按照指令输出信号控制相对应的继电器吸合或断开,以控制设备通断电。

47.在本实用新型中,进一步的,请参见图8,所述译码器单元白包括译码器uio6,译码器uio6的型号为74hc138,所述译码器uio6的a至c端口与所述主控芯片u1的p1.3至p1.5端口对应连接,所述译码器uio6的输出端与所述缓冲器单元连接。具体的,译码器uio6的15引脚连接至缓冲器u2a的1脚与缓冲器u2d的13脚的连接线上,译码器uio6的14引脚缓冲器u2b的4脚与缓冲器u2c的10脚的连接线上,y2至y7端口的连接方式相似,如此,cpu单元通过译码器uio6对指令进行转换以单独控制每个缓冲单元的状态。

48.在本实用新型中,进一步的,请参见图9,所述电源单元包括电源接口j3,所述电源接口j3连接有用于滤去信号干扰的滤波电路。具体的,滤波电路由电容cio3、电容cio4、电容c1、电容c2、电容c3、电容cio5、电容cio6以及电容e1依次并联组成,通过滤波电路滤去信号干扰以得到vcc电源来给各个芯片供电。

49.在本实施方式中,

50.工作原理:通过232通讯单元接收外设的采集数据,具体通过六组所述232通讯接

口分别用于接收下位数据、上传数据、上传显示器、传输拨码盘数据、连接指示灯以及获取sd数据,以使系统能够连接多种设备获取不同设置的采集信号,应用范围广泛,232通讯单元将接受到数据经过缓冲单元进行存放,cpu单元通过译码器单元进行信号转换,控制每一组缓冲单元的数据状态,cpu单元提取所需要的缓冲单元的数据并处理后,将指令送到驱动单元,数据先经过锁存器uio4缓冲,在经过驱动器uio2控制继电器单元中的继电器动作。

51.上述说明是针对本实用新型较佳可行实施例的详细说明,但实施例并非用以限定本实用新型的专利申请范围,凡本实用新型所提示的技术精神下所完成的同等变化或修饰变更,均应属于本实用新型所涵盖专利范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1