具有宽调节电压范围的混合电压调节器的制作方法

具有宽调节电压范围的混合电压调节器

1.相关申请的交叉引用

2.本技术要求于2020年7月28日在美国专利和商标局提交的非临时申请序列号16/941,230和于2020年7月28日在美国专利和商标局提交的非临时申请序列号16/941,261的优先权和权益,其内容被并入本文,如同在下面充分地全部陈述的并且用于所有适用目的。

技术领域

3.本公开的各个方面大体上涉及电压调节器,更具体地涉及具有宽调节电压范围的混合电压调节器。

背景技术:

4.电压调节器被用于各种系统中,以为系统中的电源电路提供调节电压。常用的电压调节器是低压差(ldo)调节器。ldo调节器可以被用于提供干净的调节电压以向电路(例如驱动器)供电。ldo调节器通常包括传输晶体管和误差放大器,其中误差放大器的输出基于参考电压和调节电压的反馈来驱动传输晶体管的栅极。

技术实现要素:

5.以下提出了一个或多个实施方式的简化发明内容,以提供对这种实施方式的基础理解。该发明内容不是所有设想实施方式的广泛概述,并且既不旨在标识所有实施方式的关键或重要元件,也不旨在描写任何或所有实施方式的范围。其唯一目的是以简化的形式提出一个或多个实施方式的一些概念,作为稍后呈现的更详细描述的序言。

6.第一方面涉及一种包括电压调节器的芯片。电压调节器包括被耦合在第一电压轨与第二电压轨之间的传输n型场效应晶体管(nfet)和被耦合在第一电压轨与第二电压轨之间的传输p型场效应晶体管(pfet)。电压调节器还包括具有输出的第一放大器、被耦合在第一放大器的输出与传输nfet的栅极之间的第一开关、具有输出的第二放大器以及被耦合在第二放大器的输出与传输pfet的栅极之间的第二开关、被耦合在传输nfet的栅极与接地之间的第三开关以及被耦合在传输pfet的栅极与第二电压轨之间的第四开关。

7.第二方面涉及一种操作混合电压调节器的方法。电压调节器包括传输n型场效应晶体管(nfet)和传输p型场效应晶体管(pfet),传输nfet被耦合在第一电压轨与第二电压轨之间,传输pfet被耦合在第一电压轨与第二电压轨之间。该方法包括:在第一调节模式下,关断传输pfet,并且基于参考电压和反馈电压来驱动传输nfet的栅极,其中反馈电压提供第一电压轨上的电压的反馈。该方法还包括:在第二调节模式下,关断传输nfet,并且基于参考电压和反馈电压来驱动传输pfet的栅极。

附图说明

8.图1示出了根据本公开的某些方面的包括第一芯片、第二芯片和用于芯片到芯片通信的驱动器的系统的示例。

9.图2示出了根据本公开的某些方面的串行器/解串行器(serdes)被用于芯片到芯片通信的系统的示例。

10.图3示出了根据本公开的某些方面的差分链路被用于芯片到芯片通信的系统的示例。

11.图4示出了根据本公开的某些方面的具有nfet上nfet架构的驱动器的示例。

12.图5示出了根据本公开的某些方面的具有pfet上nfet架构的驱动器的示例。

13.图6示出了根据本公开的某些方面的混合驱动器的示例。

14.图7示出了根据本公开的某些方面的开关控制电路的示例性实施方式。

15.图8示出了根据本公开的某些方面的包括多个切片的混合驱动器的示例。

16.图9示出了根据本公开的某些方面的差分混合驱动器的示例。

17.图10示出了根据本公开的某些方面的包括多个切片的差分混合驱动器的示例。

18.图11示出了根据本公开的某些方面的包括传输nfet的低压差(ldo)调节器。

19.图12示出了根据本公开的某些方面的包括传输pfet的ldo调节器。

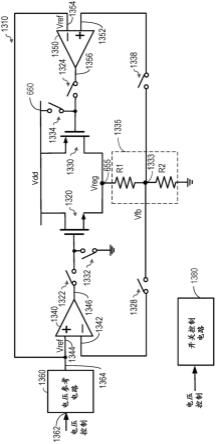

20.图13示出了根据本公开的某些方面的包括传输nfet和传输pfet的混合ldo调节器的示例。

21.图14示出了根据本公开的某些方面的包括补偿电路的混合ldo调节器的示例。

22.图15示出了根据本公开的某些方面的电压参考电路的示例性实施方式。

23.图16示出了根据本公开的某些方面的电压参考电路的另一示例性实施方式。

24.图17示出了根据本公开的某些方面的电压参考电路的再一示例性实施方式。

25.图18示出了根据本公开的某些方面的通过混合驱动器和混合ldo调节器的静电放电路径的示例。

26.图19a示出了根据本公开的某些方面的混合驱动器的示例性实施方式。

27.图19b示出了根据本公开的某些方面的由与图19a中的混合驱动器相同的控制信号集合控制的混合ldo调节器的示例性实施方式。

28.图20是图示了根据本公开的某些方面的用于操作混合电压调节器的方法的流程图。

具体实施方式

29.下面结合所附附图陈述的详细描述旨在作为各种配置的描述,并且不旨在表示本文描述的概念可以被实践的唯一配置。详细描述包括具体细节,以便提供对各种概念的透彻理解。然而,对于本领域技术人员来说显而易见的是,这些概念可以在没有这些具体细节的情况下实践。在一些实例中,众所周知的结构和组件以框图形式示出,以避免混淆这种概念。

30.图1示出了包括第一芯片110、第二芯片120、第一链路122和第二链路124的系统100的示例。链路122和124中的每个链路可以包括衬底126(例如印刷电路板)、电缆等上的一个或多个金属迹线。第一芯片110和第二芯片120可以被安装在衬底126上,其示例在图1中示出。然而,要了解的是,情况并非如此。

31.在该示例中,第一芯片110包括第一驱动器130和被耦合至第一驱动器130的输出的第一输出引脚135。第二芯片120包括第一接收器140和被耦合至第一接收器140的输入的

第一输入引脚145。第一链路122被耦合在第一芯片110上的第一输出引脚135与第二芯片120上的第一输入引脚145之间。

32.在操作中,第一驱动器130从第一芯片110上的第一电路170接收信号。第一电路170可以包括处理器、收发器、调制解调器或另一类型的电路。第一驱动器130用信号驱动第一链路122,以将信号从第一芯片110传输到第二芯片120。第二芯片120上的第一接收器140经由第一链路122接收信号,并且将接收到的信号输出到第二芯片120上的第二电路175以供进一步处理。第二电路175可以包括处理器、收发器、调制解调器或另一类型的电路。第一接收器140可以放大接收信号和/或对接收信号执行均衡,以校正由第一链路122中的频率相关衰减引起的接收信号中的失真。在该示例中,第一驱动器130、第一链路122和第一接收器140支持从第一芯片110到第二芯片120的通信。

33.在该示例中,第二芯片120还包括第二驱动器150和被耦合至第二驱动器150的输出的第二输出引脚155。第一芯片110包括第二接收器160和被耦合至第二接收器160的输入的第二输入引脚165。第二链路124被耦合在第二芯片120上的第二输出引脚155与第一芯片110上的第二输入引脚165之间。

34.在操作中,第二驱动器150从第二芯片120上的第二电路175接收信号。第二驱动器150用信号驱动第二链路124,以将信号从第二芯片120传输到第一芯片110。第一芯片110上的第二接收器160经由第二链路124接收信号,并且将接收到的信号输出到第一芯片110上的第一电路170以供进一步处理。第二接收器160可以放大接收信号和/或对接收信号执行均衡,以校正由第二链路124中的频率相关衰减引起的接收信号中的失真。在该示例中,第二驱动器150、第二链路124和第二接收器160支持从第二芯片120到第一芯片110的通信。

35.因此,在该示例中,驱动器130和150、链路122和124以及接收器140和160促进了第一芯片110与第二芯片120之间的双向通信。然而,要了解的是,在其他实施方式中,通信可以仅在一个方向上被支持。例如,针对仅从第一芯片110到第二芯片120的通信被支持的实施方式,第二驱动器150、第二链路124和第二接收器160可以被省略。还要了解的是,两个方向上的通信可以在共享链路上被执行,而不是在两个单独的链路上被执行(例如使用时分复用,其中信号一次在一个方向上跨共享链路传输)。还要了解的是,第一芯片110和第二芯片120可以包括图1中未示出的附加组件。例如,第一芯片110可以在第一电路170与第一驱动器130的输入之间包括第一预驱动器电路,以预驱动第一驱动器130,并且第二芯片120可以在第二电路175与第二驱动器150的输入之间包括第二预驱动器电路以预驱动第二驱动器150。

36.在某些方面中,串行器/解串行器(serdes)可以被用于在第一芯片110与第二芯片120之间发送高速串行信号。serdes的优点在于serdes减少了第一芯片110和第二芯片120的引脚计数。第一芯片110与第二芯片120之间的serdes通信的示例在图2中示出。

37.在该示例中,第一芯片110包括在第一电路170与第一驱动器130的输入之间的第一串行器210,并且第二芯片120包括在第一接收器140的输出与第二电路175之间的第一解串行器220。在操作中,第一串行器210从第一电路170接收并行信号,并且将接收到的并行信号转换为串行信号。第一驱动器130接收串行信号,并且用串行信号驱动第一链路122。第二芯片120上的第一接收器140经由第一链路122接收串行信号,并且将接收到的串行信号输出到第一解串行器220。第一解串行器220将接收到的串行信号转换回并行信号,并且将

并行信号输出到第二电路175用于进一步处理。

38.在该示例中,第二芯片120包括在第二电路175与第二驱动器150的输入之间的第二串行器230,并且第二芯片110包括在第二接收器160的输出与第一电路170之间的第二解串行器240。在操作中,第二串行器230从第二电路175接收并行信号,并且将接收到的并行信号转换为串行信号。第二驱动器150接收串行信号,并且用串行信号驱动第二链路124。第一芯片110上的第二接收器160经由第二链路124接收串行信号,并且将接收到的串行信号输出到第二解串行器240。第二解串行器240将接收到的串行信号转换回并行信号,并且将并行信号输出到第一电路170用于进一步处理。

39.在某些方面中,第一链路122和第二链路124中的每个链路都可以是差分链路。在这方面,图3示出了一个示例,其中第一链路122是包括第一对传输线312a和312b的差分链路,并且第二链路124是包括第二对传输线314a和314b的差分链路。每个传输线312a、312b、314a和314b可以包括衬底126(例如印刷电路板)上的金属线。

40.在该示例中,第一驱动器130具有包括一对输出330a和330b的差分输出,并且第一接收器140具有包括一对输入340a和340b的差分输入。第一驱动器130的输出330a经由输出引脚335a被耦合至传输线312a,并且第一驱动器130的输出330b经由输出引脚335b被耦合到传输线312b。第一驱动器130被配置为用差分信号驱动传输线312a和312b。第一接收器140的输入340a经由输入引脚345a被耦合至传输线312a,并且第一接收器140的输入340b经由输入引脚345b被耦合到传输线312b。第一接收器140被配置为在输入340a和340b处接收差分信号。

41.在该示例中,第二驱动器150具有包括一对输出350a和350b的差分输出,并且第二接收器160具有包括一对输入360a和360b的差分输入。第二驱动器150的输出350a经由输出引脚355a被耦合至传输线314a,并且第二驱动器150的输出350b经由输出引脚355b被耦合到传输线314b。第二驱动器150被配置为用差分信号驱动传输线314a和314b。第二接收器160的输入360a经由输入引脚365a被耦合至传输线314a,并且第二接收器160的输入360b经由输入引脚365b被耦合到传输线314b。第二接收器160被配置为在输入360a和360b处接收差分信号。

42.在某些方面中,驱动器130和150可能需要支持第一芯片110与第二芯片120之间的各种距离。例如,第一芯片110与第二芯片120之间的距离可以跨不同系统变化(例如一英寸到六英寸以上)。针对较短的距离,跨链路122和124的衰减较小,从而允许驱动器130和150的输出信号电平(即,幅度)较低以节省功率。针对较长的距离,跨链路122和124的衰减较高,这可能要求驱动器130和150的输出信号电平(即,幅度)较高,以确保足够的信号电平到达接收器140和160。因此,可能期望驱动器130和150具有宽的输出信号电平(即,幅度)范围,以支持在第一芯片110与第二芯片120之间的各种距离上的信号传输。

43.在一些应用中,第一芯片110可以是射频集成电路(rfic)芯片,并且第二芯片120可以是调制解调器芯片。在这些应用中,第一电路170可以包括收发器,并且第二电路175可以包括调制解调器,其中驱动器130和150在收发器与调制解调器之间提供芯片到芯片的通信(即,接口)。收发器与调制解调器之间的数据速率可以在宽范围内变化(例如在1.5gbps到18gbps之间)。例如,收发器和调制解调器可以支持具有宽数据速率范围的无线通信技术。而且,收发器和调制解调器可以支持具有不同数据速率的多种无线通信技术(例如第五

代(5g)、第四代(4g)、第三代(3g)等)。针对较低的数据速率,驱动器130和150的输出信号电平(即,幅度)可以较低以节省功率。针对较高的数据速率,驱动器130和150的输出信号电平(即,幅度)可能需要较高,以确保在接收器140和160处有足够的数据眼。

44.因此,期望具有宽输出信号电平(即,幅度)范围的驱动器来支持第一芯片110与第二芯片120之间的各种距离和/或各种数据速率。实现宽的输出信号电平(即,幅度)范围的挑战是电流驱动器设计的输出信号电平(即,幅度)范围受到限制,如下面进一步讨论的。

45.图4示出了具有nfet上nfet架构(简称为“n-over-n”)的驱动器410的示例。驱动器410可以被用于实施图1至3中的驱动器130和150中的每个驱动器(即,驱动器130和驱动器150中的每个驱动器可以是驱动器410的单独实例)。

46.在该示例中,驱动器410包括分别由互补输入信号inn和inp驱动的下拉n型场效应晶体管(nfet)420和上拉nfet 430。下拉nfet 420被配置为当由输入信号inn接通时下拉驱动器410的输出432,并且上拉nfet 430被配置为当由输入信号inp接通时上拉输出432。在操作中,nfet 420和430中的一个nfet一次被接通以将输出432驱动为高或低。

47.驱动器410的输出信号电平(即,幅度)可以通过调整供应给驱动器410的电压来调整(即,调谐)。在这方面,图4示出了一个示例,其中供应给驱动器410的电压是由电压调节器450(例如低压差(ldo)调节器)提供的调节电压vreg。在该示例中,调节电压vreg的电压电平由输入到电压调节器450的电压控制信号控制。由于驱动器410的输出信号电平(即,幅度)取决于供应给驱动器410的调节电压vreg的电压电平(由电压控制信号控制),因此电压控制信号可以被用于调整驱动器410的输出信号电平(即,幅度)。

48.驱动器410支持低输出信号电平,它可以被用于短距离和/或低数据速率以降低功率。然而,驱动器410的上输出信号电平受到限制。这是因为上拉nfet 430(被耦合至输出432)的源极需要低于上拉nfet 430的栅极电压至少上拉nfet 430的阈值电压,以便上拉nfet 430接通。因此,针对芯片110与120之间的长距离和/或高数据速率的情况,驱动器410可能无法实现足够高的输出信号电平(即,幅度)。另外,在静电放电(esd)事件期间,上拉nfet 430不提供从驱动器410的输出432到钳位设备(未示出)的放电路径。因此,驱动器410可能缺乏esd鲁棒性。

49.在图4中的示例中,驱动器410是单端驱动器。然而,要了解的是,驱动器410的差分版本可以通过添加第二上拉nfet和第二下拉nfet来实施,该第二上拉nfet和第二下拉nfet在与输出432相反的方向上驱动驱动器410的第二输出。

50.图5示出了具有pfet上nfet架构(简称为“p-over-n”)的驱动器510的示例。驱动器510可以被用于实施图1至3中的驱动器130和150中的每个驱动器(即,驱动器130和驱动器150中的每个驱动器可以是驱动器510的单独实例)。

51.在该示例中,驱动器510包括下拉n型场效应晶体管(nfet)520和上拉p型场效应晶体管(peft)530,其中下拉nfet 520和上拉pfet 530都由输入信号inn驱动。下拉nfet 520被配置为当由输入信号inn接通时下拉驱动器510的输出532,并且上拉pfet 530被配置为当由输入信号inn接通时上拉输出532。在操作中,下拉nfet 520和上拉pfet 530之一一次被接通以将输出532驱动为高或低。

52.驱动器510的输出信号电平(即,幅度)可以通过调整供应给驱动器510的电压来调整(即,调谐)。在这方面,图5示出了一个示例,其中供应给驱动器510的电压是由上面讨论

的电压调节器450(例如ldo调节器)提供的调节电压vreg。在该示例中,调节电压的电压电平由输入到电压调节器450的电压控制信号控制。由于驱动器510的输出信号电平(即,幅度)取决于供应给驱动器510的调节电压vreg的电压电平(由电压控制信号控制),因此电压控制信号可以被用于调整驱动器510的输出信号电平(即,幅度)。

53.驱动器510支持高输出信号电平,它可以被用于长距离和/或高数据速率。然而,驱动器510的下输出信号电平受到限制。这是因为上拉pfet 530的源极(被耦合至调节电压vreg)需要处于至少等于上拉pfet 530的阈值电压的电压,以便上拉pffet 530接通。这限制了调节电压vreg可以被设置得多低,这又限制了驱动器510的较低输出信号电平。因此,针对芯片110与120之间的短距离和/或低数据速率的情况,驱动器510可能无法实现低输出信号电平(即,幅度)。

54.在图5中的示例中,驱动器510是单端驱动器。然而,要了解的是,驱动器510的差分版本可以通过添加第二下拉nfet和第二上拉pfet来实施,该第二下拉nfet和第二上拉pfet在与输出532相反的方向上驱动驱动器510的第二输出。

55.因此,期望具有比p-over-n驱动器510和n-over-n驱动器410更宽的输出信号电平(即,幅度)范围的驱动器,以支持芯片110与120之间的各种范围和/或各种数据速率。

56.本公开的各个方面提供了一种混合驱动器,它组合了n-over-n驱动器架构和p-over-n驱动器结构,以实现宽的输出信号电平(即,幅度)范围,如下面进一步讨论的。

57.图6示出了根据本公开的各个方面的具有宽输出信号电平(即,幅度)范围的混合驱动器610的示例。混合驱动器610包括下拉nfet 620、上拉nfet 630和上拉pfet 635。在图6中的示例中,下拉nfet 620被耦合在驱动器610的输出625与接地之间,下拉nfet 620的漏极被耦合至输出625,并且下拉nfet 620的源极被耦合至接地。上拉nfet 630被耦合在第一电压轨655与输出625之间,上拉nfet 630的漏极被耦合至第一电压轨655,并且上拉nfet 630的源极被耦合至输出625。上拉pfet 635被耦合在第一电压轨655与输出625之间,上拉pfet 635的源极被耦合至第一电压轨655,并且上拉pfet 635的漏极被耦合至输出625。下拉nfet 620被配置为在接通时下拉输出625,上拉nfet 630被配置为在接通时上拉输出625,并且上拉pfet 635被配置为在接通时上拉输出625,如下面进一步讨论的。

58.混合驱动器610还包括第一开关640、第二开关642、第三开关644和第四开关646。开关640、642、644和646中的每个开关可以用传输门、nfet、pfet或另一类型的开关来实施。在图6中的示例中,第一开关640被耦合在上拉nfet 630的栅极与接地之间,第二开关642被耦合在上拉pfet 635的栅极与第二电压轨660之间,第三开关644被耦合在上拉pfet 635的栅极与驱动器610的第一输入612之间,并且第四开关646被耦合在上拉nfet 630的栅极与驱动器610的第二输入614之间。下拉nfet 620的栅极被耦合至第一输入612。

59.第一输入612和第二输入614分别是由互补输入信号inn和inp驱动的互补输入。在某些方面中,互补输入信号inn和inp可以由预驱动器电路670生成,其示例在图6中示出。在该示例中,预驱动器电路670具有输入672、被耦合至驱动器610的第一输入612的第一输出672以及被耦合至驱动器610的第二输入614的第二输出674。预驱动器电路670可以在输入672处接收输入信号(例如来自第一电路170、第二电路175、第一串行器210或第二串行器230),并且从输入信号生成互补输入信号inn和inp。预驱动器电路670从第一输出672输出输入信号inn,并且从第二输出674输出输入信号inp。

60.如下面进一步讨论的,开关640、642、644和646被配置为在n-over-n驱动器模式与p-over-n驱动器模式之间切换混合驱动器610。在一个示例中,混合驱动器610以n-over-n驱动器模式操作以支持第一幅度范围(例如50mv至400mv),并且以p-over-n驱动器模式操作以支持第二幅度范围(例如425mv至700mv)。在该示例中,混合驱动器610的幅度范围是第一幅度范围和第二幅度范围的组合。这允许混合驱动器610实现宽幅度范围,如下面进一步讨论的。

61.在图6中的示例中,电压调节器650被耦合在第二电压轨660与第一电压轨655之间。电压调节器650被配置为从第二电压轨660上的电源电压vdd生成调节电压vreg。电源电压vdd可以由被耦合至第二电压轨660的电源管理集成电路(pmic)提供。电压调节器650可以用ldo调节器或另一类型的电压调节器来实施。在该示例中,调节电压vreg由输入到电压调节器650的电压控制信号控制。驱动器610的输出信号电平(即,幅度)取决于第一电压轨655上的调节电压vreg。由于输出信号电平(即,幅度)取决于调节电压,并且电压控制信号控制调节电压vreg,因此电压控制信号可以被用于调整(即,调谐)驱动器610的输出信号电平,如下面进一步讨论的。电压控制信号可以是数字控制信号或模拟控制信号。电压控制信号可以来自被耦合至电压调节器650的电压控制电路695。电压控制电路695可以使用电压控制信号来控制驱动器610的输出信号电平,例如基于输入信号inn和inp的数据速率和/或第一芯片110与第二芯片120之间的距离。例如,控制电路695可以针对较高的数据速率增加输出信号电平和/或针对第一芯片110与第二芯片120之间的较长距离增加输出信号电平。

62.在图6中的示例中,输出625经由电阻器648被耦合至输出引脚690。输出引脚690可以被耦合至链路(例如链路122或124),并且可以对应于输出引脚135或155。电阻器648可以被配置为在驱动器610与被耦合至输出引脚690的链路(图6中未示出)之间提供阻抗匹配。

63.在该示例中,开关控制电路680控制开关640、642、644和646,以选择性地在n-over-n驱动器模式或p-over-n驱动器模式下操作混合驱动器610。为了便于图示,开关控制电路680与开关640、642、644和646之间的单独连接未在图6中明确示出。

64.为了在n-over-n驱动器模式下操作混合驱动器610,开关控制电路680接通第二开关642并且关断第三开关644。这关断上拉pfet635并且将上拉pfet 635的栅极与第一输入612去耦。开关控制电路680还关断第一开关640并且接通第四开关646,以将上拉nfet 630的栅极耦合至第二输入614。在n-over-n驱动器模式下,混合驱动器610实施图4所图示的n-over-n驱动器410,它支持低输出信号电平(即,低幅度)。

65.为了在p-over-n驱动器模式下操作混合驱动器610,开关控制电路680关断第二开关642并且接通第三开关644,以将上拉pfet 635的栅极耦合至第一输入612。开关控制电路680还接通第一开关640并且关断第四开关646。这关断上拉nfet 630并且将上拉nfet 630的栅极与第二输入614去耦。在p-over-n驱动器模式下,混合驱动器610实施图5所图示的p-over-n驱动器510,它支持高输出信号电平。

66.在某些方面中,开关控制电路680基于第一电压轨655上的调节电压vreg在n-over-n驱动器模式或p-over-n驱动器模式下操作混合驱动器610。如上面讨论的,驱动器610的幅度取决于调节电压vreg。在该示例中,如果调节电压vreg在与驱动器610的第一幅度范围(例如50mv至400mv)相对应的第一调节电压范围内,那么开关控制电路680以n-over-n驱动器模式操作混合驱动器610。如果调节电压vreg在与驱动器610的第二幅度范围

(例如425mv至700mv)相对应的第二调节电压范围内,那么开关控制电路680以p-over-n驱动器模式操作混合驱动器610。如上面讨论的,混合驱动器610的幅度范围是第一幅度范围和第二幅度范围的组合,这允许混合驱动器610实现宽幅度范围。

67.由于调节电压vreg由电压控制信号控制,因此开关控制电路680可以基于电压控制信号在n-over-n驱动器模式或p-over-n驱动器模式下操作混合驱动器610。在这方面,图6示出了电压控制信号被输入到开关控制电路680的示例。在该示例中,当电压控制信号将调节电压vreg设置为与驱动器610的第一幅度范围(例如50mv至400mv)相对应的第一调节电压范围内的电压电平时,开关控制电路680以n-over-n驱动器模式操作混合驱动器610。当电压控制信号将调节电压vreg设置为与驱动器610的第二幅度范围(例如425mv至700mv)相对应的第二调节电压范围内的电压电平时,开关控制电路680以p-over-n驱动器模式操作混合驱动器610。因此,在该示例中,电压控制信号可以被用于控制混合驱动器610的幅度和混合驱动器610的驱动器模式。

68.在某些方面中,电压控制信号是数字控制信号(也称为数字代码),其中调节电压vreg的电压电平由电压控制信号的值设置。在一个示例中,电压控制信号包括n位。在该示例中,电压控制信号具有2n个可能值,其中2n个可能值中的每个可能值对应于调节电压vreg的2n个可选电压电平中的一个相应电压电平。因此,在该示例中,电压控制电路695可以通过将电压控制信号(例如数字代码)设置为对应值来将调节电压vreg设置为2n个可选电压电平中的任何一个。

69.在一个示例中,电压控制信号的第一组值对应于第一调节电压范围内的电压电平,并且电压控制信号的第二组值对应于第二调节电压范围内的电压电平。如上面讨论的,第一调节电压范围对应于驱动器610的第一幅度范围(例如50mv至400mv),并且第二调节电压范围对应于驱动器610的第二幅度范围(例如425mv至700mv)。因此,在该示例中,第一组值覆盖第一幅度范围,并且第二组值覆盖第二幅度范围。在该示例中,如果电压控制信号的电流值在第一组值中(即,电压控制信号具有第一组值中的一个值),则开关控制电路680可以被配置为以n-over-n驱动器模式操作驱动器610,并且如果电压控制信号的电流值在第二组值中(即,电压控制信号具有第二组值中的一个值),则以p-over-n驱动器模式操作驱动器610。

70.在一个示例中,电压控制信号包括五个位,32个可能值的范围从0到31。该情况的示例在图7中图示,其中电压控制信号被标记为v《4:0》,指示电压控制信号包括五个位。在该示例中,第一组值可以包括值0至23,并且第二组值可以包括值24至31。因此,在该示例中,值0至23覆盖驱动器610的第一幅度范围(例如50mv至400mv),并且值24至31覆盖驱动器610的第二幅度范围(例如425mv至700mv)。在该示例中,如果电压控制信号的电流值在0至23的范围内,则开关控制电路680以n-over-n驱动器模式操作驱动器610,并且如果电压控制信号的电流值在24至31的范围内,则以p-over-n驱动器模式操作驱动器610。

71.在图7中的示例中,开关控制电路680由与门710实施,该与门710包括第一输入712、第二输入714和输出716。第一输入712接收电压控制信号的第二最高有效位v《3》,并且第二输入714接收电压信号的最高有效位v《4》。在该示例中,与门710对位v《3》和v《4》执行and运算,以生成开关640、642、644和646的控制信号。当位v《3》和v《4》都为1时,与门710输出1,这在电压控制信号的值在24至31的范围内(即,电压控制信号的值在对应于第二幅度

范围的第二组值中)时发生。当位v《3》和v《4》中的一个位为0时,或者位v《3》和v《4》都为0时,与门710输出0,这在电压控制信号的值在0到23的范围内(即,电压控制信号的值在对应于第一幅度范围的第一组值中)时发生。因此,当电压控制信号的值在24至31的范围内时,与门710输出1,并且当电压控制信号的值在0至23的范围内时,输出0。在该示例中,开关640、642、644和646被配置为使得当开关控制信号输出1时,第一开关640和第三开关644接通,并且第二开关642和第四开关646关断。当电压控制信号的值在24至31的范围内时,这使驱动器610在p-over-n驱动器模式下操作。开关640、642、644和646被配置为使得当开关控制信号输出0时,第一开关640和第三开关644关断,并且第二开关642和第四开关646接通。当电压控制信号的值在0至23的范围内时,这使驱动器610以n-over-n驱动器模式操作驱动器。

72.要了解的是,开关控制电路680不被限于图7所示的示例性实施方式。开关控制电路680可以用各种逻辑门和/或逻辑门的各种组合来实施。而且,要了解的是,在其他实施方式中,电压控制信号可以包括少于五位或多于五位。

73.图6所示的示例性混合驱动器610可以被用于实施多切片混合驱动器805,其示例在图8中示出。在该示例中,多切片混合驱动器805包括被并行耦合在第一电压轨655与接地之间的多个切片810-1至810-m。切片810-1至810-m中的每个切片用图6所示的示例性混合驱动器610实施(即,切片810-1至810-m中的每个切片是图6所示的混合驱动器610的单独实例)。如图8所示,切片810-1至810-m的输出625经由电阻器848被耦合至输出引脚890(即,电阻器848被耦合在切片810-1至810-m的输入625与输出引脚890之间)。输出引脚890可以被耦合至链路(例如链路122或124),并且可以对应于输出引脚135或155。

74.切片810-1至810-m的第一输入612被耦合至多切片混合驱动器805的第一输入812,并且切片810-1至810-m的第二输入614被耦合至多切片混合驱动器805的第二输入814。第一输入812和第二输入814分别由互补输入信号inn和inp驱动。

75.开关控制电路680(如图6所示)控制切片810-1至810-m中的开关640、642、644和646,以选择性地在n-over-n驱动器模式或p-over-n驱动器模式下操作多切片混合驱动器805。例如,当调节电压vreg处于对应于第一幅度范围(例如50mv至400mv)的第一调节电压范围内时,开关控制电路680可以在n-over-n驱动器模式下操作多切片混合驱动器805,并且当调节电压vreg处于对应于第二幅度范围(例如425mv至700mv)的第二调节电压范围内时,在p-over-n驱动器模式下操作多切片混合驱动器805。注意,电压调节器650未在图8中示出。

76.在某些方面中,在给定时间活动(即,启用)的切片810-1至810-m的数量可以被调整(例如使用开关)。例如,活动(即,启用)的切片810-1至810-m的数量可以被调整,以调整多切片混合驱动器805的输出阻抗。在该示例中,多切片混合驱动器805的输出阻抗可以被调整(即,校准),以提供与被耦合至输出引脚890的链路(例如链路122或124)的阻抗匹配。

77.图9示出了根据某些方面的差分混合驱动器905。差分驱动器905包括第一分支910a和第二分支910b。第一分支910a和第二分支910b中的每个分支可以用图6所示的混合驱动器610实施(即,每个分支可以是混合驱动器610的单独实例)。在图9中,第一分支910a的元件的附图标记包括字母“a”,并且第二分支910b的元件的附图标记包括字母“b”。如下面进一步讨论的,第一分支910a和第二分支910b在相反方向上被驱动,以生成差分输出信

号。

78.第一分支910a包括第一下拉nfet 620a、第一上拉nfet 630a和第一上拉pfet 635a。第一下拉nfet 620a被耦合在第一输出625a与接地之间,第一下拉nfet 620a的漏极被耦合至第一输出625a,并且第一下拉nfet 620的源极被耦合至接地。第一上拉nfet 630a被耦合在第一电压轨655与第一输出625a之间,第一上拉nfet 630a的漏极被耦合至第一电压轨655,并且第一上拉nfet 630a的源极被耦合至第一输出625a。第一上拉pfet 635a被耦合在第一电压轨655与第一输出625a之间,第一上拉pfet 635a的源极被耦合至第一电压轨655,并且第一上拉pfet 635a的漏极被耦合至第一输出625a。

79.第二分支910b包括第二下拉nfet 620b、第二上拉nfet 630b和第二上拉pfet 635b。第二下拉nfet 620b被耦合在第二输出625b与接地之间,第二下拉nfet 620b的漏极被耦合至第二输出625b,并且第二下拉nfet 620b的源极被耦合至接地。第二上拉nfet 630b被耦合在第一电压轨655与第二输出625b之间,第二上拉nfet 630b的漏极被耦合至第一电压轨655,并且第二上拉nfet 630b的源极被耦合至第二输出625b。第二上拉pfet 635b被耦合在第一电压轨655与第二输出625b之间,第二上拉pfet 635b的源极被耦合至第一电压轨655,并且第二上拉pfet 635b的漏极被耦合至第二输出625b。

80.在图9中的示例中,驱动器905包括被耦合在第一上拉nfet 630a的栅极与接地之间的第一开关640a、被耦合在第二上拉nfet 630b的栅极与接地之间的第二开关640b、被耦合在第一下拉pfet 635a的栅极与第二电压轨660之间的第三开关642a以及被耦合在第二上拉pfet 635b的栅极与第二电压轨660之间的第四开关642b。驱动器905还包括被耦合在第一上拉pfet 635a的栅极与驱动器905的第一输入912之间的第五开关644a、被耦合在第二上拉pfet 635b的栅极与驱动器905的第二输入914之间的第六开关644b、被耦合在第一上拉nfet 630a的栅极与第二输入914之间的第七开关646a以及被耦合在第二上拉nfet 630b的栅极与第一输入912之间的第八开关646b。第一下拉nfet 620a的栅极被耦合至第一输入912,并且第二下拉nfet 620b的栅极被耦合至第二输入914。

81.第一输入912和第二输入914分别是由互补输入信号inn和inp驱动的互补输入。如上面讨论的,互补输入信号inn和inp可以由预驱动器电路670(如图6所示)提供。在该示例中,预驱动器电路670的第一输出672可以被耦合至第一输入912,并且预驱动器电路670的第二输出674可以被耦合至第二输入914。

82.在该示例中,第二分支910b的输入相对于第一分支910a的输入反向,使得互补输入信号inn和inp在相反方向上驱动第一分支910a和第二分支910b,以生成差分输出信号。更具体地,输入信号inn驱动第一分支910a中的第一下拉nfet 620a,并且输入信号inp驱动第二分支910b中的第二下拉nfet 620b。在n-over-n驱动器模式下,输入信号inp驱动第一分支910a中的第一上拉nfet 630a,并且输入信号inn驱动第二分支910b中的第二上拉nfet 630b。在p-over-n驱动器模式下,输入信号inn驱动第一分支910a中的第一上拉pfet 635a,并且输入信号inp驱动第二分支910b中的第二上拉pfet 635b。

83.在图9中的示例中,第一输出625a经由第一电阻器948a被耦合至第一输出引脚990a(即,第一电阻器948a被耦合在第一输出625a与第一输出引脚990a之间)。第二输出625b经由第二电阻器948b被耦合至第二输出引脚990b(即,第二电阻器948b被耦合在第二输出端625b与第二输出引脚990b之间)。第一输出引脚990a和第二输出引脚990b可以被耦

合至差分链路,其中第一输出引脚990a被耦合至差分链路的第一传输线(例如传输线312a或314a),并且第二输出引脚990b被耦合至差分链路的第二传输线(例如传输线312b或314b)。

84.在该示例中,开关控制电路680控制第一分支910a和第二分支920中的开关,以选择性地在n-over-n驱动器模式或p-over-n驱动器模式下操作差分混合驱动器905。为了便于图示,开关控制电路680与开关之间的单独连接未在图9中明确示出。

85.为了在n-over-n驱动器模式下操作差分混合驱动器905,开关控制电路680关断第一开关640a,关断第二开关640b,接通第三开关642a,接通第四开关642b,关断第五开关644a,关断第六开关644b,接通第七开关646a,并且接通第八开关646b。这将第一上拉nfet 630a的栅极耦合至第二输入914,将第二上拉nfet 630b的栅极耦合至第一输入912,并且关断第一上拉pfet 635a和第二上拉pfet 635b。在n-over-n驱动器模式下,差分混合驱动器905实施差分n-over-n驱动器。

86.为了在p-over-n驱动器模式下操作差分混合驱动器905,开关控制电路680接通第一开关640a,接通第二开关640b,关断第三开关642a,关断第四开关642b,接通第五开关644a,接通第六开关644b,关断第七开关646a,并且关断第八开关646b。这将第一上拉pfet 635a的栅极耦合至第一输入912,将第二上拉pfet 635b的栅极耦合至第二输入914,并且关断第一上拉nfet 630a和第二上拉nfet630b。在p-over-n驱动器模式下,差分混合驱动器905实施差分p-over-n驱动器。

87.开关控制电路680可以基于第一电压轨655上的调节电压vreg在n-over-n驱动器模式或p-over-n驱动器模式下操作差分混合驱动器905。例如,如果调节电压vreg在对应于驱动器905的第一幅度范围(例如50mv至400mv)的第一调节电压范围内,那么开关控制电路680以n-over-n驱动器模式操作混合驱动器905。如果调节电压vreg在与驱动器905的第二幅度范围(例如425mv至700mv)相对应的第二调节电压范围内,那么开关控制电路680以p-over-n驱动器模式操作混合驱动器905。

88.由于调节电压vreg由电压控制信号控制,因此开关控制电路680可以基于电压控制信号在n-over-n驱动器模式或p-over-n驱动器模式下操作混合驱动器905。在这方面,图9示出了电压控制信号被输入到开关控制电路680的示例。在该示例中,当电压控制信号将调节电压vreg设置为与驱动器905的第一幅度范围(例如50mv至400mv)相对应的第一调节电压范围内的电压电平时,开关控制电路680以n-over-n驱动器模式操作混合驱动器905。当电压控制信号将调节电压vreg设置为与驱动器905的第二幅度范围(例如425mv至700mv)相对应的第二调节电压范围内的电压电平时,开关控制电路680以p-over-n驱动器模式操作混合驱动器905。

89.如上面讨论的,电压控制信号可以是数字控制信号(也称为数字代码),其中调节电压vreg的电压电平由电压控制信号的值设置。在一个示例中,电压控制信号的第一组值对应于第一调节电压范围内的电压电平,并且电压控制信号的第二组值对应于第二调节电压范围内的电压电平。如上面讨论的,第一调节电压范围对应于驱动器905的第一幅度范围(例如50mv至400mv),并且第二调节电压范围对应于驱动器905的第二幅度范围(例如425mv至700mv)。因此,在该示例中,第一组值覆盖第一幅度范围,并且第二组值覆盖第二幅度范围。在该示例中,开关控制电路680可以被配置为如果电压控制信号的电流值在第一组值

中,则以n-over-n驱动器模式操作驱动器905,并且如果电压控制信号的电流值在第二组值中,则以p-over-n驱动器模式操作驱动器905。

90.图9所示的示例性差分混合驱动器905可以被用于实施多切片混合驱动器1005,其示例在图10中示出。在该示例中,多切片混合驱动器1005包括被并行耦合在第一电压轨655与接地之间的多个切片1010-1至1010-m。切片1010-1至1010-m中的每个切片用图9所示的示例性差分混合驱动器905实施(即,切片1010-1至1010-m中的每个切片是图9所示的差分混合驱动器905的单独实例)。注意,为了便于图示,差分混合驱动器905的细节未在图10中示出。

91.如图10所示,切片1010-1至1010-m的第一输出625a经由第一电阻器1048a被耦合至第一输出引脚1090a(即,第一电阻器1048a被耦合在切片1010-1至1010-m的第一输出625a与第一输出引脚1090a之间)。切片1010-1至1010-m的第二输出625b经由第二电阻器1048b被耦合至第二输出引脚1090b(即,第二电阻器1048b被耦合在切片1010-1至1010-m的第二输出625b与第二输出引脚1090b之间)。第一输出引脚1090a和第二输出引脚1090b可以被耦合至差分链路,其中第一输出引脚1090a被耦合至差分链路的第一传输线(例如传输线312a或314a),并且第二输出引脚1090b被耦合至差分链路的第二传输线(例如传输线312b或314b)。

92.切片1010-1至1010-m的第一输入912被耦合至多切片混合驱动器1005的第一输入1012,并且切片1010-1至1010-m的第二输入914被耦合至多切片混合驱动器1005的第二输入1014。第一输入1012和第二输入1014分别由互补输入信号inn和inp驱动。

93.开关控制电路680(如图9所示)控制切片1010-1至1010-m中的开关,以选择性地在n-over-n驱动器模式或p-over-n驱动器模式下操作多切片混合驱动器1005。例如,当调节电压vreg处于对应于第一幅度范围(例如50mv至400mv)的第一调节电压范围内时,开关控制电路680可以在n-over-n驱动器模式下操作多切片混合驱动器1005,并且当调节电压vreg处于对应于第二幅度范围(例如425mv至700mv)的第二调节电压范围内时,在p-over-n驱动器模式下操作多切片混合驱动器1005。注意,电压调节器650未在图10中示出。

94.在某些方面中,在给定时间活动(即,启用)的切片1010-1至1010-m的数量可以被调整(例如使用开关)。例如,活动(即,启用)的切片1010-1至1010-m的数量可以被调整,以调整多切片混合驱动器1005的每个输出处的输出阻抗。在该示例中,多切片混合驱动器1005的每个输出处的输出阻抗可以被调整(即,校准),以提供与被耦合至输出引脚1090a和1090b中的一个相应输出引脚的传输线的阻抗匹配。

95.如上面讨论的,电压调节器650可以用低压差(ldo)调节器来实施。ldo调节器通常包括一个传输晶体管和一个误差放大器,其中误差放大器的输出基于参考电压和调节电压的反馈来驱动传输晶体管的栅极。传输晶体管可以是传输nfet或传输pfet。

96.图11示出了ldo调节器1105的示例,它包括传输nfet 1110、放大器1120、电压参考电路1140和分压器1135。传输nfet 1110被耦合在第一电压轨655与第二电压轨660之间。分压器1135包括被串行耦合在第一电压轨655与接地之间的第一电阻器r1和第二电阻器r2。分压器1135在节点1130处提供如下给出的反馈电压vfb:

97.98.其中等式(1)中的r1和r2分别是电阻器r1和r2的电阻。如等式(1)所示,反馈电压vfb与调节电压vreg成比例,因此提供调节电压vreg的反馈。反馈电压vfb被馈送到放大器1120的负输入。电压参考电路1140被配置为生成被输入到放大器1120的正输入的参考电压vref。电压参考电路1140被配置为基于电压控制信号设置参考电压vref的电压电平。如下面进一步讨论的,调节电压vreg通过使用电压控制信号调整参考电压vref来调整。

99.在操作中,放大器1120接收反馈电压vfb和参考电压vref。放大器1120在减小参考电压与反馈电压vfb之间的差异的方向上驱动传输nfet 1110的栅极,使得第一电压轨655上的调节电压vreg近似等于:

[0100][0101]

如等式(2)所示,调节电压vreg与参考电压vref成比例。因此,电压控制信号可以被用于通过调整由电压参考电路1140生成的参考电压vref来调整调节电压vreg。

[0102]

ldo调节器1105支持可以被用于将混合驱动器(例如混合驱动器610、805、905或1005)的幅度设置为低的低调节电压电平。然而,调节器1105的上调节电压电平受到限制。这是因为传输nfet 1110(被耦合至第一电压轨655)的源极需要低于传输nfet 1110的栅极电压至少传输nfet 1110的阈值电压,以便传输nfet 1110接通。因此,ldo调节器1105可能无法将混合驱动器的幅度设置为高,从而减小混合驱动器的幅度范围。

[0103]

图12示出了ldo调节器1205的示例,它包括传输pfet 1210、放大器1220、电压参考电路1140和分压器1135。传输pfet 1210被耦合在第一电压轨655与第二电压轨660之间。在该示例中,反馈电压vfb被输入到放大器1220的正输入,并且来自电压参考电路1140的参考电压vref被输入到放大器1220的负输入。

[0104]

在操作中,放大器1220接收反馈电压vfb和参考电压vref。放大器1220在减小参考电压与反馈电压vfb之间的差异的方向上驱动传输pfet 1210的栅极,使得第一电压轨655上的调节电压vreg与参考电压vref成比例(例如基于等式(2))。由于电压控制信号控制由电压参考电路1140生成的参考电压vref,因此电压控制信号可以被用于通过调整参考电压vref来调整调节电压vreg。

[0105]

ldo调节器1205支持可以被用于将混合驱动器(例如混合驱动器610、805、905或1005)的幅度设置为高的高调节电压电平。然而,与使用传输nfet 1110的ldo调节器1105相比,ldo调节器1205的较低调节电压电平受到限制。因此,ldo调节器1205可能无法将混合驱动器的幅度设置为低,从而减小混合驱动器的幅度范围。

[0106]

为了解决ldo调节器1105和1205的限制,本公开的各个方面提供了一种混合ldo调节器,它组合传输nfet和传输pfet以实现宽的调节电压范围,如下面进一步讨论的。

[0107]

图13示出了根据本公开的各个方面的混合ldo调节器1310的示例。混合ldo调节器1310可以被用于实施电压调节器650。混合ldo调节器1310被配置为从第二电压轨660上的电源电压vdd生成第一电压轨655上的调节电压vreg。如上面讨论的,第一电压轨655可以被耦合至混合驱动器610、805、905或1005。

[0108]

混合ldo调节器1310包括传输nfet 1320、传输pfet 1330、第一放大器1340、第二放大器1350、第一开关1322、第二开关1324、第三开关1332、第四开关1334、第五开关1328、第六开关1338、分压器1335和电压参考电路1360。传输nfet 1320被耦合在第一电压轨655

与第二电压轨660之间,传输nfet 1320的漏极被耦合至第二电压轨660,并且传输nfet 1320的源极被耦合至第一电压轨655。传输pfet 1330被耦合在第一电压轨655与第二电压轨660之间,传输pfet 1330的源极被耦合至第二电压轨660,并且传输pfet 1330的漏极被耦合至第一电压轨655。第一放大器1340和第二放大器1350中的每个放大器可以是单级或多级放大器。而且,第一放大器1340和第二放大器1350中的每个放大器都可以用共源共栅放大器、折叠式共源共栅放大器或另一类型的放大器来实施。

[0109]

分压器1335包括被串行耦合在第一电压轨655与接地之间的第一电阻器r1和第二电阻器r2。分压器1335在反馈节点1333处提供由上面提供的等式(1)给出的反馈电压vfb。

[0110]

第一开关1322被耦合在第一放大器1340的输出1346与传输nfet 1320的栅极之间,第二开关1324被耦合在第二放大器1350的输出与传输pfet 1330的栅极之间,第三开关1332被耦合在传输nfet 1320的栅极与接地之间,并且第四开关1334被耦合在传输pfet 1330的栅极与第二电压轨660之间。而且,第五开关1328被耦合在反馈节点1333与第一放大器1340的第一输入1342之间,并且第六开关1338被耦合在反馈节点1333与第二放大器1350的第一输入1352之间。

[0111]

电压参考电路1360被配置为在输入1362处接收电压控制信号(例如来自图6所示的电压控制电路695),并且基于接收到的电压控制信号在输出1364处生成参考电压vref。在某些方面中,电压参考电路1360被配置为基于电压控制信号设置参考电压vref的电压电平。针对电压控制信号是数字信号的示例,电压参考电路1360可以具有多个可选参考电压电平,其中可选参考电压电平中的每个参考电压电平对应于控制信号的不同值。在该示例中,电压参考电路1360将参考电压vref的电压电平设置为与控制信号的电流值相对应的可选参考电压电平中的一个参考电压电平。如下面进一步讨论的,调节电压vreg通过使用电压控制信号调整参考电压vref来调整。根据上面提供的等式(2),调节电压vreg可以与参考电压vref相关。针对电压控制信号是数字信号(也称为数字代码)的示例,电压参考电路1360可以用数模转换器(dac)实施。电压参考电路1360的示例性实施方式在下面讨论。

[0112]

电压参考电路1360的输出1364被耦合至第一放大器1340的第二输入1344和第二放大器1350的第二输入1354。因此,参考电压vref被输入到第一放大器1340的第二输入1344和第二放大器1350的第二输入1354。

[0113]

如下面进一步讨论的,开关1322、1324、1328、1332、1334和1338被配置为在第一调节模式与第二调节模式之间切换混合ldo调节器1310。在第一调节模式下,在传输pfet 1330关断的情况下,传输nfet 1320被用作混合ldo调节器1310的传输晶体管,并且在第二调节模式下,在传输nfet 1320关断时,传输pfet 1330被用作混合ldo调节器1310的传输晶体管。在一个示例中,当调节电压处于第一调节电压范围内时,混合ldo调节器1310可以以第一调节模式操作,并且当调节电压处于第二调节电压范围内时,以第二调节模式操作。在该示例中,混合ldo调节器1310的调节电压范围是第一调节电压范围和第二调节电压范围的组合,这允许混合ldo调节器1310实现宽的调节电压范围,如下面进一步讨论的。

[0114]

开关控制电路1380控制开关1322、1324、1328、1332、1334和1338,以在第一调节模式或第二调节模式选择性地操作混合ldo调节器1310(例如基于电压控制信号)。为了便于图示,开关控制电路1380与开关1322、1324、1328、1332、1334和1338之间的单独连接未在图13中明确示出。在一些实施方式中,开关控制电路1380可以与用于控制混合驱动器610、

805、905或1005的驱动器模式的开关控制电路680相同,如下面进一步讨论的。

[0115]

为了在第一调节模式下操作混合ldo调节器1310,开关控制电路1380接通第一开关1322,关断第二开关1324,关断第三开关1332,并且接通第四开关1334。这将第一放大器1340的输出耦合至传输nfet 1320的栅极,并且关断传输pfet 1330。而且,开关控制电路1380接通第五开关1328并且关断第六开关1338。这将反馈节点1333耦合至第一放大器1340的第一输入1342,并且将反馈节点1333与第二放大器1350的第一输入1352去耦。

[0116]

在第一调节模式下,第一放大器1340在第一输入1342处接收反馈电压vfb,并且在第二输入1344处接收参考电压vref。第一放大器1340在减小参考电压与反馈电压vfb之间的差异的方向上驱动传输nfet 1320的栅极,使得第一电压轨655上的调节电压vreg近似与参考电压vref成比例(例如基于等式(2))。由于参考电压vref由电压控制信号控制,并且调节电压vreg与参考电压vef成比例,因此电压控制信号可以被用于调整调节电压vreg。在第一调节模式下,传输nfet 1320允许混合ldo调节器1310实现具有高电源噪声抑制的低调节电压。

[0117]

为了在第二调节模式下操作混合ldo调节器1310,开关控制电路1380关断第一开关1322,接通第二开关1324,接通第三开关1332,并且关断第四开关1334。这将第二放大器1350的输出耦合至传输pfet 1330的栅极,并且关断传输nfet 1320。而且,开关控制电路1380关断第五开关1328并且接通第六开关1338。这将反馈节点1333耦合至第二放大器1350的第一输入1352,并且将反馈节点1333与第一放大器1340的第一输入1342去耦。

[0118]

在第二调节模式下,第二放大器1350在第一输入1352处接收反馈电压vfb,并且在第二输入1354处接收参考电压vref。第二放大器1350在减小参考电压与反馈电压vfb之间的差异的方向上驱动传输pfet 1330的栅极,使得第一电压轨655上的调节电压vreg近似与参考电压vref成比例(例如基于等式(2))。由于参考电压vref由电压控制信号控制,并且调节电压vreg与参考电压vef成比例,因此电压控制信号可以被用于调整调节电压vreg。在第二调节模式下,传输pfet 1330允许混合ldo调节器1310实现高调节电压(例如接近vdd)。

[0119]

如上面讨论的,开关控制电路1380可以基于电压控制信号在第一调节模式或第二调节模式下操作混合ldo调节器1310。在这方面,图13示出了电压控制信号被输入到开关控制电路1380的示例。在该示例中,当电压控制信号将调节电压vreg设置为第一调节电压范围内的电压电平时,开关控制电路1380在第一调节模式下操作混合ldo调节器1310,并且当电压控制信号将调节电压vreg设置为第二调节电压范围内的电压电平时,在第二调节模式下操作混合ldo调节器1310。在一个示例中,第一调节电压范围对应于混合驱动器610、805、905或1005的第一幅度范围(例如50mv至400mv),并且第二调节电压范围对应于混合驱动器610、805、905或1005的第二幅度范围(例如425mv至700mv)。在该示例中,当混合驱动器610、805、905或1005处于n-over-n驱动器模式时,开关控制电路1380在第一调节模式下操作混合ldo调节器1310,并且当混合驱动器610、805、905或1005处于p-over-n驱动器模式时,在第二调节模式下操作混合ldo调节器1310。因此,在该示例中,第一调节模式与n-over-n驱动器模式一致,并且第二调节模式与p-over-n驱动器模式一致,这允许混合ldo调节器1310的调节模式和混合驱动器的驱动器模式由同一开关控制电路控制。因此,在该示例中,开关控制电路1380可以与用于控制混合驱动器610、805、905或1005的驱动器模式的开关控制电路680相同。然而,要了解的是,本公开不被限于该示例。

[0120]

在某些方面中,电压控制信号是数字信号(也称为数字代码),其中调节电压vreg的电压电平由电压控制信号的值设置。在一个示例中,电压控制信号的第一组值对应于第一调节电压范围内的电压电平,并且电压控制信号的第二组值对应于第二调节电压范围内的电压电平。在该示例中,开关控制电路1380可以被配置为如果电压控制信号的电流值在第一组值中,则在第一调节模式下操作混合ldo调节器1310,并且如果电压控制信号的电流值在第二组值中,则操作混合ldd调节器1310。开关控制电路1380还可以被配置为如果电压控制信号的电流值在第一组值中,则以n-over-n驱动器模式操作混合驱动器610、805、905或1005,并且如果电压控制信号的电流值在第二组值中,则以p-over-n驱动器模式操作混合驱动器。

[0121]

尽管混合ldo调节器1310在上面使用混合ldo调节器1310向混合驱动器提供调节电压vreg的示例讨论,但要了解的是,混合ldo1310不被限于该示例。混合ldo调节器1310可以被用于期望提供可以在宽电压范围内调整的调节电压的其他应用中。

[0122]

图14示出了混合ldo调节器1310的示例,它进一步包括第一补偿电路1410、第七开关1415和第二补偿电路1420。第一补偿电路1410被耦合在传输nfet 1320的栅极与接地之间。在图14中的示例中,第一补偿电路1410包括串行耦合的电阻器1414和补偿电容器1412。第一补偿电路1410可以被配置为在第一调节模式下提供环路补偿以增加ldo调节器1310的相位裕度和环路稳定性。

[0123]

第二补偿电路1420被耦合在传输pfet 1330的栅极与第七开关1415之间,并且第七开关1415被耦合在第二补偿电路1420与传输pfet 1330的漏极之间。在图14中的示例中,第二补偿电路1420包括串行耦合的电阻器1424和补偿电容器1422。

[0124]

开关控制电路1380(如图13所示)可以被配置为在第一调节模式下关断第七开关1415,并且在第二调节模式下接通第七开关1415。因此,在该示例中,在第二调节模式下,第二补偿电路1420被耦合在传输pfet 1330的栅极与传输pfet 1330的漏极之间,以提供米勒补偿以提高环路稳定性。

[0125]

因此,在该示例中,单独的补偿电路(即,第一补偿电路1410和第二补偿电路1420)被用于第一调节模式和第二调节模式,而不是用于两种调节模式的共享补偿电路。这允许用于第一调节模式和第二调节模式的补偿方案被独立地设计,以为第一调节模式提供良好的环路稳定性并且为第二调节模式提供良好的环路稳定性。

[0126]

图15示出了根据本公开的某些方面的电压参考电路1360的示例性实施方式。在该示例中,电压参考电路1360包括电流源1510和可变电阻器1520。电流源1510被耦合在第二电压轨660与电压参考电路1360的输出1364之间,并且可变电阻器1520被耦合在电压参考电路1360的输出1364与接地之间。

[0127]

在该示例中,可变电阻器1520具有数字控制电阻,该数字控制电阻由在输入1362处接收的电压控制信号控制。可变电阻器1520可以包括多个电阻器和多个开关,其中开关控制在给定时间哪个电阻器对可变电阻器1520的电阻有贡献。在该示例中,开关中的每个开关可以由电压控制信号的相应位控制。在该示例中,参考电压vref由以下给出:

[0128]

vref=i.rv

ꢀꢀꢀ

(3)

[0129]

其中i是电流源1510的电流,并且rv是可变电阻器1520的电阻。如等式(3)所示,电压控制信号通过控制可变电阻器1520的电阻来控制参考电压。

[0130]

图16示出了根据本公开的某些方面的电压参考电路1360的另一示例性实施方式。在该示例中,电压参考电路1360包括参考电阻器1610和可变电阻器1520。参考电阻器1610被耦合在第二电压轨660与电压参考电路1360的输出1364之间,并且可变电阻器1520被耦合在电压参考电路1360的输出1364与接地之间。参考电阻器1610可以具有固定电阻。

[0131]

如上面讨论的,可变电阻器1520具有由在输入1362处接收的电压控制信号控制的数字控制电阻。在该示例中,参考电压vref由以下给出:

[0132][0133]

其中rf是参考电阻器1610的电阻,并且rv是可变电阻器1520的电阻。如等式(4)所示,电压控制信号通过控制可变电阻器1520的电阻来控制参考电压。

[0134]

图17示出了根据本公开的某些方面的电压参考电路1360的示例性实施方式,该电压参考电路1360组合了图15和图16所示的示例性实施方式的元件。在该示例中,电压参考电路1360包括电流源1510、参考电阻器1610、可变电阻器1520、第一晶体管1710、第二晶体管1720和反相器1715。在图17中的示例中,第一晶体管1710和第二晶体管1720中的每个晶体管都用pfet实施。

[0135]

电流源1510被耦合在第二电压轨660与第一晶体管1710之间,并且第一晶体管1710被耦合在电流源1510与电压参考电路1360的输出1364之间。第二晶体管1720被耦合在第二电压轨660与参考电阻器1610之间,并且参考电阻器1610被耦合在第二晶体管1720与电压参考电路1360的输出1364之间。可变电阻器1520被耦合在电压参考电路1360的输出1364与接地之间。

[0136]

第一晶体管1710的栅极被耦合至参考模式选择输入1735。反相器1715的输入被耦合至参考模式选择输入1735,并且反相器1715的输出被耦合至第二晶体管1720的栅极。

[0137]

电压参考电路1360被配置为基于在参考模式选择输入1735处接收的参考模式选择信号(标记为“ref_mode”)在第一参考模式或第二参考模式下操作。在图17中的示例中,当参考模式选择信号为低时,电压参考电路1360以第一参考模式操作。在这种情况下,第一晶体管1710接通,并且第二晶体管1720关断。这使第一晶体管1710将电流源1510耦合至可变电阻器1520。在该模式下,参考电压vref由等式(3)给出。当参考模式选择信号为高时,电压参考电路1360以第二参考模式操作。在这种情况下,第一晶体管1710关断,并且第二晶体管1720接通。这使第二晶体管1720将参考电阻器1610耦合在第二电压轨660与可变电阻器1520之间。在该模式下,参考电压vref由等式(4)给出。

[0138]

示例性混合驱动器610、805、905或1005和混合ldo调节器1310提供esd鲁棒性,如下面进一步讨论的。如图18所示,当静电荷从外部源(例如在处理芯片期间)无意地转移到芯片(例如芯片110或120)的输出引脚1890时,可能发生esd。输出引脚1890可以对应于输出引脚690、890、990a、990b、1090a或1090b。被耦合至输出引脚1890的电阻器1848可以对应于电阻器648、848、948a、948b、1048a或1048b。

[0139]

参照图18,芯片可以包括二极管1810和钳位设备1820,以提供esd保护。二极管1810被耦合在输出引脚1890与第二电压轨660之间,并且钳位设备1820被耦合在第二电压轨660与接地之间。钳位设备1820可以包括钳位晶体管和rc瞬态检测器,其中rc瞬态检测器被配置为检测esd事件,并且当esd事件检测到提供到接地的放电路径时接通钳位晶体管。

在该示例中,在esd事件期间,二极管1810和钳位设备1820提供从输出引脚1890到接地的放电路径,以释放输出引脚1890上的静电荷。

[0140]

然而,输出引脚1890上的电压仍可能达到大电压,这可能导致被耦合至输出引脚1890的晶体管产生大的栅极到漏极电压,从而可能损坏晶体管。为了防止这种情况,混合驱动器610、805、905或1005中的一个或多个上拉pfet 635和混合ldo调节器1310中的传输pfet 1330在esd事件期间接通,从而产生通过混合驱动器和混合ldd调节器的放电路径1805。这假设当电源关断时pfet的栅极向接地漂移,使得pfet在esd事件期间接通。对应的放电电流通过电阻器1848,导致跨电阻器1848的ir压降。跨电阻器1848的ir压降降低了混合驱动器和混合ldo调节器中的晶体管在esd事件期间暴露的电压,这降低了混合驱动和混合ldd调节器中的晶体管的栅极到漏极电压,从而提供更大的esd鲁棒性。注意,为了便于图示,仅放电路径1805中的混合驱动器和混合ldo调节器的晶体管在图18中示出。

[0141]

如上面讨论的,混合ldo调节器1310的第一调节模式可以与混合驱动器610、805、905或1005的n-over-n驱动器模式一致,并且混合ldo调节器1310的第二调节模式可以与混合驱动器610、805、905或1005的p-over-n驱动器模式一致。这允许混合ldo调节器1310的调节模式和混合驱动器的驱动器模式由相同的开关控制电路控制。该情况的示例在图19a和19b中图示,其中根据某些方面,图19a示出了混合驱动器905的示例性实施方式,并且图19b示出了混合ldo调节器1310的示例性实施方式。在该示例中,开关控制电路680基于电压控制信号(例如来自电压控制电路695)在输出1910处生成控制信号enp,并且在输出1920处生成控制信号enn。控制信号enp和enn被用于控制混合驱动器905的驱动器模式和混合ldo调节器1310的调节模式。因此,在该示例中,混合驱动器905的驱动器模式和混合ldo调节器1310的调节模式由同一控制信号集合enp和enn控制。

[0142]

在图19a中的示例中,开关640a用nfet实施,开关640b用nfet实施,开关642a用pfet实施,并且开关642b用pfet实施。这些晶体管中的每个晶体管的栅极被耦合至开关控制电路680的输出1910以接收控制信号enp。开关644a和644b中的每个开关用相应的传输门来实施,该传输门包括并行耦合的pfet和nfet,其中pfet的栅极被耦合至开关控制电路680的输出1920以接收控制信号enn,并且nfet的栅极被耦合至开关控制电路680的输出1910以接收控制信号enp。开关646a和646b中的每个开关用相应的传输门来实施,该传输门包括并行耦合的pfet和nfet,其中pfet的栅极被耦合至开关控制电路680的输出1910以接收控制信号enp,并且nfet的栅极被耦合至开关控制电路680的输出1920以接收控制信号enn。

[0143]

在图19b中的示例中,开关1332用nfet实施,并且开关1334用pfet实施,其中nfet和pfet中的每一个的栅极被耦合至开关控制电路680的输出1910,以接收控制信号enp(如图19a所示)。开关1322和1328中的每个开关用相应的传输门来实施,该传输门包括并行耦合的pfet和nfet,其中pfet的栅极被耦合至开关控制电路680的输出1910以接收控制信号enp,并且nfet的栅极被耦合至开关控制电路680的输出1920以接收控制信号enn。开关1324和1338中的每个开关用相应的传输门来实施,该传输门包括并行耦合的pfet和nfet,其中pfet的栅极被耦合至开关控制电路680的输出1920以接收控制信号enn,并且nfet的栅极被耦合至开关控制电路680的输出1910以接收控制信号enp。注意,为了便于图示,补偿电路1410和1420未在图19b中示出。

[0144]

在该示例中,通过将控制信号enp设置为0并且将控制信号enn设置为1,开关控制

电路680在n-over-n驱动器模式下操作混合驱动器905,并且在第一调节模式下操作混合ldo调节器1310。例如,如果电压控制信号的电流值在第一组值(例如0至23)中,则开关控制电路680可以这样做。通过将控制信号enp设置为1并且将控制信号enn设置为0,开关控制电路680在p-over-n驱动器模式下操作混合驱动器905,并且在第二调节模式下操作混合ldo调节器1310。例如,如果电压控制信号的电流值在第二组值(例如24至31)中,则开关控制电路680可以这样做。

[0145]

要了解的是,混合驱动器905中的开关和混合ldo调节器1310中的开关不被限于图19a和19b所示的示例性实施方式。

[0146]

图20图示了根据本公开的某些方面的用于操作混合电压调节器的方法2000。混合电压调节器(例如混合ldo调节器1310)包括被耦合在第一电压轨(例如第一电压轨655)与第二电压轨(例如第二电压轨660)之间的传输n型场效应晶体管(nfet)(例如传输nfet1320)以及被耦合在第一电压轨与第二电压轨之间的传输p型场效应晶体管(pfet)(例如传输pfet 1330)。

[0147]

在框2010中,在第一调节模式下,传输pfet被关断。例如,传输pfet可以通过接通被耦合在传输pfet的栅极与第二电压轨之间的开关(例如开关1334)来关断。开关可以由开关控制电路1380接通。

[0148]

在框2020中,在第一调节模式下,传输nfet的栅极基于参考电压和反馈电压来驱动,其中反馈电压提供第一电压轨上的电压的反馈。例如,传输nfet的栅极可以由第一放大器1340驱动。在该示例中,反馈电压可以与第一电压轨上的电压(例如vreg)成比例,并且第一放大器1340可以在减小参考电压与反馈电压之间的差异的方向上驱动传输nfet的栅极。

[0149]

在框2030中,在第二调节模式下,传输nfet被关断。例如,传输nfet可以通过接通被耦合在传输nfet的栅极与接地之间的开关(例如开关1332)来关断。开关可以由开关控制电路1380接通。

[0150]

在框2040中,在第二调节模式下,传输pfet的栅极基于参考电压和反馈电压来驱动。例如,传输pfet的栅极可以由第二放大器1350驱动。在该示例中,反馈电压可以与第一电压轨上的电压(例如vreg)成比例,并且第二放大器1350可以在减小参考电压与反馈电压之间的差异的方向上驱动传输pfet的栅极。

[0151]

要了解的是,本公开不被限于上面用于描述本公开的各个方面的示例性术语。例如,驱动器也可以被称为发送器、驱动器电路或另一术语。在另一示例中,链路也可以被称为信道、传输线或另一术语。切片也可以被称为切片单元或另一术语。在另一示例中,nfet也可以被称为n型金属氧化物半导体(nmos)晶体管,并且pfet也可以被称为p型金属氧化物半导体(pmos)晶体管。在另一示例中,传输晶体管也可以被称为传输元件、传输设备或另一术语。输出引脚也可以被称为输出焊盘或另一术语,并且输入引脚也可以被称为输入焊盘或另一术语。

[0152]

本文使用诸如“第一”、“第二”等名称对元件的任何引用通常不会限制这些元件的数量或顺序。相反,这些名称在本文中被用作区分两个或多个元件或者元件实例的便利方式。因此,要了解的是,权利要求中的名称“第一”、“第二”等不一定对应于书面描述中的相同名称。进一步地,要了解的是,对第一元件和第二元件的引用并不意味着仅两个元件可以被使用,或者第一元件必须在第二元件之前。

[0153]

术语“耦合”在本文中被用于指代两个结构之间的直接或间接电耦合。例如,在间接电耦合的一个示例中,一个结构可以经由电阻器被耦合至另一结构。

[0154]

在本公开内,词语“示例性”被用于表示“充当示例、实例或图示”。本文作为“示例性”描述的任何实施方式或方面不必被解释为比本公开的其他方面更优选或有利。同样地,术语“各个方面”并不要求本公开的所有方面都包括所讨论的特征、优点或操作模式。本文相对于规定值或财产使用的术语“近似”旨在指示在规定值或财产的10%内。

[0155]

本公开的先前描述被提供,以使本领域的任何技术人员能够制造或使用本公开。本公开的各种修改对于本领域技术人员来说将是显而易见的,并且在不脱离本公开的精神或范围的情况下,本文定义的一般原理可以被应用于其他变化。因此,本公开不旨在被限于本文描述的示例,而是被赋予与本文公开的原理和新颖特征一致的最广泛的范围。

[0156]

实施方式1.一种芯片,包括:

[0157]

电压调节器,其中电压调节器包括:

[0158]

传输n型场效应晶体管(nfet),被耦合在第一电压轨与第二电压轨之间;

[0159]

传输p型场效应晶体管(pfet),被耦合在第一电压轨与第二电压轨之间;

[0160]

第一放大器,具有输出;

[0161]

第一开关,被耦合在第一放大器的输出与传输nfet的栅极之间;

[0162]

第二放大器,具有输出;

[0163]

第二开关,被耦合在第二放大器的输出与传输pfet的栅极之间;

[0164]

第三开关,被耦合在传输nfet的栅极与接地之间;以及

[0165]

第四开关,被耦合在传输pfet的栅极与第二电压轨之间。

[0166]

实施方式2.根据实施方式1的芯片,还包括控制电路,控制电路被配置为:

[0167]

接收控制信号;

[0168]

如果控制信号具有第一组值中的一个值,则接通第一开关,关断第二开关,关断第三开关并且接通第四开关;以及

[0169]

如果控制信号具有第二组值中的一个值,则关断第一开关,接通第二开关,接通第三开关并且关断第四开关。

[0170]

实施方式3.根据实施方式1或2的芯片,还包括:

[0171]

驱动器,其中驱动器包括:

[0172]

下拉晶体管,被耦合在驱动器的输出与接地之间;

[0173]

上拉nfet,被耦合在第一电压轨与驱动器的输出之间;

[0174]

上拉pfet,被耦合在第一电压轨与驱动器的输出之间;

[0175]

第五开关,被耦合在上拉nfet的栅极与接地之间;以及

[0176]

第六开关,被耦合在上拉pfet的栅极与第二电压轨之间。

[0177]

实施方式4.根据实施方式3的芯片,还包括:

[0178]

串行器,具有输入和输出,其中串行器的输出被耦合至驱动器;以及

[0179]

电路,具有被耦合至串行器的输入的输出。

[0180]

实施方式5.根据实施方式4的芯片,其中电路包括处理器。

[0181]

实施方式6.根据实施方式3至5中任一项的芯片,还包括控制电路,控制电路被配置为:

[0182]

接收控制信号;

[0183]

如果控制信号具有第一组值中的一个值,则接通第一开关,关断第二开关,关断第三开关,接通第四开关,关断第五开关并且接通第六开关;以及

[0184]

如果控制信号具有第二组值中的一个值,则关断第一开关,接通第二开关,接通第三开关,关断第四开关,接通第五开关并且关断第六开关。

[0185]

实施方式7.根据实施方式1或2的芯片,还包括:

[0186]

第五开关,被耦合在第一放大器的第一输入与第一电压轨之间;以及

[0187]

第六开关,被耦合在第二放大器的第一输入与第一电压轨之间。

[0188]

实施方式8.根据实施方式7的芯片,还包括参考电路,具有被耦合至第一放大器的第二输入和第二放大器的第二输入的参考输出,其中参考电路被配置为生成参考电压并且在参考输出处输出参考电压。

[0189]

实施方式9.根据实施方式8的芯片,其中参考电路包括:

[0190]

电流源,被耦合在第二电压轨与参考输出之间;以及

[0191]

可变电阻器,被耦合在参考输出与接地之间,其中可变电阻器被配置为接收控制信号并且基于控制信号来设置可变电阻器的电阻。

[0192]

实施方式10.根据实施方式8的芯片,其中参考电路包括:

[0193]

参考电阻器,被耦合在第二电压轨与参考输出之间;以及

[0194]

可变电阻器,被耦合在参考输出与接地之间,其中可变电阻器被配置为接收控制信号并且基于控制信号来设置可变电阻器的电阻。

[0195]

实施方式11.根据实施方式8的芯片,其中参考电路被配置为:

[0196]

接收控制信号;以及

[0197]

基于控制信号来设置参考电压的电压电平。

[0198]

实施方式12.根据实施方式9至11中任一项的芯片,还包括控制电路,控制电路被配置为:

[0199]

接收控制信号;

[0200]

如果控制信号具有第一组值中的一个值,则接通第一开关,关断第二开关,关断第三开关,接通第四开关,接通第五开关并且关断第六开关;以及

[0201]

如果控制信号具有第二组值中的一个值,则关断第一开关,接通第二开关,接通第三开关,关断第四开关,关断第五开关并且接通第六开关。

[0202]

实施方式13.根据实施方式7至12中任一项的芯片,还包括电压驱动器,包括:

[0203]

第一电阻器;以及

[0204]

第二电阻器,其中第一电阻器被串行耦合在第一电压轨与接地之间,第五开关被耦合在反馈节点与第一放大器的第一输入之间,第六开关被耦合在反馈节点与第二放大器的第一输入之间,并且反馈节点在第一电阻器与第二电阻器之间。

[0205]

实施方式14.根据实施方式1或2的芯片,还包括:

[0206]

第一补偿电路,被耦合至传输nfet的栅极;

[0207]

第二补偿电路,被耦合至传输pfet的栅极;以及

[0208]

第五开关,被耦合在第二补偿电路与pfet的漏极之间。

[0209]

实施方式15.根据实施方式14的芯片,其中第一补偿电路包括第一补偿电容器,并

且第二补偿电路包括第二补偿电容器。

[0210]

实施方式16.根据实施方式14或15的芯片,还包括控制电路,控制电路被配置为:

[0211]

接收控制信号;

[0212]

如果控制信号具有第一组值中的一个值,则接通第一开关,关断第二开关,关断第三开关,接通第四开关并且关断第五开关;以及

[0213]

如果控制信号具有第二组值中的一个值,则关断第一开关,接通第二开关,接通第三开关,关断第四开关并且接通第五开关。

[0214]

实施方式17.根据实施方式3至5中任一项的芯片,还包括:

[0215]

第七开关,被耦合在第一放大器的第一输入与第一电压轨之间;以及

[0216]

第八开关,被耦合在第二放大器的第一输入与第一电压轨之间。

[0217]

实施方式18.根据实施方式17的芯片,还包括控制电路,控制电路被配置为:

[0218]

接收控制信号;

[0219]

如果控制信号具有第一组值中的一个值,则接通第一开关,关断第二开关,关断第三开关,接通第四开关,关断第五开关,接通第六开关,接通第七开关并且关断第八开关;以及

[0220]

如果控制信号具有第二组值中的一个值,则关断第一开关,接通第二开关,接通第三开关,关断第四开关,接通第五开关,关断第六开关,关断第七开关并且接通第八开关。

[0221]

实施方式19.根据实施方式17或18的芯片,还包括参考电路,参考电路具有参考输出,参考输出被耦合至第一放大器的第二输入和第二放大器的第二输入,其中参考电路被配置为生成参考电压并且在参考输出处输出参考电压。

[0222]

实施方式20.根据实施方式17至19中任一项的芯片,还包括电压驱动器,包括:

[0223]

第一电阻器;以及

[0224]

第二电阻器,其中第一电阻器被串行耦合在第一电压轨与接地之间,第七开关被耦合在反馈节点与第一放大器的第一输入之间,第八开关被耦合在反馈节点与第二放大器的第一输入之间,并且反馈节点在第一电阻器与第二电阻器之间。

[0225]

实施方式21.一种操作混合电压调节器的方法,其中电压调节器包括传输n型场效应晶体管(nfet)和传输p型场效应晶体管(pfet),传输nfet被耦合在第一电压轨与第二电压轨之间,传输pfet被耦合在第一电压轨与第二电压轨之间,该方法包括:

[0226]

在第一调节模式下,关断传输pfet;

[0227]

在第一调节模式下,基于参考电压和反馈电压来驱动传输nfet的栅极,其中反馈电压提供第一电压轨上的电压的反馈;

[0228]

在第二调节模式下,关断传输nfet;以及

[0229]

在第二调节模式下,基于参考电压和反馈电压来驱动传输pfet的栅极。

[0230]

实施方式22.根据实施方式21的方法,其中反馈电压与第一电压轨上的电压成比例。

[0231]

实施方式23.根据实施方式21或22的方法,其中:

[0232]

基于参考电压和反馈电压来驱动传输nfet的栅极包括:在减小参考电压与反馈电压之间的差异的方向上驱动传输nfet;以及

[0233]

基于参考电压和反馈电压来驱动传输pfet的栅极包括:在减小参考电压与反馈电

压之间的差异的方向上驱动传输pfet。

[0234]

实施方式24.根据实施方式21至23中任一项的方法,还包括:

[0235]

接收控制信号;以及

[0236]

基于控制信号来设置参考电压的电压电平。

[0237]

实施方式25.根据实施方式24的方法,还包括:

[0238]

如果控制信号具有第一组值中的一个值,则在第一调节模式下操作电压调节器;以及

[0239]

如果控制信号具有第二组值中的一个值,则在第二调节模式下操作电压调节器。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1