一种基准电压及倍压电路的制作方法

1.本技术涉及微电子技术领域,尤其是涉及一种基准电压及倍压电路。

背景技术:

2.带隙基准电路是模拟以及数模混合电路系统的基本模块,用以给模拟及数模混合电路提供一个稳定的基准电压。

3.目前,在基准电路中,通常包括带隙基准电路和基准倍压电路,带隙基准电压为1.2v,而基准倍压电路用于产生基准电压1.2v增倍的参考电压,通常参考电压是1.2v、2.4v、3.6v等。

4.针对上述中的相关技术,发明人发现:基准倍压电路通常通过设定电阻的比例关系得到相应的参考电压,而电阻存在消耗,在低功耗电路领域中,为了减小电阻的消耗,通常做法为增大电阻的面积,这样会增加集成芯片的面积。

技术实现要素:

5.为了降低功耗且减小芯片的面积,本技术提供一种基准电压及倍压电路。

6.本技术提供的一种基准电压及倍压电路,采用如下的技术方案:一种基准电压及倍压电路,包括带隙基准电路和基准倍压电路,所述基准倍压电路包括mos管n1、电流镜像单元和倍压单元,所述mos管n1采用n型mos管,mos管n1的栅极与带隙基准电路的输出端连接,mos管n1的漏极与电流镜像单元连接,mos管n1的源极接地,所述电流镜像单元与电源vdd连接,所述倍压单元的一端与电流镜像单元连接,倍压单元的另一端接地;其中,倍压单元包括多个依次串联的mos管,且每个mos管的栅极与自身的漏极连接,若倍压单元采用n型mos管,则mos管的栅极作为参考电压输出端;若倍压单元采用p型mos管,则mos管的漏极作为参考电压输出端。

7.通过采用上述技术方案,带隙基准电路产生带隙基准电压,并将带隙基准电压输送到mos管n1的栅极,mos管n1将带隙基准电压转换为电流,并通过电流镜像单元将该电流传递到倍压单元,倍压单元中的mos管将电流转换成带隙基准电压,并且通过串联mos管的个数来倍增带隙基准电压,以得到不同的参考电压;而mos管的消耗较小,适合低功耗电路,且能减小芯片的面积。

8.优选的,所述mos管n1采用宽长比小于或等于0.1的mos管,倍压单元中的mos管的尺寸与mos管n1的尺寸相同。

9.通过采用上述技术方案,mos管的宽长比小于或等于0.1,可以使mos管的栅极电压为1.2v时产生较小的电流,进一步降低功耗,且沟道调制效应小,有较高的厄利电压。

10.优选的,所述mos管n1的宽为2um,mos管n1的长为20um。

11.通过采用上述技术方案,mos管的占用面积较小,可进一步减小芯片的面积。

12.优选的,所述电流镜像单元包括mos管p1和mos管p2,所述mos管p1和mos管p2采用p

型mos管,mos管p1的源极与电源vdd连接,mos管p1的栅极与mos管p1的漏极、mos管n1的漏极连接;所述mos管p2的源极与电源vdd连接,mos管p2的栅极与mos管p1的栅极连接,mos管p2的漏极与倍压单元连接。

13.通过采用上述技术方案,mos管p1和mos管p2组成1:1比例的电流镜像单元,流过mos管p1和mos管p2的电流相同,电路简单,成本低。

14.优选的,所述电流镜像单元还包括mos管p3,所述mos管p3采用p型mos管,mos管p3的源极与电源vdd连接,mos管p3的栅极与mos管p1的栅极连接,mos管p3的漏极连接有参考电压单元。

15.优选的,所述参考电压单元包括mos管n5,所述mos管n5采用n型mos管,mos管n5的漏极与mos管p3的漏极、mos管n5的栅极连接,mos管n5的源极接地。

16.通过采用上述技术方案,mos管n5的栅极产生1倍带隙基准电压的参考电压,可增加一路参考电压,便于电路设计。

17.优选的,所述带隙基准电路的输出端连接有滤波单元,所述滤波单元的输出端与mos管n1的栅极连接。

18.优选的,所述滤波单元包括电阻r4和电容c,所述电阻r4的一端与带隙基准电路的输出端连接,电阻r4的另一端与mos管n1的栅极、电容c的一端连接,所述电容c的另一端接地。

19.通过采用上述技术方案,电阻r4和电容c形成rc滤波网络,提高带隙基准电压的稳定性。

20.综上所述,本技术包括以下至少一种有益技术效果:1.通过串联mos管的个数来倍增带隙基准电压,以得到不同的参考电压,而mos管的消耗较小,适合低功耗电路,且能减小芯片的面积;2.mos管的宽长比小于或等于0.1,可以使mos管的栅极电压为1.2v时产生较小的电流,进一步降低功耗,且沟道调制效应小,有较高的厄利电压;3.通过电阻r4和电容c形成rc滤波网络,可提高带隙基准电压的稳定性。

附图说明

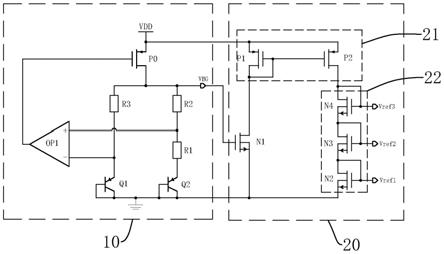

21.图1是相关技术中一种适用于低电压输入的带隙基准电路的电路图;图2是相关技术中一种基准电压及倍压电路的电路图;图3是相关技术中另一种基准电压及倍压电路的电路图;图4是相关技术中另一种基准电压及倍压电路的电路图;图5是相关技术中另一种基准电压及倍压电路的电路图;图6是本技术实施例1中一种基准电压及倍压电路的电路图;图7是本技术实施例2中一种基准电压及倍压电路的电路图;图8是本技术实施例3中一种基准电压及倍压电路的电路图;图9是本技术实施例4中一种基准电压及倍压电路的电路图。

22.附图标记说明:10、带隙基准电路;20、基准倍压电路;21、电流镜像单元;22、倍压单元;30、滤波单元;40、参考电压单元。

具体实施方式

23.以下结合附图1-9对本技术作进一步详细说明。

24.参考图1,相关技术公开一种适用于低电压输入的带隙基准电路,包括运算放大器op1、mos管p0、电阻r1、电阻r2、电阻r3、三极管q1和三极管q2,其中,mos管p0为p型mos管,三极管q1和三极管q2为pnp型三极管。运算放大器op1反相端与三极管q1发射极之间的连接点的电压为vnode1,运算放大器op1同相端与电阻r1之间的连接点的电压为vnode2,vnode1与vnode2相等,而电阻r2和电阻r3的阻值相同,电阻r2和电阻r3上产生的电压相等,由此,构成了wildar电流源。

25.其中,三极管q1和三极管q2发射区的面积比例关系设置为1:8,产生数值为ln8*vt/r1的ptat电流,则在三极管q1与电阻r3串联网络,以及在三极管q2、电阻r1与电阻r2串联网络上产生的带隙基准电压为:vbg=(r1+r2)*(ln8*vt/r1)+vbe式中,vbg为带隙基准电压,vt为热电压,vbe为三极管基极与发射极之间的电压。

26.参考图2,相关技术公开一种基准电压及倍压电路,包括隙基准电路和基准倍压电路20,其中,带隙基准电路10用于产生带隙基准电压vbg,在mos管p0中产生ptat电流,并通过构建1:1比例关系的mos管 p1和mos管p2传递ptat电流,mos管 p1和mos管p2为p型mos管,而三极管q3和电阻r4串联,ptat电流通过电阻r4,在电阻r4与mos管p1之间的连接点处产生1倍带隙基准电压的参考电压。其中,三极管q3、三极管q4和三极管q5为pnp型三极管,和电阻r5串联,三极管q5和电阻r6串联,在电阻r5与三极管q4集电极的连接点处产生1倍带隙基准电压的参考电压,在电阻r6与mos管p2源极的连接点处产生2倍带隙基准电压的参考电压。其中,三极管q3、三极管q4和三极管q5为双极型三极管,双极型三极管一种隔离型器件,实现隔离型的三极管需要bcd工艺,无法运用于数字电路中,而电阻r4、电阻r5和电阻r6的设置,会导致功耗增大,芯片面积的增大。

27.参考图3,相关技术公开一种基准电压及倍压电路,与图2的不同之处在于:三极管q3、三极管q4和三极管q5采用npn型三极管,其中,在三极管q4的基极处产生1倍带隙基准电压的参考电压,在三极管q5的基极处产生2倍带隙基准电压的参考电压。其中,三极管q3、三极管q4和三极管q5为双极型三极管,实现隔离型的三极管需要bcd工艺,无法运用于数字电路中,而电阻r4、电阻r5和电阻r6的设置,会导致功耗增大,芯片面积的增大。

28.参考图4,相关技术公开一种基准电压及倍压电路,带隙基准电路10产生带隙基准电压vbg,电阻r4和电容c构成rc滤波网络,将带隙基准电压信号vbg滤波成vbg_rc电压信号,该电压信号输入到运算放大器op2的同相端,运算放大器op2的输出接mos管n1的栅极,mos管n1为n型mos管,mos管n1的源极接电阻r7,mos管n1的漏极连接电源vdd,电阻r7、电阻r6和电阻r5依次串联,电阻r7、电阻r6和电阻r5的阻值相同,电阻r5和电阻r6之间的连接点与运算放大器op2的反相端连接,其中,在电阻r5与电阻r6之间的连接点处产生1倍带隙基准电压的参考电压,在电阻r6和电阻r7之间的连接点处产生2倍带隙基准电压的参考电压,在电阻r7和mos管n1之间的连接点处产生3倍带隙基准电压的参考电压。其中,mos管n1和运算放大器op2构成的反馈系统,电源vdd需要大于一个mos管n1的驱动电压和3倍的基准电压之和,而电阻r5、电阻r6、电阻r7的设置,会导致功耗增大,芯片面积的增大。

29.参考图5,相关技术公开一种基准电压及倍压电路,与图4的不同之处在于:mos管

p1为p型mos管,其中,在电阻r5与电阻r6之间的连接点处产生1倍带隙基准电压的参考电压,电阻r6和电阻r7之间的连接点处产生2倍带隙基准电压的参考电压,电阻r7和mos管p1之间的连接点处产生3倍带隙基准电压的参考电压。其中,mos管p1和运算放大器op2构成的反馈系统,电源vdd需要大于3倍的基准电压,而电阻r5、电阻r6、电阻r7的设置,会导致功耗增大,芯片面积的增大。

30.本技术提供一种基准电压及倍压电路。

31.实施例1参考图6,基准电压及倍压电路包括带隙基准电路10和基准倍压电路20,带隙基准电路10用于产生带隙基准电压vbg。

32.基准倍压电路20包括mos管n1、电流镜像单元21和倍压单元22,mos管n1采用n型mos管,mos管n1的栅极与带隙基准电路10的输出端连接,mos管n1的漏极与电流镜像单元21连接,mos管n1的源极接地,电流镜像单元21与电源vdd连接,倍压单元22的一端与电流镜像单元21连接,倍压单元22的另一端接地。

33.其中,mos管n1采用隔离型mos管,可以更好地隔离衬底噪声信号对基准电压的干扰。带隙基准电压vbg输出到mos管n1的栅极,在mos管n1上产生的电流ids为:ids=(kpn/2)*(w/l)*(vgs-vthn)^2式中:vthn为开启阈值,可以取0.7v;w/l为mos管的宽长比;kpn为常数,可以取60ua/v^2;vgs为mos管栅极与源极之间的电压。

34.其中,倍压单元22包括多个依次串联的mos管,且每个mos管的栅极与自身的漏极连接。在本实施例中,倍压单元22采用n型mos管,例如,倍压单元22包括mos管n2、mos管n3和mos管n4,其中,mos管n4的漏极与电流镜像单元21连接,mos管n4的栅极与mos管n4的漏极连接,mos管n4的源极与mos管n3的漏极连接,mos管n3的栅极与mos管n3的漏极连接,mos管n3的源极与mos管n2的漏极连接,mos管n2的栅极与mos管n2的漏极连接,mos管n2的源极接地。

35.mos管n1、mos管n2、mos管n3和mos管n4采用宽长比小于或等于0.1的mos管;例如,mos管n1、mos管n2、mos管n3和mos管n4的宽均为2um,mos管n1、mos管n2、mos管n3和mos管n4的长均为20um;mos管n1、mos管n2、mos管n3和mos管n4均采用隔离型的增强型场效应晶体管。

36.电流ids流到mos管n4,在mos管n4上产生的电压vgs为:vgs=(2*ids/(kpn*(w/l)))^0.5+vthn在电流镜像单元21的作用下,流过mos管n2、mos管n3和mos管n4的电流与电流ids相同,mos管n2、mos管n3和mos管n4串联后,相邻mos管之间的栅极与源极连接在一起,使得mos管不存在衬偏效应。电流ids由带隙基准电压来决定,则在mos管n2、mos管n3和mos管n4上产生的电压vgs均等于带隙基准电压,故,mos管n2的栅极电压为1倍的带隙基准电压,mos管n3的栅极电压为2倍的带隙基准电压,mos管n4的栅极电压为3倍的带隙基准电压。

37.电流镜像单元21包括mos管p1和mos管p2,mos管p1和mos管p2采用p型mos管,mos管p1的源极与电源vdd连接,mos管p1的栅极与mos管p1的漏极、mos管n1的漏极连接。mos管p2的源极与电源vdd连接,mos管p2的栅极与mos管p1的栅极连接,mos管p2的漏极与mos管n4的漏极连接。

38.实施例1的实施原理为:带隙基准电路10产生带隙基准电压,并将带隙基准电压输

送到mos管n1的栅极,mos管n1将带隙基准电压转换为电流,并通过电流镜像单元21将该电流传递到倍压单元22,倍压单元22中的mos管将电流转换成带隙基准电压,并且通过串联mos管的个数来倍增带隙基准电压,以得到不同的参考电压。其中,若要产生n倍的带隙基准电压,则串联n个隔离型的mos管即可,此时,电源vdd的电压需要大于n倍的带隙基准电压。

39.通过利用mos管替换由双极晶体管和电阻构成的电压网络,或者由运算放大器和电阻网络构成的电压网络,可以简化电路,同时调整mos管的w/l比例,可以更好地适应低功耗电路,并减小芯片的面积。

40.实施例2参照图7,本实施例与实施例1的不同之处在于,带隙基准电路10的输出端还连接有滤波单元30,在本实施例中,滤波单元30包括电阻r4和电容c,电阻r4的一端与带隙基准电路10的输出端连接,电阻r4的另一端与mos管n1的栅极、电容c的一端连接,电容c的另一端接地。

41.电阻r4和电容c1构成rc滤波网络,将带隙基准电压信号vbg滤波成vbg_rc电压信号,可以提高基准电压的稳定性。

42.实施例3参照图8,本实施例与实施例2的不同之处在于,电流镜像单元21还包括mos管p3,mos管p3采用p型mos管,mos管p3的源极与电源vdd连接,mos管p3的栅极与mos管p1的栅极连接,mos管p3的漏极连接有参考电压单元40。

43.参考电压单元40包括mos管n5,mos管n5采用n型mos管,mos管n5的漏极与mos管p3的漏极、mos管n5的栅极连接,mos管n5的源极接地。其中,mos管n5的宽为2um,mos管n5的长为20um。mos管n5上产生的电压vgs等于带隙基准电压,故,mos管n5的栅极电压为1倍的带隙基准电压。

44.实施例4参照图9,本实施例与实施例1的不同之处在于,倍压单元22采用p型mos管,例如,倍压单元22包括mos管p3、mos管p4和mos管p5,其中,mos管p3的源极与电流镜像单元21连接,mos管p3的栅极与mos管p3的漏极连接,mos管p3的漏极与mos管p4的源极连接,mos管p4的栅极与mos管p4的漏极连接,mos管p4的漏极与mos管p5的源极连接,mos管p5的栅极与mos管p5的漏极连接,mos管p5的漏极接地。

45.其中,mos管p3的源极电压为3倍的带隙基准电压,mos管p4的源极电压为2倍的带隙基准电压,而mos管p5的源极电压为1倍的带隙基准电压。

46.以上均为本技术的较佳实施例,并非依此限制本技术的保护范围,故:凡依本技术的结构、形状、原理所做的等效变化,均应涵盖于本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1