一种集成电路安全检测系统

1.本技术涉及集成电路领域,特别涉及一种集成电路安全检测系统。

背景技术:

2.随着半导体制造工艺和计算机辅助设计技术的快速发展,集成电路广泛地应用在各个领域,成为国民生活中不可或缺的部分,因此集成电路的安全性十分重要,目前市面上很少有专门针对集成电路安全检测的硬件平台,一般都是通用性的fpga(field programmable gate array,现场可编程逻辑门阵列)开发板,无法精确的测量集成电路中是否植入硬件木马。

3.因此如何提高集成电路安全检测的可靠性是本领域需要解决的技术问题。

技术实现要素:

4.有鉴于此,本技术的目的在于提供一种集成电路安全检测系统,可以提高集成电路安全检测的可靠性。

5.为实现上述目的,本技术有如下技术方案:

6.本技术实施例提供了一种集成电路安全检测系统,包括:高精密电阻模块、信号放大模块和处理器;所述高精密电阻模块包括高精密电阻;

7.所述处理器与待测集成电路连接,用于运行集成电路安全检测策略;

8.所述高精密电阻模块连接所述待测集成电路;所述高精密电阻模块还连接所述信号放大模块和所述处理器;

9.所述信号放大模块,用于放大所述高精密电阻的电压;所述信号放大模块连接示波器。

10.在一种可能的实现方式中,所述高精密电阻模块包括跳线;所述跳线连接第一路径和第二路径;

11.所述第一路径直接与电源总开关连接;

12.所述第二路径串联所述高精密电阻后与所述电源总开关连接。

13.在一种可能的实现方式中,所述系统还包括:外围接口电路模块和电源管理模块;

14.所述外围接口电路模块包括:双倍速率同步动态随机存取存储器、nand闪存和六线串行外设接口闪存,用于分别与所述处理器连接;

15.所述电源管理模块分别与所述处理器和所述外围接口电路模块连接,用于分别为所述处理器和所述外围接口电路模块供电。

16.在一种可能的实现方式中,所述系统还包括:数据通信接口模块;

17.所述数据通信接口模块包括:通用串行总线联合测试工作组接口、通用串行总线通用异步收发传输器调试接口和以太网接口,用于分别与所述处理器连接。

18.在一种可能的实现方式中,所述系统还包括:反式闪存卡接口,用于与所述处理器连接存储用户数据。

19.在一种可能的实现方式中,所述系统还包括:有机发光二极管显示模组,用于与所述处理器连接方便用户输入信号。

20.在一种可能的实现方式中,所述处理器包括:处理系统模块和可编程逻辑模块;

21.所述处理系统模块包括:双核中央处理器;所述可编程逻辑模块包括:现场可编程逻辑门阵列。

22.在一种可能的实现方式中,所述可编程逻辑模块分别与指示灯模块、开关模块和按键模块连接。

23.在一种可能的实现方式中,所述电源总开关为单刀双掷开关。

24.在一种可能的实现方式中,所述系统还包括:

25.分别与所述处理器连接的系统复位模块和模式配置模块;

26.所述系统复位模块,用于给所述处理器提供系统复位;

27.所述模式配置模块,用于配置所述系统的启动模式。

28.本技术实施例提供了一种集成电路安全检测系统,包括:高精密电阻模块、信号放大模块和处理器,高精密电阻模块包括高精密电阻,处理器与待测集成电路连接,用于运行集成电路安全检测策略,高精密电阻模块连接待测集成电路,高精密电阻模块还连接信号放大模块,信号放大模块,用于放大高精密电阻的电压,信号放大模块连接示波器。即提供专门针对集成电路安全检测的硬件平台,能更好适应目前集成电路安全检测的需要,减少不需要的模块,通过增加了高精密电阻模块和信号放大模块,精确测量和放大高精密电阻的电压值,从而可以根据高精密电阻的微小的电压值的变化准确的进行观测分析待测集成电路中是否存在木马电路,提高了集成电路安全检测的可靠性和效率。

附图说明

29.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

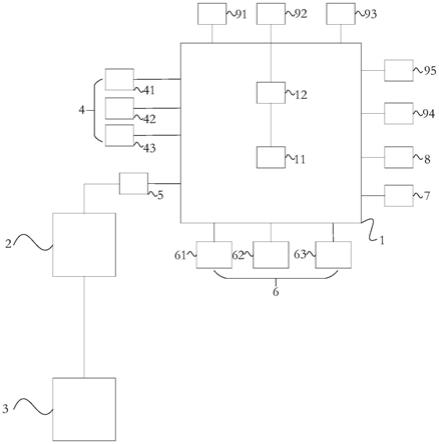

30.图1示出了本技术实施例提供的一种集成电路安全检测系统的示意图;

31.图2示出了本技术实施例提供的一种高精密电阻模块的示意图;

32.图3示出了本技术实施例提供的一种信号放大模块的示意图;

33.图4示出了本技术实施例提供的又一种集成电路安全检测系统的示意图;

34.图5示出了本技术实施例提供的电压转换的示意图。

具体实施方式

35.为使本技术的上述目的、特征和优点能够更加明显易懂,下面结合附图对本技术的具体实施方式做详细的说明。

36.在下面的描述中阐述了很多具体细节以便于充分理解本技术,但是本技术还可以采用其它不同于在此描述的其它方式来实施,本领域技术人员可以在不违背本技术内涵的情况下做类似推广,因此本技术不受下面公开的具体实施例的限制。

37.正如背景技术中的描述,随着半导体制造工艺和计算机辅助设计技术的快速发

展,集成电路广泛地应用在各个领域,成为国民生活中不可或缺的部分,因此集成电路的安全性十分重要,目前市面上很少有专门针对集成电路安全检测的硬件平台,一般都是通用性的fpga(field programmable gate array,现场可编程逻辑门阵列)开发板,无法精确的测量集成电路中是否植入硬件木马。

38.因此如何提高集成电路安全检测的可靠性是本领域需要解决的技术问题。

39.为了解决以上技术问题,本技术实施例提供了一种集成电路安全检测系统,包括:高精密电阻模块、信号放大模块和处理器,高精密电阻模块包括高精密电阻,处理器与待测集成电路连接,用于运行集成电路安全检测策略,高精密电阻模块连接待测集成电路,高精密电阻模块还连接信号放大模块,信号放大模块,用于放大高精密电阻的电压,信号放大模块连接示波器。即提供专门针对集成电路安全检测的硬件平台,能更好适应目前集成电路安全检测的需要,减少不需要的模块,通过增加了高精密电阻模块和信号放大模块,精确测量和放大高精密电阻的电压值,从而可以根据高精密电阻的微小的电压值的变化准确的进行观测分析待测集成电路中是否存在木马电路,提高了集成电路安全检测的可靠性和效率。

40.示例性系统

41.参见图1所示,为本技术实施例提供的一种集成电路安全检测系统,包括:高精密电阻模块2、信号放大模块3和处理器1。

42.高精密电阻模块2包括高精密电阻,处理器1与待测集成电路(图中未示出)连接,用于运行集成电路安全检测策略,高精密电阻模块2连接待测集成电路,高精密电阻模块2还连接信号放大模块3和处理器1,信号放大模块3,用于放大高精密电阻2的电压,信号放大模块3连接示波器。

43.在本技术实施例中,高精密电阻模块2包括高精密电阻,高精密电阻是要求电阻的阻值误差、电阻的热稳定性、电阻的分布参数等项指标均达到一定标准的电阻,普通电阻的阻值误差1%以上,高精密电阻的误差可以做到0.1%,甚至更低。

44.一般来说,如果待测集成电路中隐藏有异常电路,会在电路启动后有功率消耗现象,我们可以通过采集电路的电流电压数据,分析电路相关的电流、电压、功耗等,与对照的电路进行比较来判断其中是否存在有异常来确定是否有安全隐患。由于对照电路的相关参数变化很小,这种方法精度要求很高,这样就需要选择高精密电阻来采集电路的电流电压数据。

45.具体的,可以采用信号放大模块3,用于放大高精密电阻的电压,信号放大模块3连接示波器,即可以采用旁路信号检测方法检测待检测集成电路的安全性,即通过功耗(静态和动态)、信号延迟、电磁场等外在物理参数的变化分析是否存在木马电路。通过对输入管脚的接入电平控制进行静态和动态测试向量测试,并使用示波器测量在电源总输入端的高精密电阻两端的电压降,计算相应的静/动态电流值,从而计算出电路的总功耗。

46.在一种可能的实现方式中,参见图2所示,高精密电阻模块2包括跳线jp0,跳线jp0连接第一路径a和第二路径b,跳线的另一端可以接cn1dc_jack,即直流电源插座,直流电源插座cn1 dc_jack的第一端接电源和跳线jp0,直流电源插座cn1 dc_jack的第二端和第三端接地。

47.第一路径a直接与电源总开关s0连接,第二路径b串联高精密电阻r0后与电源总开

关s0连接。当需要进行旁路信号检测时,即需要检测高精密电阻r0两端的电压时则开启第二路径b,测高精密电阻r0两端的电压降来采集相关信息,即测量+vin到-vin的电压降;当不需要进行旁路信号检测时,即可以采用第一路径,电源直接通过电源总开关s0进入系统。

48.在一种可能的实现方式中,电源总开关s0可以为单刀双掷开关,参见图2所示,以上两种方式电源总开关s0均位于单刀双掷开关的1点;当不需要本技术实施例提供的集成电路安全检测系统进行测试时,可以将单刀双掷开关置于3点,此时系统处于断电状态。

49.在一种可能的实现方式中,参见图3所示,为本技术实施例提供的一种信号放大模块3的示意图,考虑到电压信号变化微弱,通过电压放大器(ad8000)对电压信号进行放大,ad8000是一款超高速、高性能、电流反馈型放大器,其输出的信号失真较低,带宽高达1.5ghz,输入失调电压:1mv,差分增益为0.02%。它具有两种供电模式,分别是单极性供电和双极性供电,由于单极性供电模式下,它的性能会降低,所以在本发明中,使用

±

5v双极性电源为它供电。双极性电源由wra1205md-6w供电,设置一个跳线jp1,在不需要测电压信号时可以设置断开,ad8000输出信号的增益由图中电阻r1和r2的阻值决定,通过调节r1和r2的阻值即可调节ad8000输出信号的增益,在本发明中,可以将增益设置为20。

50.高精密电阻r0两端的+vin和-vin分别连接ad8000的+in端和-in端,ad8000的fb端可以连接并联的第一电容c1和第一电阻r1,再与第二电阻r2串联,第二电阻r2连接-in端,第三电阻r3连接+in端,第二电容c2和第三电容c3并联接ad8000的-vs端后接地,其中,第三电容c3为有极性电容,ad8000的pd端和+vs端并联后与并联的第四电容c4和第五电容c5连接后接地,其中,第四电容c4为有极性电容,ad8000的output输出端接vout,ad8000的nc端为空端,双极性电源wra1205md-6w的1端接地,2端分别与第七电容c7和跳线jp1连接,跳线jp1连接电源,具体的,电源可以为12v,3端接+v0,具体的可以为5v,4端接地,5端接-v0即-5v,5端还可以接第六电容c6后接地,其中,第六电容c6为有极性电容,3端还可以接第八电容c8后接地,其中,第八电容c8为有极性电容。在vout和地之间还可以接有第四电阻r4。

51.需要说明的是,上述电阻和电容的大小可以根据信号放大模块的放大倍数进行设置,本技术实施例在此不作具体限定。

52.在一种可能的实现方式中,参见图4所示,本技术实施例提供的系统还包括:外围接口电路模块4和电源管理模块5,

53.外围接口电路模块4包括:双倍速率同步动态随机存取存储器41(ddr3sdram,double data rate synchronous dynamic random access memory)、nand闪存42(nand flash)和六线串行外设接口闪存43(qspi flash,quad serial peripheral interface flash),用于分别与处理器1连接。

54.电源管理模块5分别与处理器1和外围接口电路模块4连接,用于分别为处理器1和外围接口电路模块4供电。

55.其中,可选的,双倍速率同步动态随机存取存储器41可以为两片最大寻址空间为1gb的芯片,nand闪存42支持nand flash方式启动,用于存储uboot(通用引导加载程序,u-boot)、内核及文件系统,六线串行外设接口闪存芯片以六线串行外设接口闪存方式启动,存储用户程序。

56.可选的,电源管理模块5可以将处理器1与外围接口电路模块4分开供电,在不使用外围接口时,可以关断外围接口电路电源。

output,通用输入/输出)接口按键;8个用户开关方便用户输入信号,拨动开关可将相应的io管脚接电源,8个led指示灯,引脚的逻辑高电平将点亮对应led。

68.在一种可能的实现方式中,参见图4所示,系统还包括:

69.分别与处理器1连接的系统复位模块94和模式配置模块95,

70.系统复位模块94,用于给处理器1提供系统复位,模式配置模块95,用于配置系统的启动模式。

71.可选的,在本技术实施例中,上电复位采用复位芯片提供给处理器做系统复位;模式配置通过五个单排插针来设置系统的启动模式。

72.本技术实施例提供了一种集成电路安全检测系统,包括:高精密电阻模块、信号放大模块和处理器,高精密电阻模块包括高精密电阻,处理器与待测集成电路连接,用于运行集成电路安全检测策略,高精密电阻模块连接待测集成电路,高精密电阻模块还连接信号放大模块,信号放大模块,用于放大高精密电阻的电压,信号放大模块连接示波器。即提供专门针对集成电路安全检测的硬件平台,能更好适应目前集成电路安全检测的需要,减少不需要的模块,通过增加了高精密电阻模块和信号放大模块,精确测量和放大高精密电阻的电压值,从而可以根据高精密电阻的微小的电压值的变化准确的进行观测分析待测集成电路中是否存在木马电路,提高了集成电路安全检测的可靠性和效率,具有体积小、效率高,干扰小,测量数据准确等优点。

73.本说明书中的各个实施例均采用递进的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其它实施例的不同之处。尤其,对于器件实施例而言,由于其基本相似于方法实施例,所以描述得比较简单,相关之处参见方法实施例的部分说明即可。

74.以上所述仅是本技术的优选实施方式,虽然本技术已以较佳实施例披露如上,然而并非用以限定本技术。任何熟悉本领域的技术人员,在不脱离本技术技术方案范围情况下,都可利用上述揭示的方法和技术内容对本技术技术方案做出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本技术技术方案的内容,依据本技术的技术实质对以上实施例所做的任何的简单修改、等同变化及修饰,均仍属于本技术技术方案保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1