一种用于动态偏置电流LDO的低启动电流电路的制作方法

一种用于动态偏置电流ldo的低启动电流电路

技术领域

1.本发明涉及一种线性稳压器芯片,具体说是用于动态偏置电流ldo的低启动电流电路。

背景技术:

2.随之科技的发展,目前电源领域需要的线性电源芯片越来越多,低输出电压大电流的ldo广泛应用于各种mcu与主板中。众所周知,ldo有p型差分对运输放大器和n型差分对运输放大器两种,做低输出电压的ldo时,fb端电压很低,n型差分对因其g端需要的工作电压较高,通常要》1v,此情况下用n型差分对的ldo无法正常工作,而p型差分对运输放大器的ldo就不存在此问题,p型差分对运输放大器的ldo为了提高带载能力与动态特性通常采用动态偏置电流的方式,如图1所示。但其也带来了启动时静态电流过大这一缺点,其产生的原因为低输入电压时输出没有达到设定值,运输放大器输出端n3的g端拉的很高想控制功率p管给出更多的电流让输出达到设定值,此路径静态功耗很大,如图1中mos管p5和mos管n3的路径。

技术实现要素:

3.本发明要解决的技术问题是提高一种用于动态偏置电流ldo的低启动电流电路,采用电路的ldo的静态功耗小,启动时静态电流较小。解决了背景技术中静态功耗大,启动时静态电流过大的问题。

4.为解决上述问题,提供以下技术方案:

5.本发明的用于动态偏置电流ldo的低启动电流电路包括功率电路和控制电路。所述功率电路的输入端接入vin,输出端输出vout。所述控制电路包括运算放大器和mos管n3,运算放大器的同相输入端接入基准电压vref,运算放大器的反相输入端与控制电路适配连接,运算放大器的反相输入端用于接收控制电路的电压反馈vfb,运算放大器的输出端与mos管n3的栅极相连,mos管n3的漏极与功率电路适配连接。其特点是还包括比较器。所述mos管n3的源极与电阻r3的一端相连,电阻r3的另一端接地。所述功率电路的输出端与比较器的同相输入端相连,比较器的反向输入端接入vin,比较器的输出端与mos管n3的源极相连。

6.其中,所述功率电路的输出端与电阻r1的一端相连,电阻r1的另一端分别与运输放大器的输出端和电阻r2的一端相连,电阻r2的另一端接地。

7.所述功率电路含有电流镜一,电流镜一包括mos管p5和mos管p6。所述mos管p5的源极和mos管p6的源极均与vin相连,mos管p5的栅极分别与mos管p5的漏极和mos管p6的栅极相连,mos管p5的漏极与所述mos管n3的漏极相连,mos管p6的漏极即为功率电路的输出端。

8.所述运算放大器含有mos管p1、mos管p2和电流镜二,电流镜二包括mos管n1和mos管n2。所述mos管p1的栅极为运算放大器的同相输入端,mos管p2的栅极为运算放大器的反相输入端,mos管p1的源极与mos管p2的源极相连、形成运算放大器的电源流端。所述mos管

p1的漏极分别与mos管n1的漏极、mos管n1的栅极和mos管n2的栅极相连,mos管n1的源极和mos管n2的源极接地。所述mos管p2的漏极即为运算放大器的输出端,且与mos管p2的漏极与mos管n2的漏极相连。

9.所述比较器含有差分对、电阻r4、电阻r5、mos管n4、mos管n5和mos管n6;所述差分对含有mos管p7和mos管p8。所述mos管p7的源极为比较器的同相输入端,所述mos管p8的源极为比较器的反相输入端,所述mos管n6漏极为比较器的输出端。所述mos管p7栅极分别与mos管p7的漏极和mos管p8栅极相连,mos管p7的漏极与电阻r4的一端相连,电阻r4的另一端与mos管n4的漏极相连,mos管n4的源极接地,mos管n4的栅极分别与mos管n5的栅极和mos管n1的栅极相连。所述mos管p8的漏极与电阻r5的一端相连,电阻r5的另一端分别与mos管n6的栅极和mos管n5的漏极相连,mos管n5和与mos管n6的源极均接地。

10.所述运算放大器的电源流端适配连接有电流镜四,电流镜四含有mos管p3和mos管p4,mos管p3的源极和mos管p4的源极均接电源vdd,mos管p3的栅极分别与其漏极和mos管p4的栅极相连,mos管p3的漏极接入基本电流ib,mos管p4的漏极与运算放大器的电源流端相连。

11.采取以上方案,具有以下优点:

12.由于本发明的用于动态偏置电流ldo的低启动电流电路的mos管n3的源极与电阻r3的一端相连,电阻r3的另一端接地,功率电路的输出端与比较器的同相输入端相连,比较器的反向输入端接入vin,比较器的输出端与mos管n3的源极相连。工作时,当输入电压较低时,mos管n6处于关断状态,电阻r3选取较大阻值,在静态时,因为r3阻值较大当有小电流流过时n3的源端被拉高进入半导通状态,r3相当于起到截止作用,从而降低了电路的静态功耗。当输入电压大于输出电压一定值时比较器的输出端拉高,n6导通,电阻r3被n6短路,mos管n3的源极与漏极间可以流过较大电流,从而使得功率电路得到驱动电压,整个芯片正常工作,从而避免了启动时静态电流过大的问题,当输入电压大于输出电压一定值时流经p5、n3的路径只需极小电流就可保证输出轻载正常,不存在此问题。

附图说明

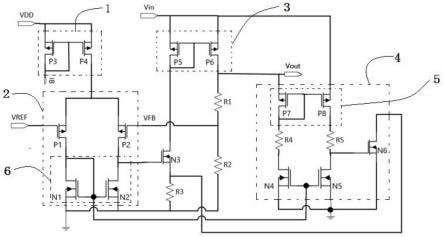

13.图1是背景技术中p型差分对运输放大器的ldo的电路示意图;

14.图2是本发明的用于动态偏置电流ldo的低启动电流电路的电路示意图;

15.图3是在vin从0v到5v做dc扫描的未加本发明电路的ldo的静态电流波形和输出电压波形图;

16.图4是在vin从0v到5v做dc扫描的加了本发明电路的ldo的静态电流波形和输出电压波形图;

具体实施方式

17.以下结合附图对本发明做进一步详细说明。

18.如图2所示,本发明的用于动态偏置电流ldo的低启动电流电路包括功率电路、控制电路和比较器4。所述功率电路的输入端接入vin,输出端输出vout。所述控制电路包括运算放大器2和mos管n3,运算放大器2的同相输入端接入基准电压vref,运算放大器2的反相输入端与控制电路适配连接,运算放大器2的反相输入端用于接收控制电路的电压反馈

vfb,运算放大器2的输出端与mos管n3的栅极相连,mos管n3的漏极与功率电路适配连接。所述mos管n3的源极与电阻r3的一端相连,电阻r3的另一端接地。所述功率电路的输出端与比较器4的同相输入端相连,比较器4的反向输入端接入vin,比较器4的输出端与mos管n3的源极相连。所述功率电路的输出端与电阻r1的一端相连,电阻r1的另一端分别与运输放大器的输出端和电阻r2的一端相连,电阻r2的另一端接地。

19.其中,电阻r2起到的是大电阻作用,可用其它能够实现大电阻作用电器元件代替。

20.所述功率电路含有电流镜一3,电流镜一3包括mos管p5和mos管p6。所述mos管p5的源极和mos管p6的源极均与vin相连,mos管p5的栅极分别与mos管p5的漏极和mos管p6的栅极相连,mos管p5的漏极与所述mos管n3的漏极相连,mos管p6的漏极即为功率电路的输出端。

21.所述运算放大器2含有mos管p1、mos管p2和电流镜二6,电流镜二6包括mos管n1和mos管n2。所述mos管p1的栅极为运算放大器2的同相输入端,mos管p2的栅极为运算放大器2的反相输入端,mos管p1的源极与mos管p2的源极相连、形成运算放大器2的电源流端。所述mos管p1的漏极分别与mos管n1的漏极、mos管n1的栅极和mos管n2的栅极相连,mos管n1的源极和mos管n2的源极接地。所述mos管p2的漏极即为运算放大器2的输出端,且与mos管p2的漏极与mos管n2的漏极相连。

22.所述比较器4含有差分对5、电阻r4、电阻r5、mos管n4、mos管n5和mos管n6。所述差分对5为电流比较器的差分对。所述差分对5含有mos管p7和mos管p8。所述mos管p7的源极为比较器4的同相输入端,所述mos管p8的源极为比较器4的反相输入端,所述mos管n6漏极为比较器4的输出端。所述mos管p7栅极分别与mos管p7的漏极和mos管p8栅极相连,mos管p7的漏极与电阻r4的一端相连,电阻r4的另一端与mos管n4的漏极相连,mos管n4的源极接地,mos管n4的栅极分别与mos管n5的栅极和mos管n1的栅极相连。所述mos管p8的漏极与电阻r5的一端相连,电阻r5的另一端分别与mos管n6的栅极和mos管n5的漏极相连,mos管n5和与mos管n6的源极均接地。

23.所述运算放大器2的电源流端适配连接有电流镜四1,电流镜四1含有mos管p3和mos管p4,mos管p3的源极和mos管p4的源极均接电源vdd,mos管p3的栅极分别与其漏极和mos管p4的栅极相连,mos管p3的漏极接入基本电流ib,mos管p4的漏极与运算放大器2的电源流端相连。

24.本发明的动态偏置电流ldo的低启动电流电路利用电阻r3,限制静态功耗过大,增加一个由r4、r5、p7、p8、n4、n5、n6组成的比较器4,当输入电压大于输出电压一定值时n6导通,芯片正常工作,此值通过调整p7、p8的比例以及r4、r5的阻值决定。

25.本实施例中,电阻r3的阻值大于1兆欧,在静态时,因为r3阻值较大当有小电流流过时n3的源端被拉高进入半导通状态,r3相当于起到截止作用,从而降低了电路的静态功耗。

26.当vin大于vout一定值此值通过调整mos管p7、mos管p8的比例以及电阻r4、电阻r5的阻值决定时,运算放大器2输出端发出信号,mos管n3导通,比较器4的输出端拉高,信号经过mos管n3作为电流镜一3的基本电流输入到电流镜一3中,ldo正常工作。

27.图3和图4为vin从0v到5v做dc扫描的ldo仿真波形,图3和图4上半部分为静态电流波形,下半部分为输出电压波形,如图3所示,未加本发明电路的ldo前静态功耗最大约2ma。

如图4所示,加了本发明电路之后的ldo静态功耗最大约2ua,大大降低了ldo的静态功耗,完美解决启动时静态电流过大问题。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1