时钟电路和电子设备的制作方法

1.本技术涉及电路领域,尤其涉及时钟电路和电子设备。

背景技术:

2.时钟电路,是电子设备中必不可少的电路,由于电子设备中的各种工作、任务调度均是按时间顺序进行,需要一个准确的时间,时钟电路即为电子设备中产生时间的电路。

3.在时钟电路设计中,抖动是十分关键的因素。抖动是指信号的定时事件与其理想位置之间的偏差,抖动会对时钟的精确度造成影响,抖动越大,时钟电路的准确度越低。因此,如何降低时钟电路的抖动,成为了一个亟需解决的问题。

技术实现要素:

4.本技术提供时钟电路和电子设备,以解决时钟电路的抖动问题。

5.第一方面,本技术提供一种时钟电路,所述时钟电路包括带隙基准模块和振荡模块,其中:

6.所述带隙基准模块与所述振荡模块连接,用于产生正温度系数电流和负温度系数电流,并将由所述正温度系数电流和所述负温度系数组合得到的组合电流输入给所述振荡模块;

7.所述振荡模块用于基于所述组合电流产生时钟信号。

8.在一种可能的设计中,所述带隙基准模块包括偏置单元和电流产生单元,其中:所述偏置单元的一端与电源连接,所述偏置单元的另一端与所述电流产生单元的触发端连接,用于触发所述电流产生单元工作;所述电流产生单元的输入端与所述电源连接,所述电流产生单元的输出端与所述振荡模块连接,用于在所述偏置单元的触发下产生所述正温度系数电流和负温度系数电流。

9.在一种可能的设计中,所述电流产生单元包括等电流产生子电路和电流输出子电路,其中:所述等电流产生子电路的输入端与所述电源连接,所述等电流产生子电路的两个输出端分别与所述电流输出子电路的两个输入端连接,所述等电流产生子电路用于产生并向所述电流输出子电路输出两路相等的电流;所述电流输出子电路的触发端与所述偏置单元连接,所述电流输出子电路的输出端与所述振荡模块连接,所述电流输出子电路用于在所述偏置单元的触发下,基于所述两路相等的电流,向所述振荡模块输出所述正温度系数电流和负温度系数电流。

10.在一种可能的设计中,所述电流输出子电路包括第一电阻、第二电阻、第一三极管和第二三极管,其中:第一电阻的一端与所述第一三极管的基极、所述第二三极管的基极连接,所述第一电阻的另一端与所述第二电阻的一端、所述第一三极管的发射极以及所述振荡模块连接,所述第二电阻的另一端与所述第二三极管的发射极连接,所述第一三极管的集电极、所述第二三极管的集电极分别与所述等电流产生子电路的两个输出端连接。

11.在一种可能的设计中,所述等电流产生子电路包括第三电阻、第四电阻、第一运算

放大器和第一mos管,其中:所述第三电阻的一端、所述第四电阻的一端与所述电源连接,所述第三电阻的另一端与所述第一运算放大器的第一输入端以及所述电流输出子电路的一个输入端连接,所述第四电阻的另一端与所述第一运算放大器的第二输入端、所述第一mos管的源极连接,所述第一运算放大器的输出端与所述第一mos管的栅极连接,所述第一mos管的漏极与所述电流输出子电路的另一个输入端连接。

12.在一种可能的设计中,所述偏置单元包括第二mos管,所述第二mos管的栅极与所述第三电阻的另一端、所述第一运算放大器的第一输入端以及所述电流输出子电路的一个输入端连接,所述第二mos管的源极与所述电流输出子电路的触发端连接,所述第二mos管的漏极与所述电源连接。

13.在一种可能的设计中,所述等电流产生子电路包括第三mos管、第四mos管和第二运算放大器,其中:所述第三mos管的源极、所述第四mos管的源极与所述电源连接,所述第三mos管的栅极与所述第二运算放大器的输出端、所述第四mos管的栅极连接,所述第三mos管的漏极与所述第二运算放大器的第一输入端、所述电流输出子电路的一个输入端连接,所述第四mos管的漏极与所述第二运算放大器的第二输入端、所述电流输出子电路的另一个输入端连接。

14.在一种可能的设计中,所述偏置单元包括第五mos管,所述第五mos管的栅极与所述第四mos管的漏极、所述第二运算放大器的第二输入端以及所述电流输出子电路的另一个输入端连接,所述第四mos管的源极与所述电流输出子电路的触发端连接,所述第四mos管的漏极与所述电源连接。

15.在一种可能的设计中,所述振荡模块为环形震荡器。

16.第二方面,提供一种电子设备,包括控制系统和第一方面所述的时钟电路;其中:所述时钟电路用于为所述控制系统产生时钟信号。

17.本技术可以实现如下技术效果:本技术中的时钟电路,包括带隙基准模块和振荡模块,所述带隙基准模块与所述振荡模块连接,用于产生正温度系数电流和负温度系数电流,并将由所述正温度系数电流和所述负温度系数组合得到的组合电流输入给所述振荡模块;所述振荡模块用于基于所述组合电流产生时钟信号。由于是直接将带隙基准模块与振荡模块连接,带隙基准模块产生的正温度系数电流和负温度系数电流组合后直接输入给振荡模块,避免组合电流经过电流镜像结构而产生噪声,从而可以减少时钟电路的抖动,提高时钟电路的精准度;直接将由正温度系数电流和负温度系数电流组合得到的组合电流输入给振荡模块,还可以实现对工作电流的充分利用,可以降低时钟电路的功耗。

附图说明

18.图1为本技术实施例提供的一种电子设备的结构框图;

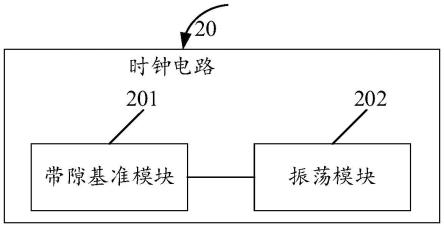

19.图2为本技术实施例提供的一种时钟电路的结构框图;

20.图3为本技术实施例提供的一种带隙基准模块的结构框图;

21.图4为本技术实施例提供的一种电流产生单元的结构框图;

22.图5为本技术实施例提供的时钟电路的一种电路原理图;

23.图6为本技术实施例提供的另一种时钟电路的另一种电路原理图。

具体实施方式

24.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行描述。

25.本技术的时钟电路可适用于基于时钟电路产生时钟以进行工作的电子设备,电子设备包括但不限于为电子播放器、电子表、蓝耳耳机等等。

26.首先参见图1,图1为本技术实施例提供的一种电子设备的结构框图。如图1所示,电子设备1可包括控制系统10和时钟电路20,其中,时钟电路20与控制系统10连接,用于为控制系统产生时钟信号。具体地,控制系统10为电子设备中用于实现各种控制的电路系统,控制系统10具体可以包括中央处理单元(central processing unit,cpu)或微处理单元(microcontroller unit,mcu)等。不同的电子设备,控制系统实现的控制不同。例如,在电子播放器中,控制系统可以实现音频播放相关的各种控制;在蓝牙耳机中,控制系统可以实现蓝牙控制以及音频播放相关的各种控制;在键盘中,控制系统可以实现各种按键控制;不限于这里举例。可选地,电子设备还可以包括电源系统、负载等电路模块,本技术不做限制。

27.接下来参见图2,图2为本技术实施例提供的一种时钟电路的结构框图。如图2所示,时钟电路20包括带隙基准模块201和振荡模块202,其中:

28.所述带隙基准模块201与所述振荡模块202连接,用于产生正温度系数电流和负温度系数电流,并将由所述正温度系数电流和所述负温度系数组合得到的组合电流输入给所述振荡模块202;

29.所述振荡模块202用于基于所述组合电流产生时钟信号。

30.其中,带隙基准模块201可以为任意一种能同时产生正温度系数电流和负温度系数电流的电路模块。振荡模块202可以为任意一种能够产生时钟信号的振荡电路。具体地,振荡模块202可以环形振荡器,即将奇数个反相器串联在一起,把最后一级的输出反馈给第一极的输入,从而在逻辑上产生振荡的振荡电路。

31.本技术的总体技术原理如下:带隙基准模块201产生正温度系数电流和负温度系数电流,然后将正温度系数电流和负温度系数电流组合后输入给振荡模块202。由于是带隙基准模块201直接将正温度系数电流和负温度系数电流组合后输入给振荡模块202,输入给振荡模块202的组合电流为零温度系数电流,不受温度影响,相较于经过电流镜像结构输出的电流,直接将零温度系数电流输入给振荡模块可以减小噪声,从而可以减少时钟电路的抖动,提高时钟电路的精准度;直接将由正温度系数电流和负温度系数电流组合得到的组合电流输入给振荡模块,还可以实现对工作电流的充分利用,可以降低时钟电路的功耗。

32.以下介绍实现上述时钟电路的一些具体电路设计。参见图3-图6。

33.在一些可能的设计中,如图3所示,所述带隙基准模块201包括偏置单元2011和电流产生单元2012;其中:所述偏置单元2011的一端与电源连接,所述偏置单元2011的另一端与所述电流产生单元2012的触发端连接,用于触发所述电流产生单元2011工作;所述电流产生单元2012的输入端与所述电源连接,所述电流产生单元2012的输出端与所述振荡模块连接,用于在所述偏置单元2011的触发下产生所述正温度系数电流和负温度系数电流。通过设置偏置单元,能够对电流产生单元进行触发,使得电流产生单元能够在电源上电时摆脱简并偏置点,从而能够正常产生正温度系数电流和负温度系数电流。

34.在一些具体设计中,如图4所示,电流产生单元2011可以包括等电流产生子电路2011a和电流输出子电路2011b;所述等电流产生子电路2011a的输入端与所述电源连接,所

述等电流产生子电路2011b的两个输出端分别与所述电流输出子电路2011a的两个输入端连接,所述等电流产生子电路2011b用于向所述电流输出子电路2011a输出两路相等的电流;所述电流输出子电路2011b的触发端与所述偏置单元连接,所述电流输出子电路2011b的输出端与所述振荡模块连接,所述电流输出子电路2011b用于在所述偏置单元的触发下,基于所述两路相等的电流,向所述振荡模块输出所述正温度系数电流和负温度系数电流。

35.在一种具体实现方式中,所述电流输出子电路可以包括第一电阻、第二电阻、第一三极管和第二三极管,其中:第一电阻的一端与所述第一三极管的基极、所述第二三极管的基极连接,所述第一电阻的另一端与所述第二电阻的一端、所述第一三极管的发射极以及所述振荡模块连接,所述第二电阻的另一端与所述第二三极管的发射极连接,所述第一三极管的集电极、所述第二三极管的集电极分别与所述等电流产生子电路的两个输出端连接。

36.示例性地,第一电阻可以为图5或图6中的电阻r1,第二电阻可以为图5或图6中的电阻r2,第一三极管可以为图5或图6中的npn三极管q1,第二三极管可以为图5或图6中的npn三极管q2。

37.在一种具体实现方式中,所述等电流产生子电路可以包括第三电阻、第四电阻、第一运算放大器和第一mos管,其中:所述第三电阻的一端、所述第四电阻的一端与所述电源连接,所述第三电阻的另一端与所述第一运算放大器的第一输入端以及所述电流输出子电路的一个输入端连接,所述第四电阻的另一端与所述第一运算放大器的第二输入端、所述第一mos管的源极连接,所述第一运算放大器的输出端与所述第一mos管的栅极连接,所述第一mos管的漏极与所述电流输出子电路的另一个输入端连接。

38.示例性地,第三电阻可以为图5中的电阻r3,第四电阻可以为图5中的电阻r4,电阻r3和电阻r4的阻值相同,第一运算放大器可以为图5中的运算放大器amp1,第一mos管可以为图5中的pmos管p1。

39.在等电流产生子电路包括上述第三电阻、第四电阻、第一运算放大器和第一mos管的情况下,上述偏置单元可以包括第二mos管,所述第二mos管的栅极与所述第三电阻的另一端、所述第一运算放大器的第一输入端以及所述电流输出子电路的一个输入端连接,所述第二mos管的源极与所述电流输出子电路的触发端连接,所述第二mos管的漏极与所述电源连接。

40.示例性地,第二mos管可以为图5中的nmos管n1。

41.其中,图5所示的带隙基准模块的工作原理如下:

42.运放闭环使得第一运算放大器amp1两个输入端的电压相等,第三电阻r3与第四电阻r4的阻值相等,故流经第三电阻r3的电流和流经第四电阻r4的电流相等;第二mos管n1的栅极为高电平,第二mos管n1导通,将第一三极管q1和第二三极管q2的基极上拉为高电平,第一三极管q1和第二三极管q2导通;流经第三电阻r3的电流流经第一三极管q1流向振荡模块,流经第一三极管q1的电流等于两个三极管(即第一三极管q和第二三极管q2)的集电极和发射极间的电压差与第二电阻的比值,流经第一三极管q1的电流为正温度系数电流;流经第四电阻r4的电流流经第二三极管q2流向振荡模块,由于流经第三电阻r3的电流和流经第四电阻r4的电流相等,故流经第二三极管q2的电流等于流经第一三极管q1的电流,即等于两个三极管(即第一三极管q和第二三极管q2)的集电极和发射极间的电压差与第二电阻

r2的商,流经第二三极管q1的电流为正温度系数电流;流经第一电阻r1的电流等于第二三极管q2的集电极和发射极间的电压与第一电阻r1的阻值,流经第一电阻r1的电流为负温度系数电流;因此,流向振荡模块的电流为正温度系数电流和负温度系数电流的组合电流,即为零温度系数电流。

43.在另一种具体实现方式中,所述等电流产生子电路包括第三mos管、第四mos管和第二运算放大器,其中:所述第三mos管的源极、所述第四mos管的源极与所述电源连接,所述第三mos管的栅极与所述第二运算放大器的输出端、所述第四mos管的栅极连接,所述第三mos管的漏极与所述第二运算放大器的第一输入端、所述电流输出子电路的一个输入端连接,所述第四mos管的漏极与所述第二运算放大器的第二输入端、所述电流输出子电路的另一个输入端连接。

44.示例性地,第三mos管可以为图6中的pmos管p2,第四mos管可以为图6中的pmos管p3,第二预算放大器可以为图6中的运算放大器amp2,运算放大器amp2的同相输入端与第三mos管p2的漏极连接,运算放大器amp2的反相输入端与第四mos管p3的漏极连接,运算放大器amp2的输出端与第三mos管p2、第四mos管p3的栅极连接,第三mos管p2和第四mos管p3的源极与电源连接。

45.在等电流产生子电路包括上述第三mos管、第四mos管和第二运算放大器的情况下,所述偏置单元可以包括第五mos管,所述第五mos管的栅极与所述第四mos管的漏极、所述第二运算放大器的第二输入端以及所述电流输出子电路的另一个输入端连接,所述第四mos管的源极与所述电流输出子电路的触发端连接,所述第四mos管的漏极与所述电源连接。

46.示例性地,第五mos管可以为图6中的nmos管n2。

47.图6所示的带隙基准模块的工作原理如下:

48.运算放大器amp2的两个输入端的电压相等,运算放大器输出低电平,第三mos管p2和第四mos管p3导通,流经第三mos管p2和第四mos管p3的电路相等;第五mos管n2的栅极为高电平,第五mos管n2导通将第一三极管q1和第二三极管q2的基极上拉为高电平,第一三极管q1和第二三极管q2导通;流经第三mos管p2的电流流经第一三极管q1流向振荡模块,流经第一三极管q1的电流等于两个三极管(即第一三极管q和第二三极管q2)的集电极和发射极间的电压差与第二电阻的比值,流经第一三极管q1的电流为正温度系数电流;流经第四mos管p3的电流流经第四电阻r4的电流流经第二三极管q2流向振荡模块,由于流经第三电阻r3的电流和流经第四电阻r4的电流相等,故流经第二三极管q2的电流等于流经第一三极管q1的电流,即等于两个三极管(即第一三极管q和第二三极管q2)的集电极和发射极间的电压差与第二电阻r2的商,流经第二三极管q1的电流为正温度系数电流;流经第一电阻r1的电流等于第二三极管q2的集电极和发射极间的电压与第一电阻r1的阻值,流经第一电阻r1的电流为负温度系数电流;因此,流向振荡模块的电流为正温度系数电流和负温度系数电流的组合电流,即为零温度系数电流。

49.结合上述图5-图6的电路可知,上述电路基于带隙基准电路结构,将正温度系数电流和负温度系数电流进行组合,直接输入给振荡模块,带隙基准电路产生的电流得到充分利用,降低了时钟电路的功耗;并且,带隙基准电路结构和振荡模块之间没有镜像结构,减少噪声产生,从而可以减少时钟电路的抖动,提高时钟电路的精准度。

50.以上所揭露的仅为本实用新型较佳实施例而已,当然不能以此来限定本实用新型之权利范围,因此依本实用新型权利要求所作的等同变化,仍属本实用新型所涵盖的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1