一种硬件可编程音频芯片、系统及在线升级方法与流程

1.本发明涉及芯片设计技术领域,尤其涉及一种硬件可编程音频芯片、系统及在线升级方法。

背景技术:

2.目前的音频芯片多采用通用处理器方案,受通用处理器器处理能力的限制,只能够实现基本的音频播放和录音,以及部分简单的音频处理算法。随着半导体技术和人工智能技术的发展,作为一种端设备,音频芯片不仅要完成基本的音频播放和录音,还需要实现越来越复杂的音频处理算法,但当前的音频芯片在制造完成后,其内部的硬件电路就已固化,无法更改,导致难以更新或者增加新的音频处理功能。

技术实现要素:

3.为解决背景技术中存在的技术问题,本发明提出一种硬件可编程音频芯片、系统及在线升级方法,可以通过重构硬件电路的方式更新或者增加新的音频处理功能,同时获得相比通用处理器方案更快的处理能力。

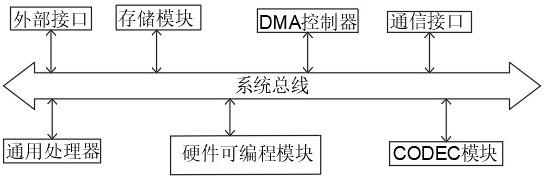

4.本发明提出一种硬件可编程音频芯片,包括:通用处理器、硬件可编程模块、存储模块、通信接口、系统总线,通信接口与系统总线连接,用于接收或发送数据,其中数据包括音频数据、升级数据;存储模块与系统总线连接,用于储存数据;通用处理器与系统总线连接,用于实现标准的音频协议栈、基本的音频数据访问控制和在线升级方法;硬件可编程模块与系统总线连接,用于通过在线升级方法并依据升级数据中的配置数据进行电路重构以实现不同的音频算法。

5.优选地,所述硬件可编程模块具体为efpga模块,efpga模块包括efpga配置器和efpga单元,其中efpga配置器和efpga单元均与系统总线连接,且efpga配置器还与efpga单元连接,efpga配置器用于接收经由系统总线转发的配置数据并将接收到的配置数据写入到efpga单元中,efpga单元依据所接收的配置数据进行电路重构。

6.优选地,还包括codec模块、dma模块和外部接口,codec模块、dma模块和外部接口均与系统总线连接,其中codec模块用于播放音频数据或采集录音数据,dma模块用于芯片内部数据搬运。

7.本发明提出的一种硬件可编程音频芯片系统,包括上位机和上述硬件可编程音频芯片,上位机与硬件可编程音频芯片通过通信接口连接,以实现信息交互,上位机中安装有上位机软件,以指定用户程序、配置数据以及在线升级的启动和停止。

8.基于上述的一种硬件可编程音频芯片系统,本发明提出的一种硬件可编程音频芯片在线升级方法,包括以下步骤:

s1、接收来自上位机的升级数据和原始校验字,升级数据中包括用于电路重构的配置数据;s2、对升级数据进行校验以得到本地校验字;s3、对本地校验字与原始校验字进行匹配,当匹配成功后,执行s4;s4、在升级数据中提取出配置数据并进行电路重构。

9.优选地,升级数据中还包括用于下位机软件升级的数据包;“s4”进一步包括:当匹配成功后,在升级数据中提取出数据包并进行下位机软件升级。

10.优选地,“s3”进一步包括:当匹配失败后,执行s5;s5、上位机发出错误提示:优选地,“s1”具体包括:s11、接收来自上位机的升级命令并对升级命令进行响应,当响应成功后,向上位机反馈成功响应报文后执行s12;s12、接收来自上位机的升级数据和原始校验字,升级数据中包括用于电路重构的配置数据。

11.优选地,“s11”进一步包括:当响应失败后,执行s5。

12.本发明中硬件可编程音频芯片,采用通用处理器、硬件可编程模块的方案,在基本音频功能的基础上,通过efpga模块来实现丰富复杂的音频处理算法,除了能够实现丰富复杂的音频处理算法之外,本发明针对硬件可编程音频芯片所提出的在线升级方法对芯片进行软件升级及efpga单元重配置,efpga单元重配置时替换efpga单元原有的配置数据,对efpga单元进行在线配置,从而实现芯片的在线升级以更新或者增加新的音频处理功能,避免了芯片返厂,方便终端客户使用。

附图说明

13.图1为本发明提出的一种硬件可编程音频芯片的结构示意图;图2为本发明提出的一种硬件可编程音频芯片中efpga模块第一结构示意图;图3为本发明提出的一种硬件可编程音频芯片中efpga模块第二结构示意图;图4为播放数据格式转换模块的结构示意图;图5为录音数据格式转换模块的结构示意图;图6为接口模块的结构示意图;图7为efpga模块的第三结构示意图;图8为本发明提出的一种硬件可编程音频芯片系统结构示意图;图9为本发明提出的一种硬件可编程音频芯片在线升级方法的流程示意图。

实施方式

14.参照图1,本发明提出一种硬件可编程音频芯片,包括:通信接口、通用处理器、存储模块、硬件可编程模块、系统总线,其中系统总线连接芯片中的各个模块。

15.存储模块与系统总线连接,用于储存数据,其中数据包括音频数据、升级数据,且

升级数据中包含有配置数据,还用于存储其他程序运行所需的堆栈数据。

16.通信接口与系统总线连接,用于接收或发送数据。

17.通用处理器与系统总线连接,用于实现标准的音频协议栈、基本的音频数据访问,例如播放、录音等,还用于实现控制在线升级,以使得与系统总线连接的硬件可编程模块,可通过在线升级方法并依据配置数据进行电路重构以实现不同的音频算法。

18.需要说明的是,硬件可编程音频芯片与传统音频芯片的区别在于添加硬件可编程模块,可依据需要写入不同配置数据,硬件可编程模块通过在线升级方法并依据配置数据进行电路重构。

19.参照图2,需要进一步说明的是,硬件可编程模块可具体为efpga模块,用来实现丰富复杂的音频处理算法,例如回声消除、降噪滤波、语音识别、声源定位等。

20.其中efpga模块包括efpga配置器和efpga单元,其中efpga配置器和efpga单元均与系统总线连接,且efpga配置器还与efpga单元连接,efpga配置器用于接收配置数据并将接收到的配置数据写入到efpga单元中,efpga单元依据所接收的配置数据进行电路重构以升级现有功能电路和增加新的音频处理功能电路。

21.参照图1,上述实施例中的硬件可编程音频芯片还包括codec模块、dma模块和外部接口,codec模块、dma模块和外部接口均与系统总线连接,其中codec模块用于播放音频数据或采集录音数据,dma模块用于芯片内部数据的搬运,外部接口包括串口、i2c、pwm、通用io等接口,用于实现辅助功能,譬如打印调试信息、配置控制外接芯片、外接开关等。

22.进一步的,硬件可编程模块通过在线升级方法进行电路重构的过程中,通信接口与系统总线以及上位机通信连接,接收来自上位机的升级数据、原始校验字,并对接收到的升级数据、原始校验字通过系统总线进行转发,升级数据中包括用于电路重构的配置数据。

23.通用处理器与系统总线通讯连接,以获取经由系统总线转发的升级数据、原始校验字,并获取的升级数据进行校验以得到本地校验字,还用于将本地校验字与原始校验字进行匹配,并在匹配成功后,从升级数据中提取出配置数据并通过系统总线进行转发。

24.存储模块,与系统总线连接,并用于存储由系统总线转发的升级数据、原始校验字。

25.升级数据中还包含用于下位机软件升级的数据包,其中存储模块包括flash存储器和sram存储器,下位机软件和升级数据储存在flash存储器内,下位机软件可基于升级数据中的数据包进行升级更新。

26.硬件可编程模块,与系统总线连接,以获取系统总线转发的配置数据,并依据配置数据进行电路重构。

27.本实施例中,通信接口用于接受升级数据和原始校验字,并将升级数据和原始校验字进行转发,通用处理器接收到升级数据和原始校验字后,对升级数据进行计算得到本地校验字,并对本地校验字与原始校验字进行比对,当本地校验字与原始校验字相同时,比对成功。比对成功后,通用处理器从升级数据中提取出配置数据或数据包,存储模块中的下位机软件依据数据包进行升级更新,而efpga模块依据提取出来的配置数据进行电路重构,以实现不同的音频算法。

28.参照图3,为实现音频源与播放源之间的采样率转换算法和精度转换算法,efpga单元与系统总线连接,上述硬件可编程音频芯片通过在线升级方法进行电路重构后,efpga

单元包括播放数据格式转换模块、录音数据格式转换模块、接口模块,播放数据格式转换模块、录音数据格式转换模块均与接口模块连接。

29.参照图4,播放数据格式转换模块包括音频下采样单元、第一音频fifo单元和第一音频输出单元,第一音频输出单元、音频下采样单元均与第一音频fifo单元及接口模块连接,音频下采样单元接收由上位机传输的原始音频数据,然后对原始音频数据进行抽取处理,音频下采样单元将经过抽取处理后的音频数据传送给第一音频fifo单元进行缓存,第一音频fifo单元将缓存后的音频数据传送给第一音频输出单元,第一音频输出单元通过接口模块、系统总线将音频数据传送给codec模块,当codec模块外接扬声器时,可播放音频,例如上位机输出的音频数据为96k 24bit,那么音频下采样单元可将96k 24bit抽取为48k 16bit的音频数据。

30.参照图5,而录音数据格式转换模块包括音频上采样单元、第二音频fifo单元和第二音频输出单元,音频上采样单元、第二音频输出单元均与第二音频fifo单元级接口模块连接,codec模块外接麦克风时,音频上采样单元接收由codec模块传输的原始音频数据,然后对原始音频数据进行扩充处理,音频上采样单元将经过扩充处理后的音频数据传送给第二音频fifo单元进行缓存,第二音频fifo单元将缓存后的音频数据传送给第二音频输出单元,第二音频输出单元通过接口模块、系统总线将音频数据传送给上位机,例如codec模块输出的音频数据为48k 16bit,那么音频上采样单元可将48k 16bit扩充为96k 24bit的音频数据。

31.参照图6,接口模块具体包括内部接口、总线接口、dma接口、中断接口和寄存器组,其中寄存器组、音频下采样单元、第一音频输出单元、音频上采样单元、第二音频输出单元均与内部接口连接,总线接口与系统总线、内部接口、寄存器组连接,以接收来自系统总线的读写操作,并将系统总线的读写操作转换为寄存器组的读写操作和内部接口的读写操作,内部接口读取的音频数据传送给音频下采样单元或者传送给音频上采样单元,使得音频下采样单元或音频上采样单元对音频数据进行处理。

32.参照图6,寄存器组包括播放音频寄存器、录音音频寄存器和模式寄存器,其中模式寄存器与中断接口连接,播放音频寄存器包括播放原始数据寄存器、播放音频fifo状态寄存器和播放结果数据寄存器,录音音频寄存器包括录音原始数据寄存器、录音音频fifo状态寄存器、录音结果数据寄存器,播放音频fifo状态寄存器、录音音频fifo状态寄存器均与总线接口连接,以将播放音频fifo状态寄存器的空间状态和录音音频fifo状态寄存器的空间状态通过总线接口和系统总线传送给通用处理器,通用处理器根据播放音频fifo状态寄存器以及录音音频fifo状态寄存器的空间状态判断上位机与本地的音频时钟差异,从而进行速率调节。播放原始数据寄存器和播放结果数据寄存器均与总线接口连接,通用处理器根据速率调节的需要,控制播放原始数据的流入和播放结果数据的流出。录音原始数据寄存器和录音结果数据寄存器均与总线接口连接,通用处理器根据速率调节的需要,控制录音原始数据的流入和录音结果数据的流出。

33.播放音频fifo状态寄存器的空间状态、录音音频fifo状态寄存器的空间状态判断及速率调节具体如下:通用处理器会在每一次写入播放原始数据之前检查播放音频fifo状态寄存器,如果播放音频fifo状态寄存器的空间被占用四分之三及以上,说明上位机的音频时钟的频率

比本地音频时钟高,通用处理器会通过反馈报文告知上位机降低发送音频数据的速度,如果播放音频fifo状态寄存器的空间被占用四分之一及以下,说明上位机音频时钟的频率比本地音频时钟低,通用处理器会通过反馈报文告知上位机增加发送音频数据的速度。

34.通用处理器会在每一次读取录音结果数据之前检查录音音频fifo状态寄存器,如果录音音频fifo状态寄存器的空间被占用四分之三及以上,说明上位机音频时钟的频率比本地音频时钟低,通用处理器会增加每次发往上位机的录音数据,如果录音音频fifo状态寄存器的空间被占用四分之一及以下,说明上位机音频时钟的频率比本地音频时钟高,通用处理器会减少每次发往上位机的录音数据。

35.dma接口和中断接口均与寄存器组连接,dma接口将寄存器组中的音频状态寄存器转换为dma握手信号、中断信号。

36.当硬件可编程音频芯片面对各种各样的升级需求时,例如当efpga单元需要增设语音识别模块时,参照图7,现有的芯片往往需要重新选型或者重新流片才能完成系统功能的升级,可将需要映射的语音识别算法硬化到efpga单元,然后通过在线升级方法将配置数据烧录到存储模块中的flash存储器中,替换原有的配置数据,以实现硬件的在线升级,而下位机软件可依据上位机发送的升级数据中的数据包进行更新,以实现下位机软件的在线升级,从而避免了芯片的返厂,方便终端客户的使用。

37.参照图8,基于同一发明构思,本发明还提出一种硬件可编程音频芯片系统,包括上位机和下位机,下位机具体为上述硬件可编程音频芯片,上位机与硬件可编程音频芯片通过通信接口连接,以实现信息交互。

38.需要进一步说明的是,通信接口与上位机之间可通过线缆实现有线连接,也可通过无线实现通信连接。

39.上位机中安装有上位机软件,上位机软件具体为图形界面,以指定用户程序、配置数据以及在线升级的启动和停止,硬件可编程芯片中还包括在线升级协议,在线升级协议定义了在线升级流程和在线升级过程中所需的报文格式,以实现在线升级方法。

40.参照图9,本发明提出的一种硬件可编程音频芯片在线升级方法,可应用于上述硬件可编程音频芯片,包括以下步骤:s1、接收来自上位机的升级数据和原始校验字,升级数据中包括用于电路重构的配置数据。

41.需要进一步说明的是,升级数据中还可包括用于下位机软件升级的数据包。

42.s1具体包括:s11、接收来自上位机的升级命令并对升级命令进行响应,当响应成功后,向上位机反馈成功响应报文后执行s12;s12、接收来自上位机的升级数据和原始校验字,升级数据中包括用于电路重构的配置数据s2、对升级数据进行校验以得到本地校验字;需要进一步说明的是,对升级数据进行校验以得到本地校验字具体包括:对升级数据中的配置数据进行校验得到的本地校验字以及对升级数据中下位机软件升级的数据包进行校验得到的本地校验字。

43.s3、对本地校验字与原始校验字进行匹配,当匹配成功后,执行s4;

需要进一步说明的是,当升级数据中的配置数据进行校验得到的本地校验字与原始校验字匹配成功时,在升级数据中提取出配置数据,而当升级数据中的数据包进行校验得到的本地校验字与原始校验字匹配成功时,在升级数据中提取出的是数据包。

44.s4、在升级数据中提取出配置数据并进行电路重构。以实现硬件升级需要进一步说明的是,当升级数据中的数据包进行校验得到的本地校验字与原始校验字匹配成功时,在升级数据中提取出的是数据包时,通过数据包对下位机软件进行升级,以实现下位机软件升级。

[0045]“s4”进一步包括:当匹配成功后,在升级数据中提取出数据包并进行下位机软件升级参照图1,上述实施例中,“s4”之后还包括:s5、上位机发出错误提示。

[0046]

当“s3”中的匹配结果为匹配失败时,执行s5;当“s11”中的响应结果为响应失败时,执行s5。

[0047]

以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,根据本发明的技术方案及其发明构思加以等同替换或改变,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1