用于带隙基准电路的启动电路以及芯片的制作方法

本发明涉及集成电路,具体地涉及一种用于带隙基准电路的启动电路以及芯片。

背景技术:

1、随着现今电子业的飞速发展,基准源作为电路的基本单元显得日趋重要。目前,三种最常用的基准源电路为掩埋齐纳(zener)基准源、xfet基准源和带隙(bandgap)基准源,其中应用最广泛最受欢迎的是带隙基准源。随着电源管理芯片的发展,带隙基准源具有与温度、电源电压、工艺几乎无关的优点,其已经被广泛地用于各种电源管理芯片中。带隙基准电路是电源管理芯片中极其重要的电路,其性能决定电源管理芯片的优劣。带隙基准电路一般由带隙电压产生电路、运算放大器和偏置电路组成。

2、启动电路用于启动带隙基准电路,其作用是:在上电时,保证基准电路摆脱零电流状态,而当基准电路正常工作后,启动电路自动关闭。因此,所述启动电路直接关系到带隙基准电路是否可以正常启动以及稳定工作。然而,在现有的用于带隙基准电路的启动电路中,存在启动电路可靠性以及功耗较大等问题。因此,如何保证可靠的启动以及降低启动电路的功耗是亟需解决的问题。

技术实现思路

1、本发明的目的是提供一种用于带隙基准电路的启动电路以及芯片,其在向带隙基准电路提供启动电压之后,可基于带隙基准电路的输出电压来控制启动电压降低,从而极大地提升了带隙基准电路的启动过程的可靠性。

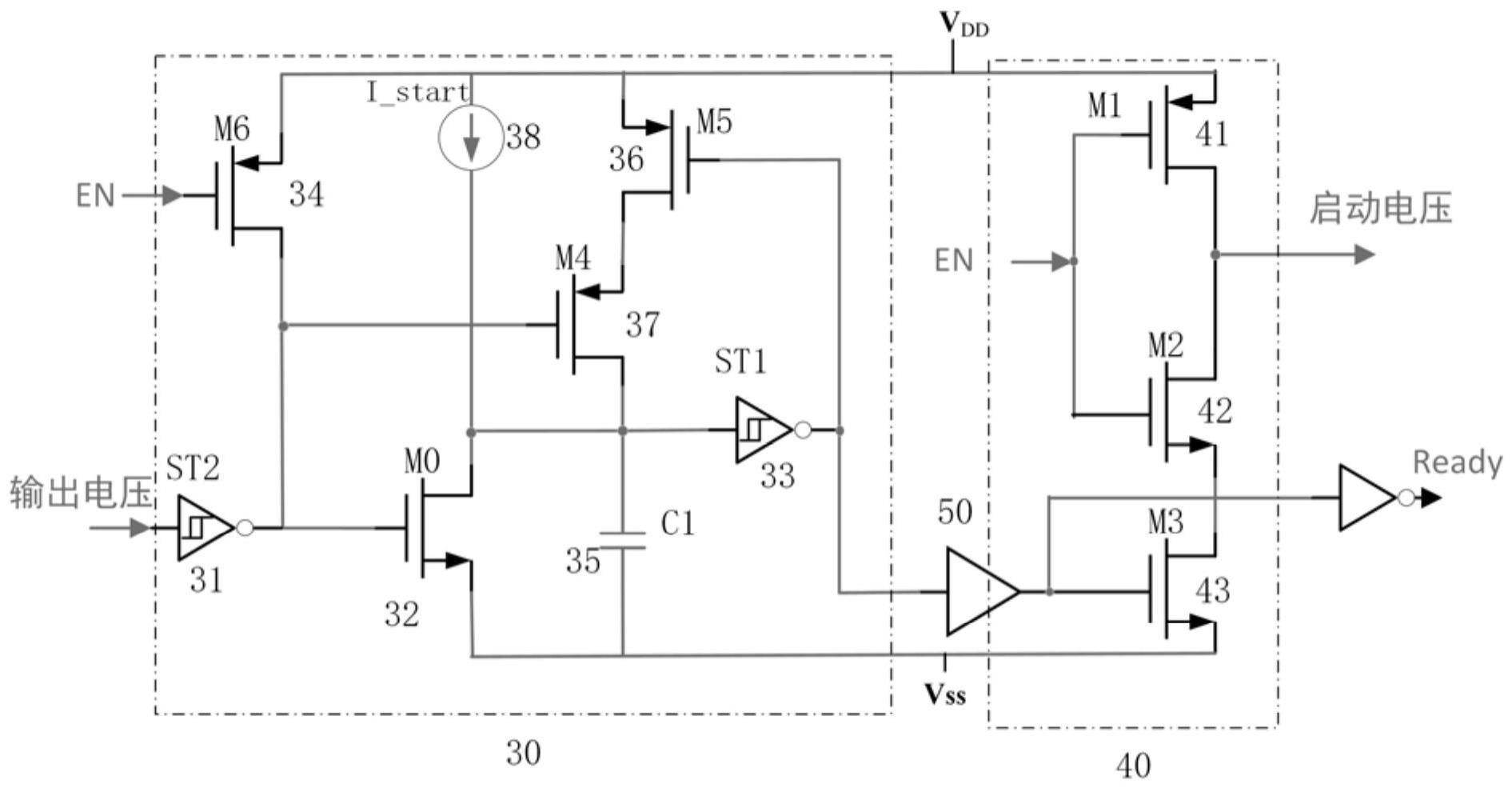

2、为了实现上述目的,本发明第一方面提供一种用于带隙基准电路的启动电路,所述启动电路包括:反馈电路,用于执行以下操作:接收所述带隙基准电路的输出电压以作为第一控制信号;接收第二控制信号;以及在所述第二控制信号被拉高并维持在第一电平的情况下,响应于所述第一控制信号高于0且低于第二电平,输出第三电平,以及控制电路,用于响应于所述第二控制信号被拉高并维持在所述第一电平并且所述反馈电路输出的所述第三电平,控制用于所述带隙基准电路的启动电压降低,其中,所述第一电平等于或高于所述反馈电路与所述控制电路的第一导通电压,所述第二电平低于所述带隙基准电路的目标输出电压,以及所述第三电平高于或等于所述控制电路的第二导通电压。

3、优选地,所述反馈电路还用于,在所述第二控制信号维持在第四电平的情况下,响应于所述第一控制信号为0,输出所述第三电平,其中,所述第四电平低于所述反馈电路与所述控制电路的第一导通电压,相应地,所述控制电路还用于,响应于所述第二控制信号维持在所述第四电平并且所述反馈电路输出的所述第三电平,控制输出所述启动电压。

4、优选地,所述反馈电路包括:第一反相器,所述第一反相器的输入端与所述第一控制信号相连,以及所述第一反相器的开启电平等于所述第二电平;第一n型mos管,所述第一n型mos管的栅极与所述第一反相器的输出端相连;第二反相器,所述第二反相器的输入端与所述第一n型mos管的漏极相连,以及所述第二反相器的开启电平等于所述第一n型mos管的漏极电源的电压;以及第一p型mos管,所述第一p型mos管的栅极与所述第二控制信号相连,以及所述第一p型mos管的导通电压等于所述反馈电路的第一导通电压。

5、优选地,所述反馈电路还包括:电流源,被设置在所述第二反相器的输入端与所述第一n型mos管的漏极相连的连接点与所述漏极电源之间;以及电容,所述电容的一极板同所述第一n型mos管的漏极与所述电流源相连,以及所述电容的另一极板与所述第一n型mos管的源极相连。

6、优选地,所述反馈电路还包括:第二p型mos管,所述第二p型mos管的源极与所述第一p型mos管的源极相连,以及所述第二p型mos管的栅极与所述第二反相器的输出端相连;以及第三p型mos管,所述第三p型mos管的栅极与所述第一p型mos管的漏极相连,所述第三p型mos管的漏极与所述第二反相器的输入端相连,以及所述第三p型mos管的源极与所述第二p型mos管的漏极相连。

7、优选地,所述控制电路包括:第四p型mos管,所述第四p型mos管的栅极与所述第二控制信号相连,所述第四p型mos管的源极与所述第一p型mos管的源极相连,以及所述第四p型mos管的导通电压等于所述控制电路的第一导通电压;第二n型mos管,所述第二n型mos管的栅极与所述第二控制信号相连,所述第二n型mos管的漏极与所述第四p型mos管的漏极相连且连接点用于提供用于所述带隙基准电路的启动电压,以及所述第二n型mos管的导通电压等于所述控制电路的第一导通电压;以及第三n型mos管,所述第三n型mos管的栅极与所述第二反相器的输出端相连,所述第三n型mos管的漏极与所述第二n型mos管的源极相连,以及所述第三n型mos管的导通电压等于所述控制电路的第二导通电压。

8、优选地,所述启动电路还包括:缓冲器,所述缓冲器被设置在所述第二反相器与所述第三n型mos管之间。

9、优选地,所述反馈电路还用于,在所述第一控制信号满足以下异常条件的情况下,响应于所述第二控制信号被拉低至第四电平,输出所述第三电平,其中,所述第四电平低于所述反馈电路与所述控制电路的第一导通电压:在所述带隙基准电路启动之后的第一时间段内,所述第一控制信号无法达到所述目标输出电压;或者在所述第一控制信号达到所述目标输出电压之后的第二时间段内,所述第一控制信号无法维持在所述目标输出电压,相应地,所述控制电路还用于,响应于所述第二控制信号维持在所述第四电平并且所述反馈电路输出的所述第三电平,重新输出所述启动电压。

10、优选地,所述反馈电路还用于,在所述第二控制信号被拉高并维持在所述第一电平的情况下,响应于所述第一控制信号高于0且低于所述第二电平,重新输出所述第三电平。

11、通过上述技术方案,本发明创造性地通过反馈电路接收带隙基准电路的输出电压以作为第一控制信号,并在第二控制信号被拉高至第二电平并维持在第一电平的情况下,响应于所述第一控制信号高于0且低于第二电平,输出第三电平;通过控制电路响应于所述第二控制信号被拉高并维持在所述第一电平并且所述反馈电路输出的所述第三电平,控制用于所述带隙基准电路的启动电压降低,由此,本发明在向带隙基准电路提供启动电压之后,可将带隙基准电路的输出电压作为反馈来控制启动电路关闭,以降低启动电压,从而极大地提升了带隙基准电路的启动过程的可靠性。

12、本发明第二方面提供一种芯片,所述芯片包括:所述的用于带隙基准电路的启动电路。

13、有关本发明实施例提供的芯片的具体细节及益处可参阅上述针对用于带隙基准电路的启动电路的描述,于此不再赘述。

14、本发明的其它特征和优点将在随后的具体实施方式部分予以详细说明。

技术特征:

1.一种用于带隙基准电路的启动电路,其特征在于,所述启动电路包括:

2.根据权利要求1所述的启动电路,其特征在于,所述反馈电路还用于,在所述第二控制信号维持在第四电平的情况下,响应于所述第一控制信号为0,输出所述第三电平,其中,所述第四电平低于所述反馈电路与所述控制电路的第一导通电压,

3.根据权利要求1或2所述的启动电路,其特征在于,所述反馈电路包括:

4.根据权利要求3所述的启动电路,其特征在于,所述反馈电路还包括:

5.根据权利要求4所述的启动电路,其特征在于,所述反馈电路还包括:

6.根据权利要求3所述的启动电路,其特征在于,所述控制电路包括:

7.根据权利要求6所述的启动电路,其特征在于,所述启动电路还包括:

8.根据权利要求1所述的启动电路,其特征在于,所述反馈电路还用于,在所述第一控制信号满足以下异常条件的情况下,响应于所述第二控制信号被拉低至第四电平,输出所述第三电平,其中,所述第四电平低于所述反馈电路与所述控制电路的第一导通电压:

9.根据权利要求8所述的启动电路,其特征在于,所述反馈电路还用于,在所述第二控制信号被拉高并维持在所述第一电平的情况下,响应于所述第一控制信号高于0且低于所述第二电平,重新输出所述第三电平。

10.一种芯片,其特征在于,所述芯片包括:根据权利要求1-9中任一项所述的用于带隙基准电路的启动电路。

技术总结

本发明涉及集成电路技术领域,公开一种用于带隙基准电路的启动电路以及芯片。所述启动电路包括:反馈电路,用于执行以下操作:接收带隙基准电路的输出电压以作为第一控制信号;接收第二控制信号;以及在第二控制信号被拉高并维持在第一电平时,响应于第一控制信号高于0且低于第二电平,输出第三电平,以及控制电路,用于响应于第二控制信号被拉高并维持在第一电平并且反馈电路输出的所述第三电平,控制用于带隙基准电路的启动电压降低,其中,第一电平等于或高于反馈电路与控制电路的第一导通电压,第二电平低于带隙基准电路的目标输出电压,以及第三电平高于或等于控制电路的第二导通电压,本发明可极大地提升带隙基准电路的启动过程的可靠性。

技术研发人员:马媛,潘成,何帆,符艳军,付振,曹波

受保护的技术使用者:北京智芯微电子科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!