一种LDO的自适应零极点补偿电路及方法、芯片系统与流程

本发明涉及集成电路,尤其涉及cmos模拟集成电路设计领域,具体地,涉及一种低压差线性稳压器(low drop-out voltage regulator,简称ldo)的自适应零极点补偿电路及方法、芯片系统。

背景技术:

1、当前集成电路产业发展中,电源管理芯片起到极其重要的作用,它可以为系统其余电路给予稳定电压。低压差线性稳压器芯片的简称是ldo,属于电源管理芯片,其显著优点有:结构简单、响应快、输出噪声低、静态功耗低、电路规模小等,因而是数模混合芯片中几乎必备的关键电源模块。

2、ldo的工作原理是当输出的负载电流或输入的电源电压发生瞬态变化时,利用负反馈技术动态调节功率管的输出电流,从而输出稳定电压。

3、ldo作为一种负反馈系统,其设计不可避免的牵涉到了系统稳定性的分析,ldo的稳定性受最大输出电流、负载电容、无负载静态电流这三个变量影响,在三个变量变化时,ldo的稳定性也会改变,例如:

4、case 1、在负载电容较大、最大输出电流较小的情况下,ldo在轻载(负载电流较小)和重载(负载电流较大)下均具有良好的稳定性;

5、case 2、在负载电容较小、最大输出电流较大、无负载静态电流较大的情况下,ldo在轻载时具有良好的稳定性,但在重载下存在稳定性问题;

6、case 3、在负载电容较小、最大输出电流较小、无负载静态电流较小的情况下,ldo在重载时具有良好的稳定性,但在轻载时存在稳定性问题;

7、case 4、在负载电容较小、最大输出电流较大、无负载静态电流较小的情况下,ldo在轻载和重载时均存在稳定性问题。

8、如上所述,现有技术的ldo,例如在应用于上述case 2和case 4的情况时,其在重载下存在稳定性问题,限制了ldo的应用,因此本技术提供了一种ldo的自适应零极点补偿电路及方法、芯片系统,其能够解决该问题,以克服现有技术存在的问题,且改进之后的ldo具有较低的功耗和较小的电路面积,在具有良好功能的基础上保证了芯片的小型化。

技术实现思路

1、为了克服现有技术的不足,本技术提供了一种ldo的自适应零极点补偿电路及方法,本发明的技术方案如下:

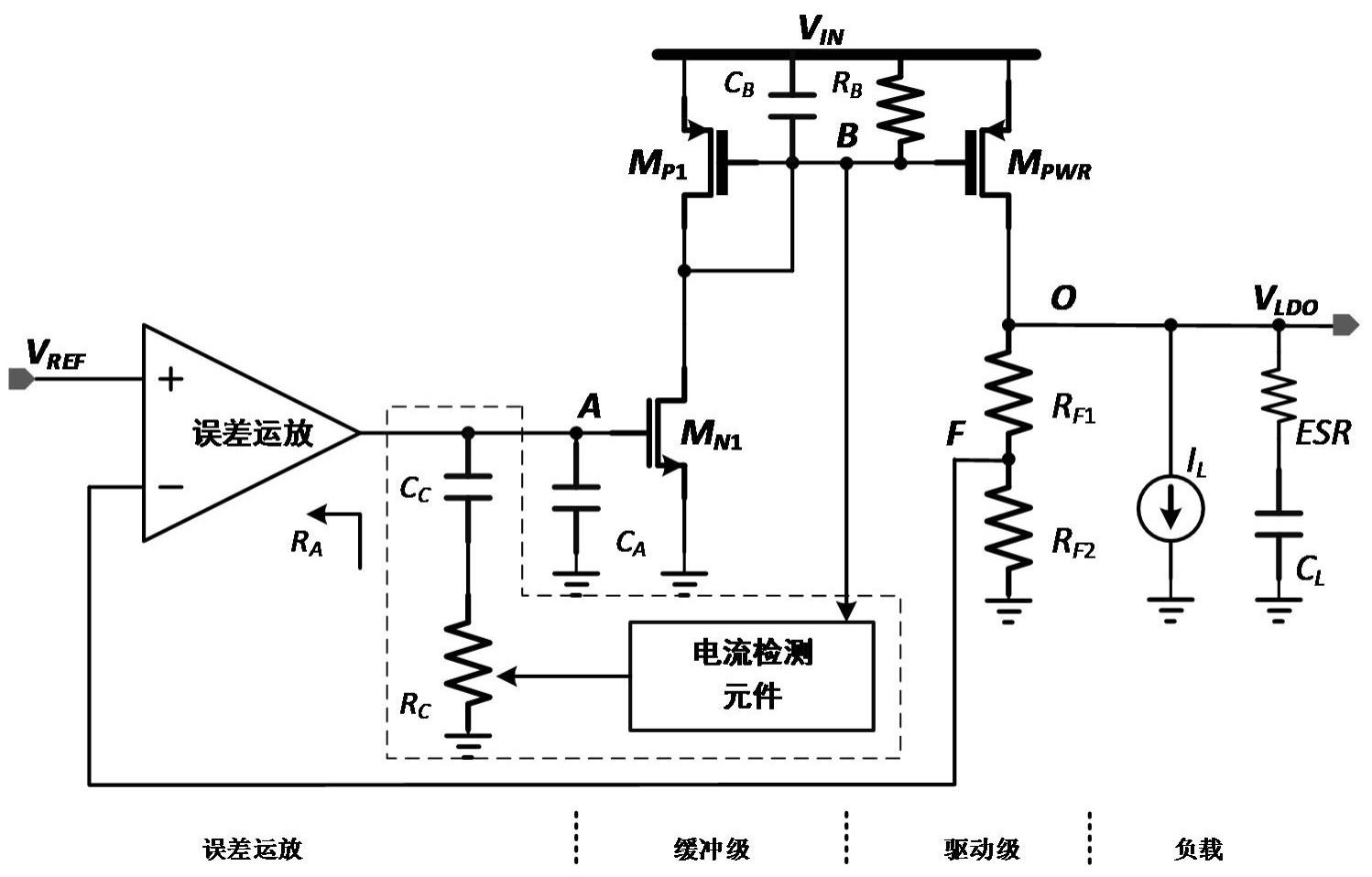

2、一种ldo的自适应零极点补偿电路,所述ldo包括误差运放、缓冲级、驱动级,所述误差运放的输出端与所述缓冲级的输入端之间具有一第一节点,所述驱动级包括输出功率管,所述ldo的自适应零极点补偿电路连接于所述第一节点与所述输出功率管的栅极之间;所述ldo的自适应零极点补偿电路包括pmos晶体管mp2、nmos晶体管mn2、nmos晶体管mn3和补偿电容;所述pmos晶体管mp2的栅极与所述输出功率管的栅极连接,所述pmos晶体管mp2的漏极与所述nmos晶体管mn2的漏极连接,所述nmos晶体管mn2的栅极与所述nmos晶体管mn3的栅极连接,所述nmos晶体管mn3的漏极连接所述补偿电容的一端,所述补偿电容的另一端连接所述第一节点;所述pmos晶体管mp2和nmos晶体管mn2用于检测流经所述输出功率管的输出电流的变化;工作于线性区的所述nmos晶体管mn3作为补偿电阻,其用于根据所述检测到的输出电流的变化来自适应调整其提供的补偿电阻的阻值,进而调整所述第一节点处的输出阻抗,并调整所述第一节点处提供的零极点的位置,从而提高ldo在重载下的稳定性。

3、所述pmos晶体管mp2将所述输出功率管的输出电流以预定的比例镜像输出给所述nmos晶体管mn2,通过所述nmos晶体管mn2将电流转换成电压信号,开启与所述nmos晶体管mn2栅极连接的nmos晶体管mn3;并通过工作在线性区的所述nmos晶体管mn3实现电压到电阻的转换。

4、所述第一节点处具有寄生电容,设置所述补偿电容,以使所述自适应零极点补偿电路引入额外的一对零极点和,,其中,是节点a处引入的主极点,是节点a处产生的零点,是节点a处产生的次极点,它们的大小可近似表示为:

5、,,,其中,为节点a处的等效输出阻抗,为补偿电阻。

6、选择、、以及的值,使得,且位于gbw内,以使ldo至少获得30度左右的相位裕度。

7、在轻载的情况下,所述补偿电容从所述第一节点中剥离,此时所述自适应零极点补偿电路不接入ldo电路中,不对轻载时ldo电路的稳定性产生影响。

8、所述误差运放包括:pmos晶体管mp11、pmos晶体管mp12、nmos晶体管mn11和nmos晶体管mn12,其中所述pmos晶体管mp11的栅极接基准电压vref,所述pmos晶体管mp11的漏极和所述nmos晶体管mn11的漏极连接,所述nmos晶体管mn11的源极接地;所述pmos晶体管mp11的源极与所述pmos晶体管mp12的源极连接且均连接至低压电源avdd,所述pmos晶体管mp12的漏极和所述nmos晶体管mn12的漏极连接,所述nmos晶体管mn12的源极接地,所述nmos晶体管mn12的栅极与所述nmos晶体管mn11的栅极连接,所述pmos晶体管mp12的栅极连接于ldo电路反馈点,所述pmos晶体管mp12的漏极和所述nmos晶体管mn12的漏极之间具有一第二节点,所述第二节点与所述第一节点连接;所述nmos晶体管mn12的栅极与所述nmos晶体管mn11的栅极之间具有一第三节点,所述pmos晶体管mp11的漏极和所述nmos晶体管mn11的漏极之间具有一第四节点,所述第三节点与所述第四节点连接。

9、所述缓冲级包括pmos晶体管mp1和nmos晶体管mn1;所述pmos晶体管mp1的源极连接输入电压vin,漏级连接所述nmos晶体管mn1的漏级,栅极连接所述输出功率管的栅极;所述nmos晶体管mn1的源极接地,栅极连接于所述第一节点。

10、所述驱动级还包括反馈电阻rf1和反馈电阻rf2;所述驱动级的输出功率管的源极连接所述输入电压vin,漏级连接所述反馈电阻rf1的一端,所述反馈电阻rf1的另一端连接所述反馈电阻rf2的一端,所述反馈电阻rf2的另一端接地;所述ldo电路反馈点设置于所述反馈电阻rf1和所述反馈电阻rf2之间。

11、一种ldo的自适应零极点补偿方法,采用如上任一所述的ldo的自适应零极点补偿电路来实现,所述方法包括:

12、检测流经ldo的输出功率管的输出电流;

13、根据所述检测到的输出电流的变化来自适应调整第一节点处的输出阻抗,进而调整所述第一节点处提供的零极点的位置。

14、一种芯片系统,所述芯片系统包括ldo,所述ldo包括如上任一所述的一种ldo的自适应零极点补偿电路;或所述ldo采用如上所述的任一种ldo的自适应零极点补偿方法来实现。

15、本技术提供的ldo的自适应零极点补偿电路功耗低、结构简单、能适用于不同的ldo电路、有利于实现芯片的小型化,且明显改善了重载下ldo电路的稳定性问题,同时也解决了现有技术中的一些补偿方式存在的设计过于复杂、适用性较弱、设计时间和成本增加的问题,本技术的其他有益效果可从具体实施例中得到。

- 还没有人留言评论。精彩留言会获得点赞!