一种高保真音频设备及其控制方法与流程

本发明涉及高保真音频,特别涉及一种高保真音频设备及其控制方法。

背景技术:

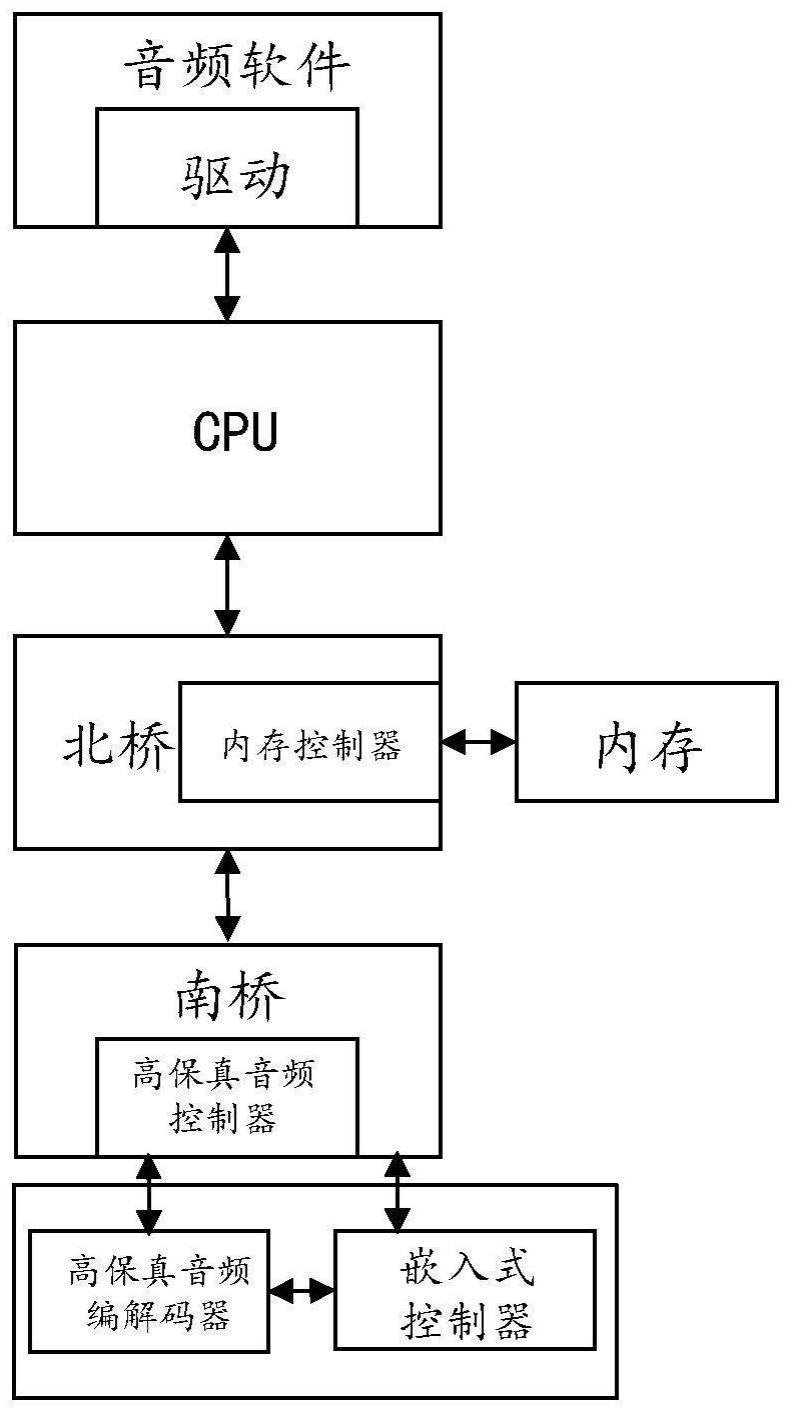

1、高保真音频(hda,high definition audio)是一种基于电脑(pc)平台的音频总线。图1示出当前pc平台中的hda设备架构示意图,如图1所示,计算机主板上通常包括cpu、北桥(mch,memory controller hub)以及南桥(ich,i/o controller hub)三个芯片,其中北桥芯片主要负责cpu与内存之间的数据交换,而南桥芯片主要是负责i/o接口等一些外设接口的控制、ide设备的控制及附加功能等。基于此,在现有的hda设备中,hda控制器设置于南桥芯片中,音频软件通过驱动与cpu进行通信,cpu通过北桥与所述hda控制器进行通信,所述hda控制器通过hda总线控制高保真音频编解码器(hda codec)芯片的音频流及采样参数等配置信息。

2、所述hda总线由总线时钟bclk、同步信号sync、放音数据sdo、录音数据sdi以及总线复位信号rst#这5根信号线组成,图2示出所述hda总线总各信号线的时序关系。如图2所示,总线时钟bclk在codec非休眠期间都会持续有效,以驱动所述codec正常工作。hda总线的帧频率为48khz,sdo/sdi在每帧的帧头sync开始时传输命令以及紧接着的音频数据流,当音频数据在本帧中传输完成但还未开始下一帧时,则需将后续数据补0。

3、可以看出,所述hda总线的效率不高,在实际工作时总线存在大量的空载期,但bclk却持续工作,带来不必要的功耗。目前的hda总线标准可在codec进入休眠后,将bclk时钟关闭,但若发生诸如耳机插拔状态改变时间时,则会唤醒所述codec,而所述codec则会进一步地主动唤醒整个hda总线。图3示出所述codec主动唤醒的时序示意图。如图3所示,虽然耳机插拔等事件并非与hda音频播放事件强相关,但唤醒后hda总线也会持续工作,带来额外功耗。此外,传统的hda codec芯片都为专用芯片,hda标准决定了hda codec需要一一映射外部音频设备,因此传统hda codec芯片需为不同的外设场景开发不同的codec芯片。若非定制的hda codec芯片,多数情况下会存在hda codec通道冗余的情况,即实际工作时这些通道不会用到但依然会持续被总线时钟bclk持续驱动,导致额外的功耗。

4、针对hda功耗较高等缺点,有研究提出了一种新的音频总线soundwire,其可适用于移动和pc行业的音频接口。相较而言,其比hda功耗更低,总线时钟和帧配置更灵活,但其总线协议比hda更复杂,因此暂难以广泛应用于pc平台中。

技术实现思路

1、针对现有技术中的部分或全部问题,为了在高保真音频(hda,high definitionaudio)总线标准基础上降低编解码器的整体功耗,本发明第一方面提出一种高保真音频设备,其将编解码器codec与嵌入式控制器(ec,embed controller)集成在一起,所述编解码器与所述嵌入式控制器可通信地连接。

2、进一步地,所述嵌入式控制器包括:

3、通信总线,包括精简引脚总线(lpc,low pin count bus)、和/或增强型串行外设接口(espi,enhanced serial peripheral interface),其用于将低速外设信息传递至cpu;

4、处理器模块,其用于控制通信总线及外设;

5、存储器,其用于存储数据、和/或程序;

6、至少一个外设,所述至少一个外设通过片内总线与所述通信总线、处理器模块以及存储器可通信地连接。

7、进一步地,所述片内总线包括高级处理器总线架构(amba,advancedmicrocontroller bus architecture)中的高级高性能总线(ahb,advanced highperformance bus)或高级外围总线(apb,advanced peripheral bus)。

8、进一步地,所述编解码器包括hda总线时钟门控模块,所述hda总线时钟门控模块用于控制所述编解码器内部的时钟,包括:

9、在空载期间关闭所述编解码器内部的时钟。

10、进一步地,所述编解码器被配置为嵌入式控制器的一个外设,与所述通信总线、处理器模块以及存储器集成在同一晶粒上,所述编解码器通过高级处理器总线架构与所述嵌入式控制器的通信总线、处理器模块以及存储器可通信地连接。

11、进一步地,所述编解码器及嵌入式控制器均为独立的晶粒,所述编解码器与嵌入式控制器集成于同一芯片中,所述编解码器通过直接可控制线与所述嵌入式控制器可通信地连接。

12、进一步地,所述高保真音频设备还包括控制器,所述控制器设置于南桥芯片中,所述南桥芯片通过精简引脚总线(lpc,low pin count bus)、和/或增强型串行外设接口(espi,enhanced serial peripheral interface)与所述嵌入式控制器可通信地连接。

13、本发明第二方面提供一种如前所述的高保真音频设备的控制方法,包括:

14、通过嵌入式控制器检测所述编解码器中的唤醒事件,并上报至驱动模块;以及

15、所述驱动模块对所述唤醒事件进行处理,以确定是否唤醒所述编解码器。

16、进一步地,所述控制方法还包括:

17、通过所述编解码器根据采样参数确定每帧中有效负载时长;以及

18、在空载期主动关闭所述编解码器内部的总线时钟。

19、本发明提供的一种高保真音频设备及其控制方法,通过将嵌入式控制器与hda编解码器集成于一体,仅需一颗芯片即可实现嵌入式控制器及编解码器功能,有效减少了系统级bom成本,节省了pcb空间。所述hda编解码器可直接与所述嵌入式控制器通信,利用嵌入式控制器长期工作的特点对hda编解码器中的唤醒事件进行检测及上报,还可以减少hda编解码器的不必要的唤醒,从而减少系统级功耗。此外,所述设备中的hda编解码器可根据采样参数确定每帧中有效负载时长,在空载期在hda编解码器内部主动关闭总线时钟,从而进一步地减少hda编解码器整体功耗。

技术特征:

1.一种高保真音频设备,其特征在于,将编解码器与嵌入式控制器集成在一起,所述编解码器与所述嵌入式控制器可通信地连接。

2.如权利要求1所述的高保真音频设备,其特征在于,所述嵌入式控制器包括:

3.如权利要求2所述的高保真音频设备,其特征在于,所述少一个外设通过高级处理器总线架构中的高级高性能总线或高级外围总线与所述通信总线、处理器模块以及存储器可通信地连接。

4.如权利要求1所述的高保真音频设备,其特征在于,所述编解码器包括高保真音频总线时钟门控模块,所述高保真音频总线时钟门控模块被配置为控制所述编解码器内部的时钟,包括:

5.如权利要求2所述的高保真音频设备,其特征在于,所述编解码器被配置为嵌入式控制器的一个外设,与所述通信总线、处理器模块以及存储器集成在同一晶粒上,所述编解码器通过高级处理器总线架构与所述嵌入式控制器的通信总线、处理器模块以及存储器可通信地连接。

6.如权利要求2所述的高保真音频设备,其特征在于,所述编解码器及嵌入式控制器均为独立的晶粒,所述编解码器与嵌入式控制器集成于同一芯片中,所述编解码器通过直接可控制线与所述嵌入式控制器可通信地连接。

7.如权利要求1所述的高保真音频设备,其特征在于,还包括控制器,所述控制器设置于南桥芯片中,所述南桥芯片通过精简引脚总线和/或增强型串行外设接口与所述嵌入式控制器可通信地连接。

8.一种如权利要求1至7任一所述的高保真音频设备的控制方法,其特征在于,包括步骤:

9.如权利要求8所述的控制方法,其特征在于,还包括步骤:

技术总结

本发明公开一种高保真音频设备,其将编解码器与嵌入式控制器集成在一起,且编解码器与嵌入式控制器可通信地连接。通过将嵌入式控制器与HDA编解码器集成于一体,可以有效减少系统级BOM成本,节省PCB空间。同时利用嵌入式控制器长期工作的特点对HDA编解码器中的唤醒事件进行检测及上报,还可以减少HDA编解码器的不必要的唤醒,从而减少系统级功耗。

技术研发人员:吴键,曹国梁

受保护的技术使用者:华大半导体(成都)有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!