一种抑制电压下冲的低压差线性稳压器电路的制作方法

本发明涉及低压差线性稳压器电路设计,尤其涉及一种抑制电压下冲的低压差线性稳压器电路。

背景技术:

1、目前,低压差线性稳压器ldo被广泛应用于电源管理电路中,是电子设备或具有电源管理功能的芯片中不可或缺的一部分。ldo设计中比较困难的挑战之一是瞬态响应的问题,在芯片工作过程中,可能会有瞬间的工作大电流产生,这种瞬间大电流会使ldo输出产生下冲问题。

2、现有技术主要是依靠ldo驱动管调节提供所需输出的电流,当瞬间工作大电流产生时,需要调整管的栅极电压迅速下降,以满足所需负载电流,但是由于调整管栅极电压无法迅速响应,会使得ldo输出电压产生下冲现象,而当ldo电压下降到一定程度时,可能会导致整个芯片不能正常工作,因此如何有效缓解电压下冲是一个亟需解决的问题。

技术实现思路

1、本发明的目的是提供一种抑制电压下冲的低压差线性稳压器电路,该电路针对现有电路结构所存在的电压下冲问题,通过加速调整管栅压放电,从而有效缓解电压下冲,提高低压差线性稳压器ldo的性能。

2、本发明的目的是通过以下技术方案实现的:

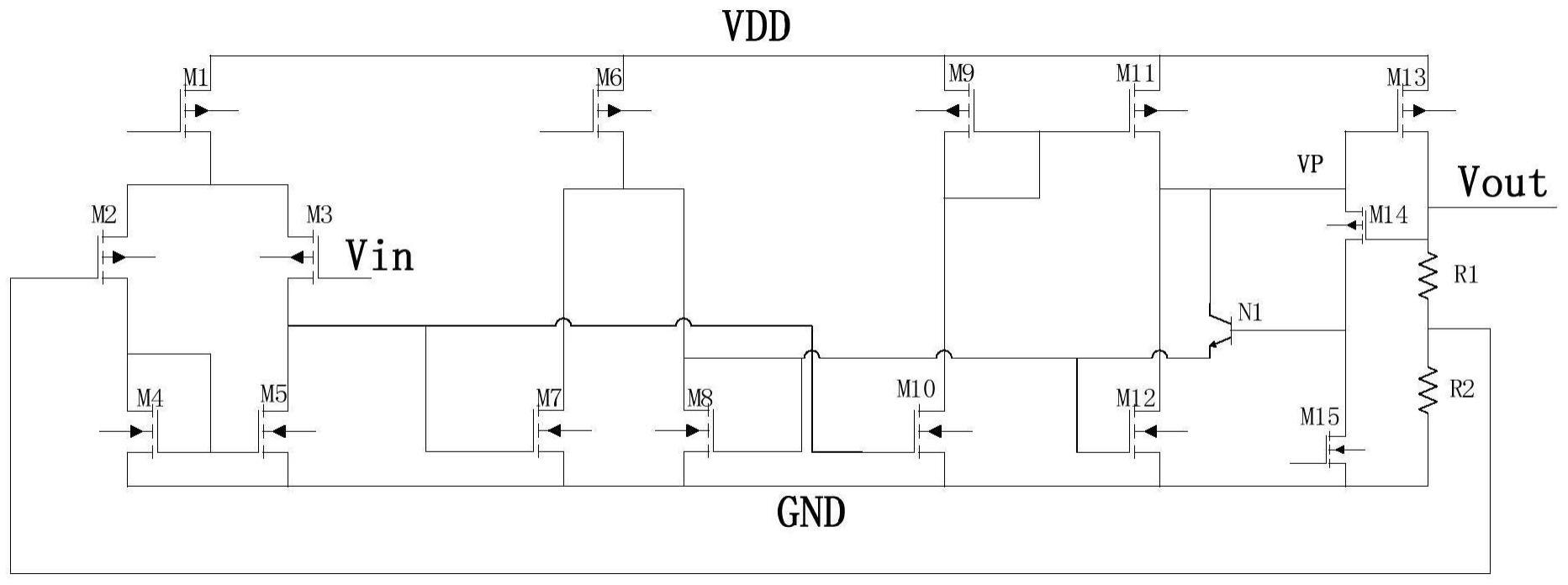

3、一种抑制电压下冲的低压差线性稳压器电路,所述电路包括15个mosfet晶体管,分别命名为m1~m15;一个放电三极管,命名为n1;两个电阻,命名为r1和r2,其中:

4、晶体管m1的栅极接电流偏置电压,源极接电源,漏极接晶体管m2和m3源极,衬底接电源;

5、晶体管m2的栅极接电阻r1和r2的反馈电压,源极接m1漏极,漏极接晶体管m4和m5的栅极,衬底接电源;

6、晶体管m3的栅极接输入电压vin,源极接晶体管m1漏极,漏极接晶体管m5漏极,衬底接地;

7、晶体管m4的栅极和漏极接晶体管m2漏极,源极和衬底接地;

8、晶体管m5的栅极接晶体管m2漏极和晶体管m4栅极,漏极接晶体管m3漏极,衬底和源极接地;

9、晶体管m6的栅极接电流偏置电压,源极接电源,漏极接晶体管m7和m8漏极,衬底接电源;

10、晶体管m7的栅极接晶体管m3和m5漏极,漏极接晶体管m6漏极,源极和衬底接地;

11、晶体管m8的栅极和漏极接晶体管m6漏极,源极和衬底接地;

12、晶体管m9的栅极和漏极接晶体管m10漏极,源极和衬底接电源;

13、晶体管m10的栅极接晶体管m3和m5漏极,漏极接晶体管m9漏极和栅极,源极和衬底接地;

14、晶体管m11的栅极接晶体管m9栅极,源极和衬底接电源,漏极接晶体管m12漏极;

15、晶体管m12的栅极接晶体管m6和m8漏极,漏极接晶体管m11漏极,源极和衬底接地;

16、晶体管m13的栅极接晶体管m11和m12漏极,源极和衬底接电源,漏极接输出电压vout;

17、晶体管m14的栅极接输出电压vout,源极接晶体管m13漏极,漏极接晶体管m15漏极,衬底接电源;

18、晶体管m15的栅极接电流偏置电压,漏极接晶体管m14漏极,源极和衬底接地;

19、放电三极管n1的n端接晶体管m13栅极,p端接晶体管m14和m15漏极,另一个n端接晶体管m6和m8漏极;

20、电阻r1的一端接输出电压vout,另一端接电阻r2;电阻r2的一端接输出电压vout,另一端接电阻r1;

21、m1~m5这五个晶体管组成运放电路,m1为电流偏置管,用于提供正常工作时所需要的工作电流;m2和m3是输入管,m2为输入负极,m3为输入正极;m4和m5为负载管;

22、晶体管m6~m8组成跨导增强电路gmboost,m6提供跨导增强电路所需工作电流;m7和m8为电流调整管,分别为m10和m12提供偏置电流;

23、晶体管m9~m12组成classab结构,m9和m10为电流偏置管,用于为m11提供偏置电流;m11和m12负责调节vp点电压,该vp点电压为晶体管m13的栅极电压,用于动态调整输出电流;其中,所述classab结构为甲乙类放大器,同时驱动m11和m12来稳定输出电压;

24、晶体管m13和电阻r1、r2组成电流调整电路和反馈电阻网;其中,晶体管m13为输出功率管,负责调整输出电流;电阻r1和r2通过分压得到反馈电压,接入系统负极输入;

25、晶体管m14、m15和放电三极管n1组成放电电路,晶体管m14作为电流监测管,时刻监测电流变化;晶体管m15作为电流偏置管,用于提供固定电流,当输出电压vout过低时,晶体管m14会导通,放电三极管n1会导通,迅速下拉晶体管m13的栅极电压,从而满足所需电流;

26、放电三极管n1用于加速电流泄放。

27、由上述本发明提供的技术方案可以看出,上述电路针对现有电路结构所存在的电压下冲问题,通过加速调整管栅压放电,从而有效缓解电压下冲,提高低压差线性稳压器ldo的性能。

技术特征:

1.一种抑制电压下冲的低压差线性稳压器电路,其特征在于,所述电路包括15个mosfet晶体管,分别命名为m1~m15;一个放电三极管,命名为n1;两个电阻,命名为r1和r2,其中:

2.根据权利要求1所述抑制电压下冲的低压差线性稳压器电路,其特征在于,基于所述电路结构:

技术总结

本发明公开了一种抑制电压下冲的低压差线性稳压器电路,包括15个MOSFET晶体管以及一个放电三极管,M1~M5这五个晶体管组成五管运放电路,M1为电流偏置管;M6~M8组成gmboost电路;M7和M8为电流调整管,分别为M10和M12提供偏置电流;M9~M12组成classAB结构;M13和电阻R1、R2组成电流调整电路和反馈电阻网;M14、M15和放电三极管N1组成放电电路,M14作为电流监测管;M15作为电流偏置管;放电三极管N1用于加速电流泄放。上述电路针对现有电路结构所存在的电压下冲问题,通过加速调整管栅压放电,从而有效缓解电压下冲,提高低压差线性稳压器LDO的性能。

技术研发人员:刘小涵,马建斌

受保护的技术使用者:豪威科技(北京)股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!