基于ARM和FPGA的二维转台伺服控制器及总线通信方法与流程

本发明涉及伺服控制,特别是一种基于arm和fpga的二维转台伺服控制器及总线通信方法。

背景技术:

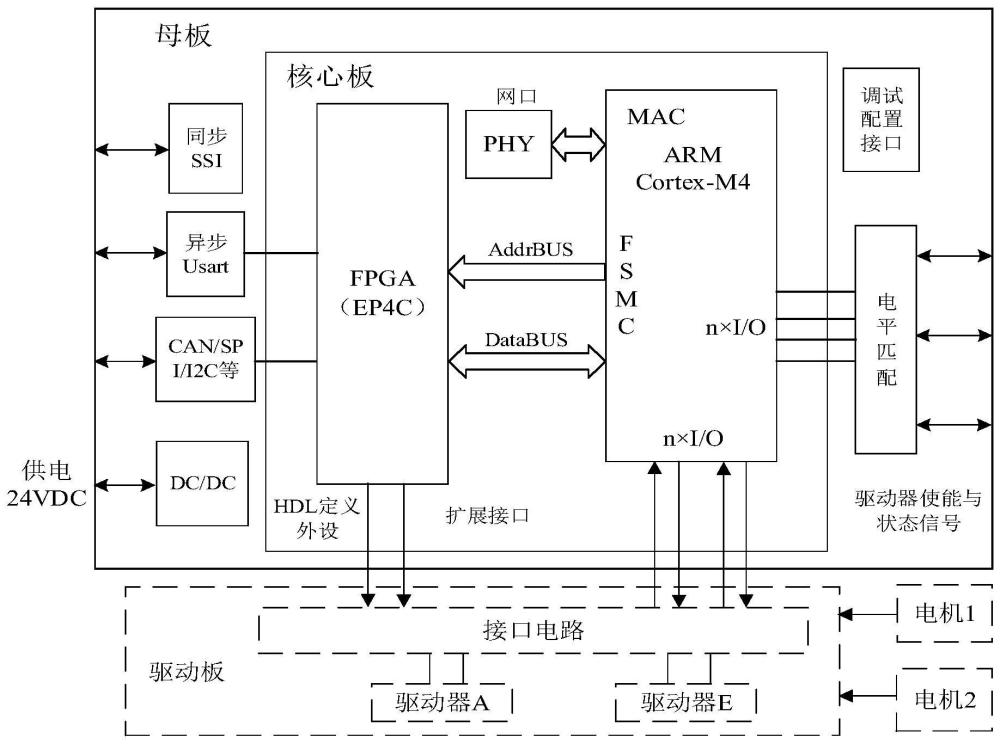

1、转台是一种集成的机电一体化系统,其涵盖机电、传感器、信息处理与控制技术,广泛应用于工业和军事领域,用于驱动和控制负载设备实现各种轴向转动或线性运动,搭载不同的功能负载,实现不同的系统功能。根据运动轴数有单轴/一维转台、两轴/二维转台、以及三轴、多轴转台等;根据应用场合或搭载的负载不同,广泛应用于:雷达天线转台、光电探测与跟踪设备、卫星天线地面站伺服控制等,以雷达天线两轴转台为例,其基本的系统组成如图1所示。

2、转台框架结构基本组成,包括:天线负载、两轴框架结构(含驱动电机、传动机构、测角、测速、测向等反馈器件)、转台控制器、电源模块等。转台控制器是其中最为核心的组成部分,是系统的通信单元、数据处理单元和控制调度单元,其接收上位机指令、采集各种传感器信息、控制和驱动电机,执行特定的运动控制功能,决定着系统功能和性能指标的实现。

3、经调研和查阅资料,发现现在常用的转台伺服控制器具有以下的局限:

4、1)硬件架构设计不够灵活:采用plc、dsp、arm处理器等单cpu架构,其外设资源有限、难以满足相对复杂的多任务系统需求;采用cpu+fpga处理器架构,针对不同的应用需求,兼容性、裁剪性、扩展性不好;

5、2)现有cpu+fpga处理器架构设计,cpu与fpga处理器双向总线数据通信不够灵活,尤其在通信数据量大、数据时序同步要求高时,现有的设计方案,很难实现复杂的双向通信实时响应,而且在系统调试过程中,一旦设计要求或通信协议发生更改,需要arm处理器和fpga处理器两边同时进行调整,增加了系统调试难度和编程工作量。

技术实现思路

1、鉴于此,本发明提供一种基于arm和fpga的二维转台伺服控制器及总线通信方法。

2、本发明公开了一种基于arm和fpga的二维转台伺服控制器,其包括:

3、采用核心板和母板的层叠式结构,核心板集成arm处理器和fpga处理器及外围电路,母板包括多路扩展接口;核心板和母板组合用于功能和外设需求相对复杂的系统,而核心板也可单独使用,满足相对简单的系统设计要求;arm处理器和fpga处理器通过可拆卸方式引出到母板,根据实际需求,在母板上进行扩展或裁减。

4、进一步地,所述核心板中的arm处理器和fpga处理器通过并行总线双向通信;fpga处理器用于外设接口扩展和数据采集,而arm处理器用于复杂控制算法和系统工作流程调度。

5、进一步地,arm处理器主要用于负责各种数据运算、算法实现、过程逻辑控制、事件处理、及对外接口,利用其标准外设资源和运算处理单元作为系统算法控制核心;

6、fpga处理器具有功能可定制的硬件io资源、逻辑处理单元,实现时序设计、高速信号处理,扩展多种功能的定制外设接口,以满足系统接口扩展、逻辑和时序控制的设计要求,用于多种传感器数据采集,并对数据进行预处理。

7、进一步地,核心板和母板之间采用双列插针和插座连接,其中,核心板用于负责大量数据运算处理,母板用于实现各种对外电气接口;

8、核心板的资源外设通过排针引出到母板/底板;母板上集成各种对外的通讯和传感器接口电路。

9、本发明还公开了一种适用于上述任一项所述的基于arm和fpga的二维转台伺服控制器的总线通信方法,所述总线通信方法包括:

10、步骤1:在链路层,arm处理器与fpga处理器之间通过可变静态存储控制器实现高速并行双向总线通信,以实现fpga处理器同时采集多路低速外设传感器信号,通过宽带的并行总线上报给arm处理器;

11、步骤2:针对arm处理器与fpga处理器之间通信的协议层,设计透明传输机制。

12、进一步地,所述步骤2包括:

13、在通信过程中,将一帧数据内容或字节序列划分为多个2字节一组的单元,若帧字节长度为奇数,则最后增加0xff补齐,数据字节序列按照先高字节、后低字节顺序;在arm处理器端读取fpga处理器数据时,arm处理器通过固定地址发送一个数据访问识别码,定义将要访问的数据类别和数据单元长度;fpga处理器根据该访问识别码,向arm处理器依次上报对应的数据内容。

14、进一步地,arm处理器和fpga处理器之间的数据传输通信过程包括:

15、当由arm处理器向fpga处理器通信时,在arm端通过固定地址下发通信数据类别+数据帧长度+数据编码,在fpga端根据约定的通用协议接收并解析对应数据;

16、当由fpga处理器向arm处理器通信时,在arm端根据地址和数据类别编码、数据单元长度,按照约定的通用协议接收并解析对应数据。

17、进一步地,根据不同传感器的帧协议,在arm处理器中进行数据组合还原。

18、由于采用了上述技术方案,本发明具有如下的优点:

19、1.选择stm32f4系列arm处理器和altera ep4c系列fpga处理器芯片,组成双核心处理器;

20、2.双核之间的通信,在链路层采用标准的fsmc(flexible static memorycontroller,可变静态存储控制器)总线,在应用层,设计了一种专门的通讯机制,可实现大量数据的透明传输,简化了应用编程的难度和工作量,可极大的调高系统开发效率;

21、3.控制器结构,采用标准化核心板+可定制化母板的层叠式结构设计,具有设计灵活、扩展性好的特点,已在多个工程项目中得到应用验证。

技术特征:

1.一种基于arm和fpga的二维转台伺服控制器,其特征在于,包括:

2.根据权利要求1所述的基于arm和fpga的二维转台伺服控制器,其特征在于,所述核心板中的arm处理器和fpga处理器通过并行总线双向通信;fpga处理器用于外设接口扩展和数据采集,而arm处理器用于复杂控制算法和系统工作流程调度。

3.根据权利要求1所述的基于arm和fpga的二维转台伺服控制器,其特征在于,arm处理器主要用于负责各种数据运算、算法实现、过程逻辑控制、事件处理、及对外接口,利用其标准外设资源和运算处理单元作为系统算法控制核心;

4.根据权利要求1所述的基于arm和fpga的二维转台伺服控制器,其特征在于,核心板和母板之间采用双列插针和插座连接,其中,核心板用于负责大量数据运算处理,母板用于实现各种对外电气接口;

5.一种适用于权利要求1-4任一项所述的基于arm和fpga的二维转台伺服控制器的总线通信方法,其特征在于,所述总线通信方法包括:

6.根据权利要求5所述的总线通信方法,其特征在于,所述步骤2包括:

7.根据权利要求6所述的总线通信方法,其特征在于,arm处理器和fpga处理器之间的数据传输通信过程包括:

8.根据权利要求7所述的总线通信方法,其特征在于,根据不同传感器的帧协议,在arm处理器中进行数据组合还原。

技术总结

本发明公开了一种基于ARM和FPGA的二维转台伺服控制器及总线通信方法,该伺服控制器采用核心板和母板的层叠式结构,核心板集成ARM处理器和FPGA处理器及外围电路,母板包括多路扩展接口;核心板和母板组合用于功能和外设需求相对复杂的系统,而核心板也可单独使用,满足相对简单的系统设计要求;ARM处理器和FPGA处理器通过可拆卸方式引出到母板,根据实际需求,在母板上进行扩展或裁减。本发明以ARM为高速运算单元,以FPGA为接口扩展单元,提出和采用了ARM与FPGA之间数据透明总线传输的通信机制,数据通信和处理灵活高效,系统外设资源丰富、可扩展性强、集成度高、硬件功能可配置、性价比高,非常适合于二维\多轴复杂转台控制系统应用。

技术研发人员:薛辉,何华卫,冯强,陈正川,贾仕杰

受保护的技术使用者:四川九洲电器集团有限责任公司

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!