复用引脚修调芯片电学参数的电路的制作方法

本发明涉及集成电路,更具体地涉及一种复用引脚修调芯片电学参数的电路。

背景技术:

1、为了获得更精确的电学参数,在芯片的电路设计时往往加入修调电路对芯片进行修调。不同的修调方案,会影响芯片的生产成本及测试效率。

2、如图1所示为现有的使用i2c进行修调的电路示意图。降压芯片111具有6个端口in、out、gnd、en、scl和sda,其中in端口连接到输入电容102的正极以及输入电源103的正极,out端连接到输出电容105的正极以及输出负载104的一端,gnd端连接到地,en端(使能端)、scl端(时钟线)、sda端(双向数据线)连接到微控制器107的输出端;输出电容102的负极、输入电源103的负极、输出电容105的负极以及输出负载104的另一端均接到地。现有的修调电路通过i2c读写码的方式,把编码写入i2c解码模块203,并从该模块读寄存器数据,与写入数据对比,判断写入的正确性,i2c解码模块203根据写入的编码对应修调线性降压模块202中的下侧比例电阻405、基准产生电压401、上侧比例电阻406以及限流模块403的电学参数,使之得到不同的输出端out的电压及电流参数,实现不同的输出规格以及保持同一规格输出的一致性。

3、但是,现有的修调电路需要通过en端、scl端和sda端三个引脚加入信号才能读写芯片数据,测试时需占用较多的引脚,增加了生产及测试成本。

技术实现思路

1、本发明的目的在于提供一种复用引脚修调芯片电学参数的电路,通过复用使能引脚en,在使能引脚加上不同的电压及脉冲信号,实现编码验证及写入功能,以修调芯片电学参数,其节省了两个引脚,因此可减少生成及测试成本。

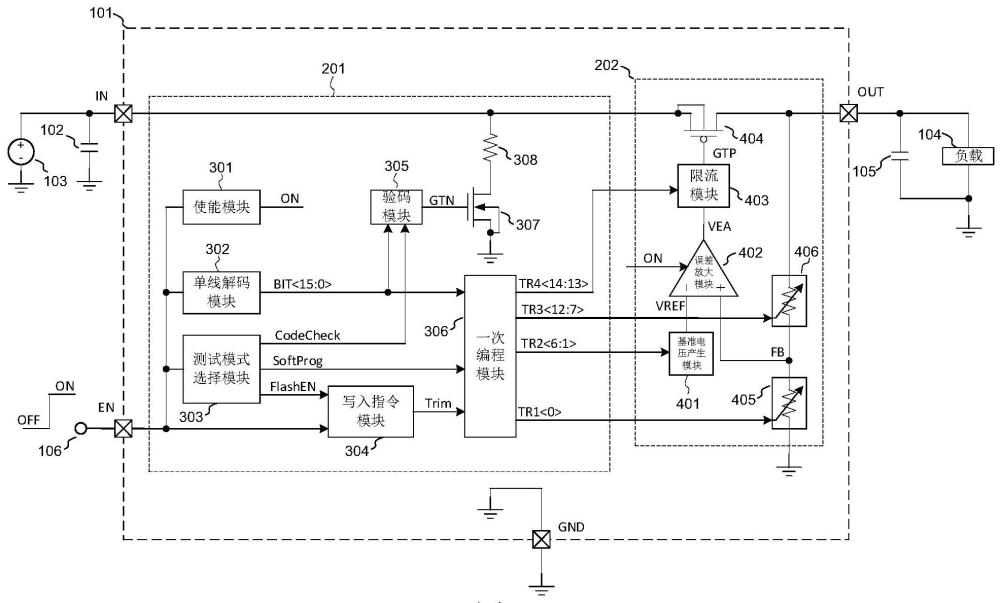

2、基于上述目的,本发明提供一种复用引脚修调芯片电学参数的电路,包括降压芯片、输入电容、输入电源、负载、输出电容和控制端,所述降压芯片包括修调码产生模块、线性降压模块、输入端、输出端、接地端和使能端,所述降压芯片的输入端连接到输入电容的正极和所述输入电源的正极,所述降压芯片的输出端连接到输出电容的正极和负载的一端,接地端连接到地;降压芯片的使能端连接到所述控制端,所述控制端用于向所述降压芯片的使能端发送使能控制信号;所述输入电源的负极、所述输入电容的负极、所述输出电容的负极和所述负载的另一端均连接到地。

3、进一步地,所述修调码产生模块包括使能模块、单线解码模块、测试模式选择模块、写入指令模块、验码模块、一次编程模块、验码nmos管和验码电阻,所述使能模块的输入端、所述测试模式选择模块的输入端、所述单线解码模块的输入端和所述写入指令模块的第二输入端均与所述降压芯片的使能端相连,所述使能模块的输出端与所述线性降压模块相连;所述单线解码模块的输出端分别与所述验码模块的第一输入端和所述一次编程模块的第一输入端相连;所述测试模式选择模块的第一输出端与所述验码模块的第二输入端相连;所述测试模式选择模块的第二输出端与所述一次编程模块的第二输入端相连,所述测试模式选择模块的第三输入端与所述写入指令模块的第一输入端相连;所述写入指令模块的输出端与所述一次编程模块的第三输入端相连;所述一次编程模块具有四个分别与所述线性降压模块相连的输出端;所述验码nmos管的源极和衬底均连接到地,所述验码nmos管的漏极与所述验码电阻的一端相连,所述验码电阻的另一端与所述降压芯片的输入端相连。

4、进一步地,所述线性降压模块包括基准电压产生模块、误差放大模块、限流模块、降压pmos管、下侧比例电阻和上侧比例电阻,其中,基准电压产生模块的输入端与一次编程模块的第二输出端相连,基准电压产生模块的输出端与误差放大模块的反相输入端相连;上侧比例电阻的第一端连接到输出端,第二端连接到下侧比例电阻的第一端,下侧比例电阻的第二端连接到地;误差放大模块的同相输入端分别与上侧比例电阻的第二端和下侧比例电阻的第一端相连;误差放大模块的使能输入端与使能模块的输出端相连;误差放大模块的输出端与限流模块的输入端相连;限流模块的输出端与降压pmos管的栅极相连;降压pmos管的源极及衬底连接到降压芯片的输入端,降压pmos管的漏极连接到降压芯片的输出端。

5、进一步地,所述测试选择模块包括输入检测nmos管、第一电流源、第一施密特触发器、第一d触发器、第二d触发器、第一二与门、第二二与门和第三二与门,输入检测nmos管的源极连接到使能端,输入检测nmos管的栅极和衬底连接到地,输入检测nmos管的漏极连接到第一电流源的负极和第一施密特触发器的输入端,第一电流源的正极连接到降压芯片的输入端,第一施密特触发器的输出端连接到第一d触发器的clk端,第一d触发器的q端分别与第一二与门的第二输入端和第三二与门的第二输入端相连;第一d触发器的d端与第一d触发器的qn端相连并形成第一节点,第一节点分别与第二d触发器的clk端和第二二与门的第二输入端相连;第二d触发器的q端分别与第二二与门的第一输入端和第三二与门的第一输入端相连;第二d触发器的d端与第二d触发器的qn端相互连接并形成第二节点,第二节点与第一二与门的第一输入端相连;第一二与门的输出端形成为测试模式选择模块的第一输出端;第二二与门的输出端形成为测试模式选择模块的第二输出端;第三二与门的输出端形成为测试模式选择模块的第三输出端。

6、进一步地,单线解码模块可包括第一反相器、第一下拉nmos管、第二电流源、脉宽电容、比较器、第三d触发器至第十八d触发器,第一反相器的输入端与使能端相连,第一反相器的输出端分别与下拉nmos管的栅极和第三d触发器至第十八d触发器的clk端相连;第一下拉nmos管的漏极分别与第二电流源的负极、脉宽电容的正极和比较器的正向输入端相连;第一下拉nmos管的源极连接到地;第二电流源的正极连接到降压芯片的输入端;脉冲电容的负极连接到地;比较器的负向输入端与内部基准电压相连;比较器的输出端与第三d触发器的d端相连;第三d触发器至第十八d触发器依次排列,且针对第四d触发器至第十七d触发器中的任意一个,该d触发器的d端与该d触发器的前一个d触发器的q端相连,该d触发器的q端与后一个d触发器的d端相连;第三d触发器至十八d触发器的所有q端形成为单线解码模块的输出端。

7、进一步地,所述写入指令模块包括输入pmos管、第三电流源、第二施密特触发器、第二反相器、消抖滤波器和第四二与门,其中,输入pmos管的源极和衬底连接到使能端,输入pmos管的栅极连接到降压芯片的输入端,输入pmos管的漏极分别与第三电流源的正极和第二施密特触发器的输入端相连,第三电流源的负极连接到地,第二施密特触发器的输出端连接到第二反相器的输入端相连,第二反相器的输出端连接到消抖滤波器的输入端,消抖滤波器的输出端连接到第四二与门的第一输入端,第四二与门的第二输入端连接到测试模式选择模块的第三输出端,第四二与门的输出端形成为写入指令模块的输出端。

8、进一步地,使能模块包括第四电流源、第二下拉nmos管和第三施密特触发器,其中,第二下拉nmos管的栅极连接到使能端,第二下拉nmos管的源极和衬底连接到地,第二下拉nmos管的漏极分别连接到第四电流源的负极和第三施密特触发器的输入端,第三施密特触发器的输出端形成为使能模块的输出端。

9、进一步地,验码模块可包括第五二与门、第一四与门至第五四与门以及第三反相器至第十反相器,其中,第三反相器的输入端与第四d触发器的q端相连,第四反相器的输入端与第六d触发器的q端相连,第二四与门的第一输入端与第三d触发器的q端相连,第二四与门的第二输入端与第三反相器的输出端相连,第二四与门的第三输入端与第五d触发器的q端相连,第二四与门的第四输入端与第四反相器的输出端相连;第五反相器的输入端与第八d触发器的q端相连,第六反相器的输入端与第十d触发器的q端相连,第三四与门的第一输入端与第七d触发器的q端相连,第三四与门的第二输入端与第五反相器的输出端相连,第三四与门的第三输入端与第九d触发器的q端相连,第三四与门的第四输入端与第六反相器的输出端相连;第七反相器的输入端与第十一d触发器的q端相连,第八反相器的输入端与第十三d触发器的q端相连,第四四与门的第一输入端与第七反相器的输出端相连,第四四与门的第二输入端与第十二d触发器的q端相连,第四四与门的第三输入端与第八反相器的输出端相连,第四四与门的第四输入端与第十四d触发器的q端相连;第九反相器的输入端与第十五d触发器的q端相连,第十反相器的输入端与第十七d触发器的q端相连,第五四与门的第一输入端与第九反相器的输出端相连,第五四与门的第二输入端与第十六d触发器的q端相连,第五四与门的第三输入端与第十反相器的输出端相连,第五四与门的第四输入端与第十八d触发器的q端相连;第一四与门的第一输入端与第二四与门的输出端相连,第一四与门的第二输入端与第三四与门的输出端相连,第一四与门的第三输入端与第四四与门的输出端相连,第一四与门的第四输入端与第五四与门的输出端相连;第一四与门的输出端与第五二与门的第一输入端相连,第五二与门的第二输入端与测试模式选择模块的第一输出端相连,第五二与门的输出端形成为验码模块的输出端。

10、进一步地,一次编程模块包括依次排列的第一熔丝单元至第十六熔丝单元,其中第一熔丝单元至第十六熔丝单元的第一输入端均与写入指令模块的输出端相连;第一熔丝单元至第十六熔丝单元的第二输入端均与测试模式选择模块的第二输出端相连;第一熔丝单元的第三输入端与第三d触发器的q端相连;第一熔丝单元的输出端形成为一次编程模块的第四输出端;第二熔丝单元至第十六熔丝单元与第四d触发器至第十八d触发器一一对应,针对第二熔丝单元至第十六熔丝单元中的每一个,该熔丝单元的第三输入端分别与前一个熔丝单元的输出端和该熔丝单元对应的d触发器的q端相连。

11、进一步地,每个熔丝单元均包括第六二与门、电流nmos管、第五电流源、熔丝、第十一反相器和信号选择器,其中,第六二与门的第二输入端形成为熔丝单元的第一输入端;第六二与门的输出端与电流nmos管的栅极相连,电流nmos管的源极和衬底连接到地,电流nmos管的漏极、第五电流源的正极、第十一反相器的输入端和熔丝的一端相互连接;熔丝的另一端连接到降压芯片的输入端,第五电流源的负极连接到地,第十一反相器的输出端连接到信号选择器的第一输入端,信号选择器的第二输入端与第六二与门的第一输入端共同形成为熔丝单元的第三输入端;信号选择器的第三输入端形成为熔丝单元的第二输入端;信号选择器的输出端形成为熔丝单元的输出端。

12、本发明的复用引脚修调芯片电学参数的电路,通过复用使能引脚en,在en引脚上加入正、负不同电平及脉宽的信号,实现测试模式的选择、编码验证及写入功能;由于复用引脚en,可以使芯片节省两个测试修调引脚,使得测试外围简单高效,节省了外围元件的使用;同时也可以减少芯片的封装成本。

- 还没有人留言评论。精彩留言会获得点赞!