基于SPI协议的数据传输方法及其系统与流程

基于spi协议的数据传输方法及其系统

技术领域

[0001]

本发明涉及数据传输技术领域,更具体地涉及一基于spi协议的数据传输方法及其系统。

背景技术:

[0002]

在如今信息技术高速发展的时代,数据传输一直是信息技术发展的基石。目前,常见的传输协议主要包括i2c(inter-integrated circuit,集成电路总线)协议、spi(serial peripheral interface,串行外围设备接口)协议以及mipi(mobile industry processor interface,移动行业处理器接口)协议等等。例如,在诸如ar/vr的分体式眼镜方案中,基于slam定位的需求,通常会在hmd(head mount display,头戴式显示器)头戴侧设置imu(惯性测量单元)器件。由于现有的imu器件的接口多为spi接口,并且spi接口存在无法长距离传输的问题,因此现有的分体式ar/vr眼镜的hmd头戴侧与box盒子之间基本是通过fpga(fieldprogrammable gate array,现场可编程门阵列)进行上下行数据封装和传输。

[0003]

然而,对于采用spi接口的imu器件,由于spi协议时钟信号由spi主机产生,在读取数据过程中spi从机需要在该spi主机发送完寄存器地址信息后的下一个时钟周期就发送读取的数据,但是在分体式的设计方案中,该spi主机和该spi从机之间的信号需要通过fpga编码传输,这将产生信号时延,导致该spi主机无法及时读取到数据而出现数据错误。

[0004]

为了解决这个问题,现有的分体式ar/vr眼镜在采集hmd头戴侧的spi从机的数据时,通常会采用spi主机读取两次的方式。具体地,该spi主机在第一次读取操作时,box侧的fpga传输读取的寄存器地址和读取的长度到该hmd头戴侧,与此同时,该hmd头戴侧读取imu器件的数据并缓存;该spi主机在第二次读取操作时,该spi从机发送所缓存的数据,以完成数据的采集。这种两次读取的方式虽然能够在一定程度上解决数据出错的问题,但是会导致fpga侧传输带宽的浪费,并且在读取数据时会产生较大的时延,而该时延会根据读取的数据长度发生变化,对实时性要求较高的场景会产生特别大的不利影响。

技术实现要素:

[0005]

本发明的一目的在于提供一基于spi协议的数据传输方法及其系统,其能够缩短在通过fpga传输spi数据时引入的时延,有助于提升数据传输的实时性。

[0006]

本发明的另一目的在于提供一基于spi协议的数据传输方法及其系统,其中在本发明的一实施例中,所述基于spi协议的数据传输系统能够解决在通过fpga传输spi数据时引入的时延而导致的读取出错问题的同时,也能够充分利用fpga的传输带宽。

[0007]

本发明的另一目的在于提供一基于spi协议的数据传输方法及其系统,其中在本发明的一实施例中,所述基于spi协议的数据传输系统通过对spi协议的修改,配合fpga的处理逻辑,解决了spi数据读取问题。

[0008]

本发明的另一目的在于提供一基于spi协议的数据传输方法及其系统,其中在本

发明的一实施例中,所述基于spi协议的数据传输系统能够通过在原有正常时钟周期中插入读取时钟周期,用于fpga的上下行传输,有助于完成spi数据的读取,以防数据出错。

[0009]

本发明的另一目的在于提供一基于spi协议的数据传输方法及其系统,其中在本发明的一实施例中,所述基于spi协议的数据传输系统能够在spi主机发送完最后一比特数据到下一个时钟之间插入空隙,以便用于fpga的传输时间消耗。

[0010]

本发明的另一目的在于提供一基于spi协议的数据传输方法及其系统,其中在本发明的一实施例中,所述基于spi协议的数据传输系统能够采用在读取数据长度上增加预定数量字节,以增加时钟周期,有助于保证spi数据的完整读取。

[0011]

本发明的另一目的在于提供一基于spi协议的数据传输方法及其系统,其中在本发明的一实施例中,所述基于spi协议的数据传输系统能够从所述spi主机侧读取的数据的前端剔除掉所述预定数量字节的无效数据,有助于确保spi数据的准确。

[0012]

本发明的另一目的在于提供一基于spi协议的数据传输方法及其系统,其中在本发明的一实施例中,所述基于spi协议的数据传输系统能够在spi主机发送的寄存器地址前插入预定长度字节,使得从机侧fpga能够同时获得所述寄存器地址和所要读取的数据长度,有助于避免fpga传输带宽的浪费,并降低数据采集的时延。

[0013]

本发明的另一目的在于提供一基于spi协议的数据传输方法及其系统,其中在本发明的一实施例中,所述基于spi协议的数据传输系统仅需要对spi主机侧进行小的改动,有助于增强所述基于spi协议的数据传输系统的适应性。

[0014]

本发明的另一目的在于提供一基于spi协议的数据传输方法及其系统,其中为了达到上述目的,在本发明中不需要采用昂贵的材料或复杂的结构。因此,本发明成功和有效地提供一解决方案,不只提供一基于spi协议的数据传输方法及其系统,同时还增加了所述基于spi协议的数据传输方法及其系统的实用性和可靠性。

[0015]

为了实现上述至少一发明目的或其他目的和优点,本发明提供了一基于spi协议的数据传输方法,包括步骤:

[0016]

藉由一主机侧fpga,接收通过一spi主机读取的spi主机数据,其中所述spi主机数据携带有一具有第一预定数量字节的数据读取长度信息和一需要读取的寄存器地址信息;

[0017]

藉由一通讯链路,将所述spi主机数据从所述主机侧fpga传输至一从机侧fpga;

[0018]

藉由所述从机侧fpga,基于所述spi主机数据中的所述数据读取长度信息和所述寄存器地址信息,缓存通过一spi从机读取回的spi从机数据;以及

[0019]

藉由所述通讯链路,将所述spi从机数据从所述从机侧fpga传输至所述主机侧fpga,以回复给所述spi主机。

[0020]

在本发明的一些实施例中,在所述spi主机数据中,携带所述数据读取长度信息的字节位于携带所述寄存器地址信息的字节之前。

[0021]

在本发明的一些实施例中,所述藉由所述通讯链路,将所述spi从机数据从所述从机侧fpga传输至所述主机侧fpga,以回复给所述spi主机的步骤,包括步骤:

[0022]

藉由所述通讯链路,将一具有第二预定数量字节的无效数据和所述spi从机数据一起从所述从机侧fpga传输至所述主机侧fpga,以使所述spi主机读取从机侧数据;和

[0023]

藉由所述spi主机,从所读取的所述从机侧数据中剔除所述无效数据,以获得所述spi从机数据。

[0024]

在本发明的一些实施例中,与所述spi主机数据中的所述数据读取长度信息对应的时钟长度等于与所述无效数据对应的时钟长度和与所述spi从机数据对应的时钟长度之和。

[0025]

在本发明的一些实施例中,在通过所述spi主机读取的所述从机侧数据中,与所述无效数据对应的字节位于与所述spi从机数据对应的字节之前

[0026]

根据本发明的另一方面,本发明还提供了一基于spi协议的主机侧数据传输方法,包括步骤:

[0027]

藉由一主机侧fpga,接收并发送通过一spi主机读取的spi主机数据,其中所述spi主机数据携带有一具有第一预定数量字节的数据读取长度信息和一需要读取的寄存器地址信息;和

[0028]

藉由所述主机侧fpga,接收并发送一从机侧数据至所述spi主机。

[0029]

在本发明的一些实施例中,所述藉由所述主机侧fpga,接收并发送一从机侧数据至所述spi主机的步骤,包括步骤:

[0030]

藉由所述主机侧fpga,接收所述从机侧数据,其中所述从机侧数据包括一具有第二预定数量字节的无效数据和一spi从机数据;和

[0031]

藉由所述spi主机,从所述从机侧数据中剔除所述无效数据,以获得所述spi从机数据。

[0032]

根据本发明的另一方面,本发明还提供了一基于spi协议的从机侧数据传输方法,包括步骤:

[0033]

藉由一从机侧fpga,接收一spi主机数据,其中所述spi主机数据携带有一具有第一预定数量字节的数据读取长度信息和一需要读取的寄存器地址信息;

[0034]

藉由一spi从机,基于所述spi主机数据中的所述数据读取长度信息和所述寄存器地址信息,读取回的spi从机数据;以及

[0035]

藉由所述从机侧fpga,缓存读取的所述spi从机数据。

[0036]

在本发明的一些实施例中,所述的从机侧数据传输方法,进一步包括步骤:

[0037]

藉由所述从机侧fpga,发送一从机侧数据至一主机侧fpga,其中所述从机侧数据包括一具有第二预定数量字节的无效数据和所述spi从机数据。

[0038]

根据本发明的另一方面,本发明还提供了一基于spi协议的数据传输系统,包括:

[0039]

一主机侧单元;

[0040]

一从机侧单元;以及

[0041]

一传输单元,其中所述传输单元将所述主机侧单元与所述从机侧单元可通信地连接;

[0042]

其中所述主机侧单元包括相互可通信地连接的至少一spi主机和至少一主机侧fpga,其中所述spi主机用于读取一spi主机数据,其中所述spi主机数据携带有一具有第一预定数量字节的数据读取长度信息和一需要读取的寄存器地址信息;其中所述主机侧fpga用于接收所述spi主机数据,以通过所述传输单元传输至所述从机侧单元,并且接收并发送来自所述从机侧单元的一从机侧数据至所述spi主机。

[0043]

在本发明的一些实施例中,所述从机侧数据包括一具有第二预定数量字节的无效数据和一spi从机数据;其中所述spi主机进一步用于从所述从机侧数据中剔除所述无效数

据,以获得所述spi从机数据。

[0044]

在本发明的一些实施例中,所述从机侧单元包括相互可通信地连接的一spi从机和一从机侧fpga,其中所述从机侧fpga用于接收来自所述主机侧单元的所述spi主机数据;其中所述spi从机用于基于所述spi主机数据中的所述数据读取长度信息和所述寄存器地址信息,读取回的所述spi从机数据。

[0045]

在本发明的一些实施例中,所述从机侧fpga进一步用于缓存读取的所述spi从机数据。

[0046]

在本发明的一些实施例中,所述从机侧fpga进一步用于发送所述从机侧数据至所述主机侧单元。

[0047]

根据本发明的另一方面,本发明还提供了一主机侧单元,供通过一传输单元与一从机侧单元可通信地连接,其中所述主机侧单元包括:

[0048]

至少一spi主机,其中所述spi主机用于读取一spi主机数据,其中所述spi主机数据携带有一具有第一预定数量字节的数据读取长度信息和一需要读取的寄存器地址信息;和

[0049]

至少一主机侧fpga,其中所述主机侧fpga与所述spi主机可通信地连接,用于接收所述spi主机数据,以通过该传输单元传输至该从机侧单元,其中所述主机侧fpga进一步用于接收并发送来自该从机侧单元的一从机侧数据至所述spi主机。

[0050]

在本发明的一些实施例中,所述从机侧数据包括一具有第二预定数量字节的无效数据和一spi从机数据;其中所述spi主机进一步用于从所述从机侧数据中剔除所述无效数据,以获得所述spi从机数据。

[0051]

根据本发明的另一方面,本发明还提供了一从机侧单元,供通过一传输单元与一主机侧单元可通信地连接,其中所述从机侧单元包括:

[0052]

至少一从机侧fpga,其中所述从机侧fpga用于接收来自该主机侧单元的所述spi主机数据;和

[0053]

至少一spi从机,其中所述spi从机与所述从机侧fpga可通信地连接,用于基于所述spi主机数据中的所述数据读取长度信息和所述寄存器地址信息,读取回的一spi从机数据。

[0054]

在本发明的一些实施例中,所述从机侧fpga进一步用于缓存读取的所述spi从机数据。

[0055]

在本发明的一些实施例中,所述从机侧fpga进一步用于发送一从机侧数据至该主机侧单元,其中所述从机侧数据包括一具有第二预定数量字节的无效数据和所述spi从机数据。

[0056]

通过对随后的描述和附图的理解,本发明进一步的目的和优势将得以充分体现。

[0057]

本发明的这些和其它目的、特点和优势,通过下述的详细说明,附图和权利要求得以充分体现。

附图说明

[0058]

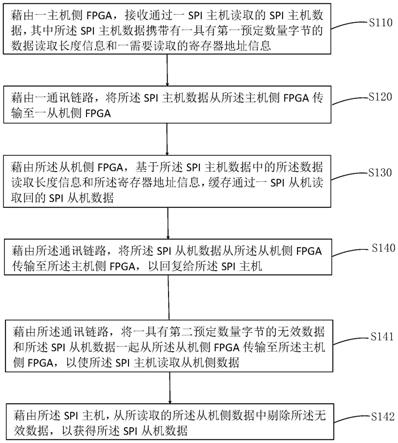

图1是根据本发明的一实施例的一基于spi协议的数据传输方法的流程示意图。

[0059]

图2是根据本发明的一实施例的一基于spi协议的主机侧数据传输方法的流程示

意图。

[0060]

图3是根据本发明的一实施例的一基于spi协议的从机侧数据传输方法的流程示意图。

[0061]

图4是根据本发明的一实施例的一基于spi协议的数据传输系统的结构示意图。

具体实施方式

[0062]

以下描述用于揭露本发明以使本领域技术人员能够实现本发明。以下描述中的优选实施例只作为举例,本领域技术人员可以想到其他显而易见的变型。在以下描述中界定的本发明的基本原理可以应用于其他实施方案、变形方案、改进方案、等同方案以及没有背离本发明的精神和范围的其他技术方案。

[0063]

在本发明中,权利要求和说明书中术语“一”应理解为“一个或多个”,即在一个实施例,一个元件的数量可以为一个,而在另外的实施例中,该元件的数量可以为多个。除非在本发明的揭露中明确示意该元件的数量只有一个,否则术语“一”并不能理解为唯一或单一,术语“一”不能理解为对数量的限制。

[0064]

在本发明的描述中,需要理解的是,属于“第一”、“第二”等仅用于描述目的,而不能理解为指示或者暗示相对重要性。本发明的描述中,需要说明的是,除非另有明确的规定和限定,属于“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接或者一体地连接;可以是机械连接,也可以是电连接;可以是直接连接,也可以是通过媒介间接连结。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

[0065]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

[0066]

在现有的诸如分体式ar/vr眼镜等等之类的分体式近眼显示设备中,位于hmd头戴侧的spi从机与位于box盒子侧的spi主机之间往往通过fpga进行上下行数据封装和传输。因为基于spi协议的时钟信号是由所述spi主机产生的,所述在读取数据过程中所述spi从机需要在主机发送完寄存器地址信息后的下一个时钟周期就发送读取的数据。而由于分体式的近眼显示设备的spi主机和spi从机之间的信号需要通过fpga编码传输,会产生信号时延,因此会导致所述spi主机无法及时读取到数据而出错。

[0067]

目前,现有分体式的近眼显示设备在采集spi从机的数据时,通常会采用所述spi主机读取两次的方式。具体地,首先,现有分体式的近眼显示设备的所述spi主机在第一次读取操作时,通过fpga链路将所述spi主机所要读取的寄存器地址和读取长度从所述box盒子侧传输到所述hmd头戴侧,与此同时所述hmd头戴侧的所述spi从机读取数据后进行缓存;现有分体式的近眼显示设备的所述spi主机在第二次读取操作时,发送所缓存的数据至所述box盒子侧,以完成数据的采集。

[0068]

然而,由于现有分体式的近眼显示设备的所述spi主机所要读取的数据长度需要以所述spi主机的时钟周期次数的方式来传输至所述spi从机,也就是说,所述spi主机所要读取的数据长度越长,所述spi主机在第一次读取操作时所需的时钟周期的次数也就越多,使得现有分体式的近眼显示设备在采集所述spi从机的数据时的时延也就越大,因此采用所述spi主机读取两次的方式会导致fpga链路传输带宽的浪费,这对实时性要求较高的场景会产生比较大的影响。为了解决上述问题,本发明提供了一基于spi协议的数据传输方法及其系统,其能够减小spi数据传输的时延。

[0069]

示意性方法

[0070]

如图1所示,根据本发明的一实施例的一基于spi协议的数据传输方法被阐明。具体地,所述基于spi协议的数据传输方法,包括步骤:

[0071]

s110:藉由一主机侧fpga,接收通过一spi主机读取的spi主机数据,其中所述spi主机数据携带有一具有第一预定数量字节的数据读取长度信息和一需要读取的寄存器地址信息;

[0072]

s120:藉由一通讯链路,将所述spi主机数据从所述主机侧fpga传输至一从机侧fpga;

[0073]

s130:藉由所述从机侧fpga,基于所述spi主机数据中的所述数据读取长度信息和所述寄存器地址信息,缓存通过一spi从机读取回的spi从机数据;以及

[0074]

s140:藉由所述通讯链路,将所述spi从机数据从所述从机侧fpga传输至所述主机侧fpga,以回复给所述spi主机。

[0075]

值得注意的是,由于所述spi主机数据中直接包含有所述读取长度数据和所述寄存器地址数据,也就是说,所述从机侧fpga能够从所述spi主机数据中获得需要读取的数据长度和寄存器地址,以便通过所述spi从机读取相应长度的数据,进而被缓存在所述从机侧fpga。可以理解的是,在本发明的一实施例中,所述主机侧fpga可以但不限于被实施为一与所述spi主机一起被可通信地设置于所述box盒子侧的fpga。

[0076]

进一步地,所述第一预定数量字节可以但不限于根据所要读取的数据长度进行设定。优选地,所述第一预定数量字节被设定为两个字节。当然,在本发明的其他示例中,当需要读取的数据长度较小时,所述第一预定数量字节也可以被设定为一个字节;当需要读取的数据长度较大时,所述第一预定数量字节也可以被设定为大于两个字节。

[0077]

更优选地,所述spi主机数据中携带所述数据读取长度信息的字节位于携带所述寄存器地址信息的字节之前,以使所述spi主机在发送完所述spi主机数据中携带所述寄存器地址的字节之后的下一个时钟,就开始读取接收数据,进而无需修改spi协议的实现逻辑。可以理解的是,spi传输协议规定时钟信号由所述spi主机产生,并且spi从机需要按照所述spi主机的时钟节拍传输数据。

[0078]

值得一提的是,在本发明的上述实施例中,如图1所示,所述基于spi协议的数据传输方法的所述步骤s140,包括步骤:

[0079]

s141:藉由所述通讯链路,将一具有第二预定数量字节的无效数据和所述spi从机数据一起从所述从机侧fpga传输至所述主机侧fpga,以使所述spi主机读取从机侧数据;和

[0080]

s142:藉由所述spi主机,从所读取的所述从机侧数据中剔除所述无效数据,以获得所述spi从机数据。

[0081]

优选地,与所述spi主机数据中的所述数据读取长度信息对应的时钟长度等于与所述无效数据对应的时钟长度和与所述spi从机数据对应的时钟长度之和。换言之,所述基于spi协议的数据传输方法能够采用在原有正常时钟周期中插入读取时钟周期,用于fpga的上下行传输的方式,有助于完成spi数据的读取,以防数据出错。可以理解的是,本发明提及的所述时钟长度可以由字节数量来表示。例如,与所述无效数据对应的时钟长度等于所述第二预定数量字节的数量。

[0082]

更优选地,在本发明的一示例中,所述第二预定数量字节被实施为四个字节,以满足在所述主机侧fpga和所述从机侧fpga之间上下行传输的时间消耗需求。

[0083]

最优选地,在通过所述spi主机读取的所述从机侧数据中与所述无效数据对应的字节位于与所述spi从机数据对应的字节之前,以使与所述无效数据对应的时钟长度被用于在所述主机侧fpga和所述从机侧fpga之间上下行传输的时间消耗。可以理解的是,正是由于与所述无效数据对应的字节位于与所述spi从机数据对应的字节之前,因此本发明的所述基于spi协议的数据传输方法在满足上下行传输的时间消耗的同时,还有助于后续基于字节数量和位置,从所读取的所述从机侧数据中剔除所述无效数据。

[0084]

值得注意的是,在ar眼镜分体式方案的一个示例中,box盒子侧和hmd头戴侧之间需要经过fpga转发数据,而fpga传输需要时间,会导致spi主机和spi从机的无法在规定的时钟周期内完成数据读取。通过对fpga的实现方式分析,所述box盒子侧的fpga会按字节接收完所述spi主机数据,然后通过通讯链路传输至所述hmd头戴侧,由所述hmd头戴侧的fpga通过所述spi从机发送到器件,然后读取回数据缓存,再通过所述通讯链路回传到所述box盒子侧的fpga,由所述box盒子侧的fpga回复给所述spi主机,但所述通讯链路需要消耗时间。

[0085]

此外,spi标准协议实现读取数据时,所述spi主机会在发送完最后一比特的寄存器地址后,在下一个时钟开始接收所述spi从机的数据,并且读取数据长度由时钟长度控制。针对所述spi标准协议进行分析后,发现可以在所述spi主机发送完最后一比特数据到下一个时钟之间插入空隙,该空隙用于fpga传输时间消耗。而因为嵌入式处理器spi控制器一般为硬件实现,无法修改协议实现逻辑,所以本发明的一示例采用在读取数据长度上增加四字节,让硬件spi控制器产生的时钟比原有多出四字节对应的时钟周期,所述四字节对应的时钟周期用于fpga上下行传输,最后从所述spi主机侧读取的数据剔除掉前面四字节无效数据。

[0086]

进一步地,因为所述hmd头戴侧的fpga不仅需要缓存数据,而且需要获取读取的数据长度,但标准spi协议读取数据长度由所述spi主机的时钟周期个数控制,并不需要缓存数据,因此本发明解决该问题的方法是采用提前将需要读取的数据长度发送至所述hmd头戴侧。例如,通过对spi协议分析,可以在所述spi主机发送需要读取的寄存器地址前插入二字节表示需要读取的数据长度,以便在所述hmd头戴侧的fpga接收到后,先取出前二字节长度数据,再使所述hmd头戴侧的fpga根据该长度和寄存器地址读取所述spi从机的数据,以缓存数据。这样,本发明解决了ar眼镜分体式方案中头戴侧spi器件数据读取问题,优化了现有方案所述spi主机读取两次造成的fpga传输带宽浪费和数据采集时延,且对所述spi主机侧改动较小,适应性强。

[0087]

根据本发明的另一方面,如图2所示,根据本发明的一实施例的基于spi协议的主

机侧数据传输方法被阐明。具体地,所述基于spi协议的主机侧数据传输方法,包括步骤:

[0088]

s210:藉由一主机侧fpga,接收并发送通过一spi主机读取的spi主机数据,其中所述spi主机数据携带有一具有第一预定数量字节的数据读取长度信息和一需要读取的寄存器地址信息;和

[0089]

s220:藉由所述主机侧fpga,接收并发送一从机侧数据至所述spi主机。

[0090]

值得注意的是,在本发明的上述实施例中,如图2所示,所述基于spi协议的主机侧数据传输方法的所述步骤s220,包括步骤:

[0091]

s221:藉由所述主机侧fpga,接收所述从机侧数据,其中所述从机侧数据包括一具有第二预定数量字节的无效数据和一spi从机数据;和

[0092]

s222:藉由所述spi主机,从所述从机侧数据中剔除所述无效数据,以获得所述spi从机数据。

[0093]

根据本发明的另一方面,如图3所示,根据本发明的一实施例的基于spi协议的从机侧数据传输方法被阐明。具体地,所述基于spi协议的从机侧数据传输方法,包括步骤:

[0094]

s310:藉由一从机侧fpga,接收一spi主机数据,其中所述spi主机数据携带有一具有第一预定数量字节的数据读取长度信息和一需要读取的寄存器地址信息;

[0095]

s320:藉由一spi从机,基于所述spi主机数据中的所述数据读取长度信息和所述寄存器地址信息,读取回的spi从机数据;以及

[0096]

s330:藉由所述从机侧fpga,缓存读取的所述spi从机数据。

[0097]

进一步地,如图3所示,所述基于spi协议的从机侧数据传输方法,进一步包括步骤:

[0098]

s340:藉由所述从机侧fpga,发送一从机侧数据至一主机侧fpga,其中所述从机侧数据包括一具有第二预定数量字节的无效数据和所述spi从机数据。

[0099]

示意性系统

[0100]

参考说明书附图4,根据本发明的一实施例的一基于spi协议的数据传输系统被阐明。具体地,所述基于spi协议的数据传输系统10包括一主机侧单元11、一传输单元12以及一从机侧单元13,其中所述传输单元12将所述主机侧单元11与所述从机侧单元13可通信地连接,以便在所述主机侧单元11和所述从机侧单元13之间传输基于spi协议的数据。可以理解的是,在本发明的一示例中,所述主机侧单元11可以但不限于被实施为分体式近眼显示设备的box盒子,相应地,所述从机侧单元13可以但不限于被实施为所述分体式近眼显示设备的hmd头戴器件。此外,所述传输单元12可以但不限于被实施为所述分体式近眼显示设备的通讯链路,例如数据线等等。

[0101]

更具体地,如图4所示,所述基于spi协议的数据传输系统10的所述主机侧单元11可以包括相互可通信地连接的至少一spi主机111和至少一主机侧fpga112,其中所述spi主机111用于读取一spi主机数据,其中所述spi主机数据携带有一具有第一预定数量字节的数据读取长度信息和一需要读取的寄存器地址信息;其中所述主机侧fpga112用于接收所述spi主机数据,以通过所述传输单元12传输至所述从机侧单元13,并且接收并发送来自所述从机侧单元13的一从机侧数据至所述spi主机111。

[0102]

值得注意的时,所述从机侧数据包括一具有第二预定数量字节的无效数据和一spi从机数据。

[0103]

优选地,所述spi主机111进一步用于从所述从机侧数据中剔除所述无效数据,以获得所述spi从机数据。

[0104]

值得一提的是,根据本发明的上述实施例,如图4所示,所述基于spi协议的数据传输系统10的所述从机侧单元13可以包括相互可通信地连接的至少一spi从机131和至少一从机侧fpga132,其中所述从机侧fpga132用于接收来自所述主机侧单元11的所述spi主机数据;其中所述spi从机131用于基于所述spi主机数据中的所述数据读取长度信息和所述寄存器地址信息,读取回的所述spi从机数据。与此同时,所述从机侧fpga进一步用于缓存读取的所述spi从机数据。可以理解的是,所述主机侧单元11的所述主机侧fpga112与所述从机侧单元13的所述从机侧fpga132通过所述传输单元12可通信地连接。

[0105]

优选地,所述从机侧fpga进一步用于发送所述从机侧数据至所述主机侧单元11,其中所述从机侧数据包括一具有第二预定数量字节的无效数据和所述spi从机数据。

[0106]

值得注意的是,在本发明的其他示例中,本发明可以仅提供所述基于spi协议的数据传输系统10的所述主机侧单元11或所述从机侧单元13,并且所述主机侧单元11和所述从机侧单元13分别具有上述功能,本发明对此不在赘述。

[0107]

还需要指出的是,在本发明的装置、设备和方法中,各部件或各步骤是可以分解和/或重新组合的。这些分解和/或重新组合应视为本发明的等效方案。

[0108]

提供所公开的方面的以上描述以使本领域的任何技术人员能够做出或者使用本发明。对这些方面的各种修改对于本领域技术人员而言是非常显而易见的,并且在此定义的一般原理可以应用于其他方面而不脱离本发明的范围。因此,本发明不意图被限制到在此示出的方面,而是按照与在此公开的原理和新颖的特征一致的最宽范围。

[0109]

本领域的技术人员应理解,上述描述及附图中所示的本发明的实施例只作为举例而并不限制本发明。本发明的目的已经完整并有效地实现。本发明的功能及结构原理已在实施例中展示和说明,在没有背离所述原理下,本发明的实施方式可以有任何变形或修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1