一种地址宽度自动识别的方法与流程

[0001]

本发明涉及通信领域,特别涉及一种地址宽度自动识别的方法。

背景技术:

[0002]

随着科技的不断发展,spi技术越来越被广泛使用。spi,是serial peripheral interface的缩写,意思是串行外围设备接口。spi是一种通信接口。spi flash是一种使用spi通信的flash。spi接口主要应用在eeprom,flash,实时时钟,ad转换器,还有数字信号处理器和数字信号解码器之间。spi,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为pcb的布局上节省空间,提供方便。

[0003]

spi的通信原理以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线。是所有基于spi的设备共有的,它们是sdi(数据输入),是主设备数据输入,从设备数据输出;sdo(数据输出),是主设备数据输出,从设备数据输入;sck(时钟),是时钟信号,由主设备产生;cs(片选),是从设备使能信号,由主设备控制。

[0004]

其中cs是否是控制芯片被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。这就允许在同一总线上连接多个spi设备。接下来就负责通讯的3根线了。通讯是通过数据交换完成的,spi是串行通讯协议,也就是说数据是一位一位的传输的。由sck提供时钟脉冲,sdi,sdo则基于此脉冲完成数据传输。数据输出通过sdo线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。完成一位数据传输,输入也使用同样原理。这样,在至少8次时钟信号的改变(上沿和下沿为一次),就可以完成8位数据的传输。

[0005]

spi接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。在sclk的下降沿上数据改变,同时一位数据被存入移位寄存器。

[0006]

然而,现在spi flash设备缺少统一的协议规范,不同厂家,不同型号,不同容量的spi flash有不同的地址宽度。系统上电,通过spi flash启动时,或者读写spi flash设备时,需要预先知道spi flash的地址宽度,把地址宽度填入启动代码bootrom。并且,在芯片量产时,bootrom是固化的,不支持修改,不支持可扩展,只能支持固定的几款spi flash。

[0007]

这就出现了需要已知spi flash的地址宽度,使用对应固定的代码,只能操作地址宽度相同的spi flash设备,存在不同地址宽度spi flash兼容性的问题。

技术实现要素:

[0008]

为了解决上述现有技术中存在的问题,本发明的目的在于:自动识别spi flash的地址宽度,用简单的方法就可以操作不同地址宽度的spi flash设备。

[0009]

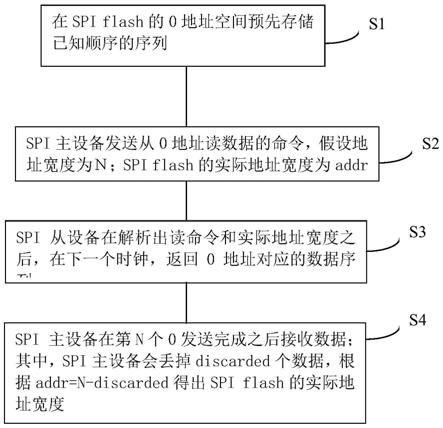

本发明提供一种地址宽度自动识别的方法,包括以下步骤:

[0010]

s1,在spi flash的0地址空间预先存储已知顺序的序列;

[0011]

s2,spi主设备发送从0地址读数据的命令,假设地址宽度为n;

[0012]

spi flash的实际地址宽度为addr;

[0013]

s3,spi从设备在解析出读命令和实际地址宽度之后,在下一个时钟(图1中d点)返回0地址对应的数据序列;

[0014]

s4,spi主设备在第n个0发送完成之后接收数据(图1中e点);

[0015]

其中,spi主设备会丢掉discarded个数据,根据addr=n-discarded得出spi flash的实际地址宽度。

[0016]

所述的n大于实际的spi flash地址宽度。

[0017]

所述的已知顺序的序列是固定序列,每个元素在序列中的位置是固定的。

[0018]

所述步骤s1的所述的0地址的值不受地址宽度影响。

[0019]

所述的步骤s4中根据主设备读取到的第一个数据在已知序列中的位置,可以按顺序推算得出丢弃数据个数discarded。

[0020]

所述的地址宽度为n为最大的地址宽度。

[0021]

所述的步骤s1中的地址宽度n为x个0,其中x为整数。

[0022]

所述的步骤s2中的读数据的命令是单线读命令。

[0023]

本申请的优势在于:通过简单的方法即可解决兼容性的问题,大大降低成本,提高效率。

附图说明

[0024]

此处所说明的附图用来提供对本发明的进一步理解,构成本申请的一部分,并不构成对本发明的限定。

[0025]

图1是本发明的方法的示意框图。

[0026]

图2是本发明的方法的流程图。

[0027]

图3是本发明的具体实施例的示意图。

具体实施方式

[0028]

目前,本技术领域常用的技术术语包括:

[0029]

flash:一种非易失性存储器。

[0030]

spi flash:使用spi接口的flash设备。

[0031]

bootrom:一种固化在芯片里面的启动代码。

[0032]

spi接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。在sclk的下降沿上数据改变,同时一位数据被存入移位寄存器。

[0033]

spi flash读数据的命令格式为:

[0034]

s1,spi主设备发送读数据命令,接着spi主设备发送相应地址长度的地址。

[0035]

s2,在下一个时钟,spi从设备接收数据。

[0036]

下图中,cs是片选信号。clk是时钟。dt是数据发送线。dr是数据接收线。cmd是spi flash的单线读命令。

[0037]

下文中长度以byte为单位。

[0038]

如图1所示,本申请涉及的自动识别地址宽度的方法,是利用spi总线协议的特性,

和0地址这个值不受地址宽度影响的特性。

[0039]

首先,spi主设备发送从0地址读数据的命令,假设地址宽度为n(n大于实际的spi flash地址宽度)。在spi flash的0地址空间预先存储已知顺序的固定序列。每个元素在序列中的位置是固定的。spi flash的实际地址长度为addr(图1中用addr表示)。

[0040]

spi从设备在解析出读命令和addr个0之后,在下一个时钟(图1中d点)返回0地址对应的数据序列。

[0041]

spi主设备在第n个0发送完成之后接收数据(图1中e点)。spi主设备会丢掉discarded个数据(图1中用discarded表示)。根据主设备读取到的第一个数据在已知序列中的位置,可以得出丢弃数据个数discarded。就可以探测出spi flash的地址宽度addr=n-discarded。

[0042]

具体实施例如图2所示:

[0043]

在spi flash的0地址空间预先存储序列0x6,0x5,0x4,0x3,0x2。探测的最大地址宽度n=6。

[0044]

spi主设备给spi flash发送单线读命令和6个0做为地址。

[0045]

当spi flash解析出cmd和地址之后,在图2中d点返回0地址空间存储的数据。

[0046]

spi主设备在图2中e点时刻接收数据。图2中的0x6和0x5是被丢弃的数据。通过spi主设备接收到的第一个数据判断,的被丢弃数据个数为2。可以探测出地址长度addr=n-2=4。

[0047]

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明实施例可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1