Verilog文件转换方法、装置、存储介质及设备与流程

verilog文件转换方法、装置、存储介质及设备

技术领域

1.本发明涉及计算机技术领域,尤其涉及一种verilog文件转换方法、装置、存储介质及设备。

背景技术:

2.目前,在集成电路设计中,主要可分为半定制电路设计流程和全定制电路设计流程。其中,半定制电路设计,是指根据芯片设计规格,使用硬件描述语言(verilog或vhdl(very

‑

high

‑

speed integrated circuit hardware description language,超高速集成电路硬件描述语言))进行芯片的行为级描述,其中,verilog即verilog hdl,是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言。然后使用综合工具将硬件描述语言转换为门级网表,最后通过自动布局布线工具进行自动化物理设计的一种流程。在该流程中,大多数步骤可以通过eda(electronic design automation,电子设计自动化)工具来进行自动化设计,可以很方便实现大规模的芯片电路设计。在全定制电路设计,根据用户的功能与性能要求,先设计出满足功能的电路,然后手动进行版图设计和优化。在半定制电路设计流程中,是将verilog或vhdl设计文件通过综合工具转换为门级网表,然后经自动布局布线工具得到最终的版图设计。在这种流程中,verilog设计文件是可以和eda工具兼容的,可以被eda工具正确识别的。但在全定制设计流程中,是直接进行电路设计,不需将verilog经综合工具转换为门级网表。在这种情况下,verilog文件一般仅用于前期的功能验证,很可能会出现无法与其他eda工具兼容的情况。目前,在大型芯片设计中,经常是半定制电路设计和全定制定路设计综合使用,部分特殊的ip(intellectual property,知识产权模块)会采用定制电路设计流程完成ip内部的电路和版图设计,然后在芯片的顶层设计时会调用ip的版图文件和其他设计文件进行顶层的设计,同时ip的verilog文件在顶层设计时也会被调用到,来进行顶层verilog仿真验证和dft(design for testability,可测性设计)。这样全定制电路设计模块的verilog经常会出现无法兼容后续流程eda工具的情况。甚至也可能出现半定制设计流程中的verilog文件在后续流程中可以对某一些eda工具兼容,但对其他eda工具却无法兼容,导致verilog文件的可移植性不好的问题。

技术实现要素:

3.有鉴于此,本发明一个或多个实施例提供一种verilog文件转换方法、装置、存储介质及设备,可提高verilog文件的与eda工具的兼容性。

4.本发明一个或多个实施例提供了一种verilog文件转换方法,包括:获取原始verilog文件以及配置文件,其中,所述配置文件中包括与目标电子设计自动化eda工具对应的目标表述方式的信息;从所述原始verilog文件中获取描述逻辑功能的目标代码;将所述目标代码转换为以所述目标表述方式进行表示,得到转换后的文件;

5.根据所述目标代码生成第一测试激励文件;根据所述第一测试激励文件分别以所述原始verilog文件以及所述转换后的文件进行仿真测试,得到第一测试结果;根据所述第

一测试结果,判断所述转换后文件与所述原始verilog文件的功能是否一致。

6.可选的,所述第一测试结果中包括以所述原始verilog文件进行仿真测试时仿真工具输出的第一信号,以及以所述转换后的文件进行仿真测试时,仿真工具输出的第二信号,根据所述第一测试结果,判断所述转换后文件与所述原始verilog文件的功能是否一致,包括:比较所述第一信号与所述第二信号;响应于所述第一信号与所述第二信号一致,确定所述转换后的文件与所述原始verilog文件的功能一致;响应于所述第一信号与所述第二信号不一致,确定所述转换后的文件与所述原始verilog文件的功能不一致。

7.可选的,所述方法还包括:响应于根据所述第一测试结果判断所述转换后的文件与所述原始verilog文件的功能不一致,修改所述配置文件;根据修改后的配置文件重新从所述原始verilog文件中获取描述逻辑功能的目标代码,以及将重新得到的目标代码转换为以所述目标表述方式进行表示,得到重新转换后的文件。

8.可选的,从所述原始verilog文件中获取描述逻辑功能的目标代码,包括:从所述原始verilog文件中识别出描述逻辑功能的代码;从识别出的代码中提取出描述目标逻辑功能的所述目标代码。

9.可选的,所述配置文件中还包括:逻辑功能与用于表示所述逻辑功能的verilog代码的对应关系。

10.可选的,从所述原始verilog文件中识别出描述逻辑功能的代码,包括:根据所述逻辑功能与用于表示所述逻辑功能的verilog代码的对应关系,从所述verilog文件中识别出描述逻辑功能的代码。

11.可选的,所述方法还包括:在从所述原始verilog文件中获取描述逻辑功能的目标代码之后,以第二测试激励文件对所述原始verilog文件进行测试,得到第二测试结果;根据所述第二测试结果确定出所述原始verilog文件中包括的目标逻辑功能;根据所述目标逻辑功能确定所述目标代码是否正确。

12.本发明一个或多个实施例还提供了一种verilog文件转换装置,包括:第一获取模块,被配置为获取原始verilog文件以及配置文件,其中,所述配置文件中包括与目标电子设计自动化eda工具对应的目标表述方式的信息;第二获取模块,被配置为从所述原始verilog文件中获取描述逻辑功能的目标代码;第一转换模块,被配置为将所述目标代码转换为以所述目标表述方式进行表示,得到转换后的文件;生成模块,被配置为根据所述目标代码生成第一测试激励文件;第一测试模块,被配置为根据所述第一测试激励文件分别以所述原始verilog文件以及所述转换后的文件进行仿真测试,得到第一测试结果;验证模块,被配置为根据所述第一测试结果,判断所述转换后文件与所述原始verilog文件的功能是否一致。

13.可选的,所述第一测试结果中包括以所述原始verilog文件进行仿真测试时仿真工具输出的第一信号,以及以转换后的文件进行仿真测试时,仿真工具输出的第二信号,所述验证模块具体被配置为:比较所述第一信号与所述第二信号;响应于所述第一信号与所述第二信号一致,确定转换后的所述文件与所述原始verilog文件的功能一致;响应于所述第一信号与所述第二信号不一致,确定转换后的文件与所述原始verilog文件的功能不一致。

14.可选的,所述装置还包括:修改模块,被配置为响应于根据所述第一测试结果判断

所述转换后的文件与所述原始verilog文件的功能不一致,修改所述配置文件;第二转换模块,被配置为根据修改后的配置文件重新从所述原始verilog文件中获取描述逻辑功能的目标代码,以及将重新得到的目标代码转换为以所述目标表述方式进行表示,得到重新转换后的文件。

15.可选的,所述第二获取模块具体被配置为:从所述原始verilog文件中识别出描述逻辑功能的代码;从识别出的代码中提取出描述目标逻辑功能的所述目标代码。

16.可选的,所述配置文件中还包括:逻辑功能与用于表示所述逻辑功能的verilog代码的对应关系。

17.可选的,所述第二获取模块具体被配置为:根据所述逻辑功能与用于表示所述逻辑功能的verilog代码的对应关系,从所述verilog文件中识别出描述逻辑功能的代码。

18.可选的,所述装置还包括:第二测试模块,被配置为在从所述原始verilog文件中获取描述逻辑功能的目标代码之后,以第二测试激励文件对所述原始verilog文件进行测试,得到第二测试结果;第一确定模块,被配置为根据所述第二测试结果确定出所述原始verilog文件中包括的目标逻辑功能;第二确定模块,被配置为根据所述目标逻辑功能确定所述目标代码是否正确。

19.本发明一个或多个实施例还提供了一种电子设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现如上述任意一种verilog文件转换方法。

20.本发明一个或多个实施例还提供了一种非暂态计算机可读存储介质,所述非暂态计算机可读存储介质存储计算机指令,所述计算机指令用于使所述计算机执行上述任意一种verilog文件转换方法。

21.本发明一个或多个实施例提供的verilog文件转换方法,从verilog文件中获取描述逻辑功能的目标代码,将该目标代码以配置文件中的与目标eda工具对应的目标表述方式进行表示,再通过测试激励文件验证转换后的文件与原verilog文件是否等效,实现了将verilog文件等效转换为与目标eda工具兼容的文件的目的,使得verilog文件可应用于各种eda工具,提高了verilog文件的通用性。

附图说明

22.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

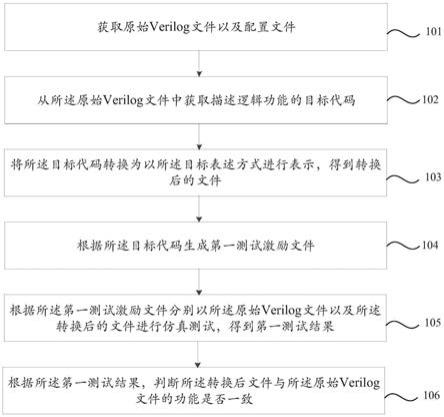

23.图1是根据本发明一个或多个实施例示出的一种verilog文件转换方法的流程图;

24.图2是根据本发明一个或多个实施例示出的一种verilog文件转换方法的流程图;

25.图3是根据本发明一个或多个实施例示出的一种verilog文件转换方法的流程图;

26.图4是根据本发明一个或多个实施例示出的一种verilog文件转换装置的结构示意图;

27.图5是根据本发明一个或多个实施例示出的一种电子设备的结构示意图。

具体实施方式

28.下面结合附图对本发明实施例进行详细描述。

29.应当明确,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

30.图1是根据本发明一个或多个实施例示出的一种verilog文件转换方法的流程图,如图1所示,该方法包括:

31.步骤101:获取原始verilog文件以及配置文件,其中,所述配置文件中包括与eda工具对应的目标表述方式的信息;

32.其中,配置文件中例如定义了verilog文件需要兼容的目标eda工具以及该目标eda工具对应的verilog表述方式。例如,若实现逻辑与的功能,可以有如下几种表述方式:

33.行为级:out=a&b;

34.门级:and i1(out,a,b);

35.或者也可以使用原语的形式来表示逻辑与的功能。

36.又例如,配置文件中还可以仅定义了通用的verilog表述方式,在此基础上,在上述步骤101中,可根据配置文件将上述verilog文件转换为以通用的verilog表述方式进行表示。

37.步骤102:从所述原始verilog文件中获取描述逻辑功能的目标代码;

38.其中,本发明一个或多个实施例中的逻辑功能例如可以是一个单独的逻辑器件可实现的逻辑功能,还可以是至少两个逻辑器件通过某种连接关系进行连接所构成的功能单元/模块可实现的逻辑功能。在此基础上,可预先构建一个用于识别verilog文件中描述逻辑功能的代码的算法,该算法中可预先定义了各种逻辑器件对应的verilog代码,或者,还可定义了由至少两个逻辑器件构成的功能模块对应的verilog代码段,将上述verilog文件作为该算法的输入,运行该算法,即可的输出verilog文件中描述逻辑功能的代码,以及代码所描述的逻辑功能,再根据代码的用途,从输出的代码中提取出目标代码。举例说明,对于一个较为复杂的ip模块,例如存储器来说,当原始verilog文件仅是用于顶层的dft设计时(如扫描链设计),若采用完成的原始verilog文件进行顶层的dft设计,会导致设计周期较长,故,可根据识别出的描述逻辑功能的代码的用途,将与测试相关的verilog逻辑提取出来,以去除冗余的逻辑(即与测试无关的逻辑,如存储阵列逻辑等),得到目标代码,这样可以加快后续设计进程,简化设计流程。

39.步骤103:将所述目标代码转换为以所述目标表述方式进行表示,得到转换后的文件;

40.例如,针对各种eda工具,可预先设置各种eda工具能够兼容的verilog表述方式,将各种eda工具能够兼容的verilog表达方式设置为与该eda工具对应的目标表述方式。假设某一eda工具a可兼容的目标表述方式包括表述方式1、表述方式2以及表述方式3,以此处假设的情况为例,在上述步骤103中,可将目标代码转换为按照表述方式1、表述方式2以及表述方式3中的任意一种表述方式进行表达。

41.步骤104:根据所述目标代码生成第一测试激励文件;

42.例如,可根据所述目标代码所描述的逻辑功能生成一套仿真激励文件,用于对这

些逻辑功能进行仿真测试。

43.步骤105:根据所述第一测试激励文件分别以所述原始verilog文件以及所述转换后的文件进行仿真测试,得到第一测试结果;

44.在一个例子中,通过仿真工具根据第一测试激励文件以原始verilog文件进行仿真测试,得到仿真工具输出的第一信号,通过仿真工具根据第一测试激励文件以转换后的文件进行仿真测试,得到仿真工具输出的第二信号。由于基于原始verilog文件以及转换后的文件进行仿真测试所使用的测试激励文件相同,故,通过判断第一信号以及第二信号的一致性,即可确定转换后的文件是否与原始verilog文件等效。

45.步骤106:根据所述第一测试结果,判断所述转换后文件与所述原始verilog文件的功能是否一致。

46.沿用上述例子,若通过对比,确认第一信号与第二信号一致,可确定转换后的文件与原verilog文件等效,否则,可确定转换后的文件与原verilog文件不等效,这时,可以重新转换verilog文件。

47.本发明一个或多个实施例提供的verilog文件转换方法,从verilog文件中获取描述逻辑功能的目标代码,将该目标代码以配置文件中的与目标eda工具对应的目标表述方式进行表示,再通过测试激励文件验证转换后的文件与原始verilog文件是否等效,实现了将verilog文件等效转换为与目标eda工具兼容的文件的目的,使得verilog文件可应用于各种eda工具,提高了verilog文件的通用性。此外,基于该方法由于可使用比较简单的方式将eda工具不兼容的verilog转化为可兼容主流eda工具的verilog,故无需重新设计verilog文件,节省设计时间。

48.在本发明的一个或多个实施例中,verilog文件的设计者还会自定义一些功能模块,在该种情况下,所述配置文件中还可包括:逻辑功能与用于表示所述逻辑功能的verilog代码的对应关系。基于此,在从所述verilog文件中获取描述逻辑功能的目标代码时,可基于该对应关系有效地识别verilog文件中的一些自定义的功能模块,得到描述逻辑功能的代码。其中,逻辑功能例如可以由一个逻辑器件实现,或者由至少两个相连的逻辑器件实现。

49.在本发明的一个或多个实施例中,上述verilog文件转换方法还可包括:响应于根据所述第一测试结果判断所述转换后的文件与所述原始verilog文件的功能不一致,修改所述配置文件;根据修改后的配置文件重新从所述原始verilog文件中获取描述逻辑功能的目标代码,以及将重新得到的目标代码转换为以所述目标表述方式进行表示,得到重新转换后的文件。沿用上述例子,若上述第一信号与第二信号不一致,则可确定转换后的文件与原始verilog文件的功能不一致,出现该种情况,有可能是在对原始verilog文件进行转换时,原始verilog文件中有一些特殊的功能模块未能被有效识别出,例如,当原始verilog文件包括一些用户自定义的功能模块时,在从原始verilog文件中识别出描述逻辑功能的代码时,可能无法正确识别出这些功能模块。故,可在根据所述第一测试结果确定转换后的文件与原始verilog文件的功能不一致后,可通过在配置文件中增加/修改对这些自定义功能模块的表述,以确保可以在修改配置文件后,再次对原始verillog文件进行识别时,可以正确识别出verilog文件中逻辑功能。

50.在本发明的一个或多个实施例中,所述第一测试结果中包括以所述原始verilog

文件进行仿真测试时仿真工具输出的第一信号,以及以转换后的文件进行仿真测试时,仿真工具输出的第二信号,根据所述第一测试结果,判断所述转换后文件与所述原始verilog文件的功能是否一致,可包括:比较所述第一信号与所述第二信号;响应于所述第一信号与所述第二信号一致,确定所述转换后的文件与所述原始verilog文件的功能一致;响应于所述第一信号与所述第二信号不一致,确定所述转换后的文件与所述原始verilog文件的功能不一致。

51.图2是根据本发明一个或多个实施例示出的一种verilog文件转换方法的流程图,以图2所示为例,在对原始verilog文件和转换后的文件进行等效性验证时,采用上述测试激励文件,将测试激励信号分别添加到原始verilog文件和转换后的verilog文件的输入信号上,如图2中步骤203、步骤204以及步骤205所示,接着通过verilog仿真工具基于两个verilog文件分别进行仿真,然后比较两种verilog文件的输出信号的变化。如果两种verilog输出信号的变化完全一致,则可判定转换后的verilog文件和原始的verilog文件等效,即二者功能一致。

52.在本发明的一个或多个实施例中,可根据需求对复杂的verilog进行简化,例如,在执行“从所述verilog文件中获取描述逻辑功能的目标代码”的步骤时,可根据需求提取出verilog文件中的一部分重要的逻辑功能,去除冗余逻辑,以简化设计流程、缩短设计周期。基于此,从所述原始verilog文件中获取描述逻辑功能的目标代码,可包括:从所述原始verilog文件中识别出描述逻辑功能的代码;从识别出的代码中提取出描述目标逻辑功能的所述目标代码。

53.在本发明的一个或多个实施例中,从所述原始verilog文件中识别出描述逻辑功能的代码,可包括:根据所述逻辑功能与用于表示所述逻辑功能的verilog代码的对应关系,从所述原始verilog文件中识别出描述逻辑功能的代码。例如,当原始verilog文件中包括一些用户自定义的功能模块时,可根据配置文件中定义的逻辑功能对应的verilog代码,从原始verilog文件中正确的识别出描述这些自定义的功能模块的代码。

54.在本发明的一个或多个实施例中,上述verilog文件转换方法还可包括:在从所述原始verilog文件中获取描述逻辑功能的目标代码之后,以第二测试激励文件对所述原始verilog文件进行测试,得到第二测试结果;根据所述第二测试结果确定出所述原始verilog文件中包括的目标逻辑功能;根据所述目标逻辑功能确定所述目标代码是否正确。可以为原verilog文件加上对应的测试激励信号,然后通过输出的信号,来判定verilog文件中所包含的逻辑功能。例如,可通过在扫描链输入信号灌入特定的激励,然后观察扫描链的输出信号,从而判定verilog文件中扫描链的信息。

55.图3是根据本发明一个或多个实施例示出的一种verilog文件转换方法的流程图,如图3所示,该方法可包括如下处理:

56.步骤301:准备好原始verilog文件;

57.步骤302:识别原始verilog文件中的逻辑功能描述,并将其转换为主流eda工具(为上述目标eda工具的一个示例)可识别的verilog描述方式,即通用性的verilog文件,并根据识别的逻辑结构生成一套测试激励;

58.步骤303:使用步骤302生成的测试激励文件,分别对原始verilog和通用性verilog进行仿真测试,比较两种verilog文件的输出是否一致,若仿真测试结果中两种

verilog文件的输出信号完全一致,则确定生成的通用性的verilog文件与原始verilog文件等效,反之则二者不等效,二者不等效时返回执行上述步骤302重新转换原始verilog文件;

59.步骤304:在步骤303中生成的通用性verilog文件等效验证通过后,可将生成的通用性的verilog文件应用于后续主流eda工具的设计环节。

60.图4是根据本发明一个或多个实施例示出的一种verilog文件转换装置的结构示意图,如图4所示,装置40可包括:

61.第一获取模块41,被配置为获取原始verilog文件以及配置文件,其中,所述配置文件中包括与目标eda工具对应的目标表述方式的信息;

62.第二获取模块42,被配置为从所述原始verilog文件中获取描述逻辑功能的目标代码;

63.第一转换模块43,被配置为将所述目标代码转换为以所述目标表述方式进行表示,得到转换后的文件;

64.生成模块44,被配置为根据所述目标代码生成第一测试激励文件;

65.第一测试模块45,被配置为根据所述第一测试激励文件分别以所述verilog文件以及所述转换后的文件进行仿真测试,得到第一测试结果;

66.验证模块46,被配置为根据所述第一测试结果,判断所述转换后文件与所述原始verilog文件的功能是否一致。

67.在本发明的一个或多个实施例中,所述第一测试结果中包括以所述原始verilog文件进行仿真测试时仿真工具输出的第一信号,以及以转换后的文件进行仿真测试时,仿真工具输出的第二信号,所述验证模块具体可被配置为:比较所述第一信号与所述第二信号;响应于所述第一信号与所述第二信号一致,确定所述转换后的文件与所述原始verilog文件的功能一致;响应于所述第一信号与所述第二信号不一致,确定所述转换后的文件与所述原始verilog文件的功能不一致。

68.在本发明的一个或多个实施例中,上述verilog文件转换装置还可包括:修改模块,被配置为响应于根据所述第一测试结果判断所述转换后的文件与所述原始verilog文件的功能不一致,修改所述配置文件;第二转换模块,被配置为根据修改后的配置文件重新从所述原始verilog文件中获取描述逻辑功能的目标代码,以及将重新得到的目标代码转换为以所述目标表述方式进行表示,得到重新转换后的文件。

69.在本发明的一个或多个实施例中,所述第二获取模块具体被配置为:从所述原始verilog文件中识别出描述逻辑功能的代码;从识别出的代码中提取出描述目标逻辑功能的所述目标代码。

70.在本发明的一个或多个实施例中,所述配置文件中还可包括:逻辑功能与用于表示所述逻辑功能的verilog代码的对应关系。

71.在本发明的一个或多个实施例中,所述第二获取模块具体可被配置为:根据所述逻辑功能与用于表示所述逻辑功能的verilog代码的对应关系,从所述verilog文件中识别出描述逻辑功能的代码。

72.在本发明的一个或多个实施例中,上述verilog文件转换装置还可包括:第二测试模块,被配置为在从所述原始verilog文件中获取描述逻辑功能的目标代码之后,以第二测

试激励文件对所述原始verilog文件进行测试,得到第二测试结果;第一确定模块,被配置为根据所述第二测试结果确定出所述原始verilog文件中包括的目标逻辑功能;第二确定模块,被配置为根据所述目标逻辑功能确定所述目标代码是否正确。

73.本发明一个或多个实施例还提供了一种电子设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现如上述任意一种verilog文件转换方法。

74.本发明一个或多个实施例提供了一种非暂态计算机可读存储介质,所述非暂态计算机可读存储介质存储计算机指令,所述计算机指令用于使所述计算机执行上述任意一种verilog文件转换方法。

75.图5示出了本发明一个或多个实施例所提供的一种更为具体的电子设备硬件结构示意图,该设备可以包括:处理器510、存储器520、输入/输出接口530、通信接口540和总线550。其中处理器510、存储器520、输入/输出接口530和通信接口540通过总线550实现彼此之间在设备内部的通信连接。

76.处理器510可以采用通用的cpu(central processing unit,中央处理器)、微处理器、应用专用集成电路(application specific integrated circuit,asic)、或者一个或多个集成电路等方式实现,用于执行相关程序,以实现本说明书实施例所提供的技术方案。

77.存储器520可以采用rom(read only memory,只读存储器)、ram(random access memory,随机存取存储器)、静态存储设备,动态存储设备等形式实现。存储器520可以存储操作系统和其他应用程序,在通过软件或者固件来实现本说明书实施例所提供的技术方案时,相关的程序代码保存在存储器520中,并由处理器510来调用执行。

78.输入/输出接口530用于连接输入/输出模块,以实现信息输入及输出。输入输出/模块可以作为组件配置在设备中(图中未示出),也可以外接于设备以提供相应功能。其中输入设备可以包括键盘、鼠标、触摸屏、麦克风、各类传感器等,输出设备可以包括显示器、扬声器、振动器、指示灯等。

79.通信接口540用于连接通信模块(图中未示出),以实现本设备与其他设备的通信交互。其中通信模块可以通过有线方式(例如usb、网线等)实现通信,也可以通过无线方式(例如移动网络、wifi、蓝牙等)实现通信。

80.总线550包括一通路,在设备的各个组件(例如处理器510、存储器520、输入/输出接口530和通信接口440)之间传输信息。

81.需要说明的是,尽管上述设备仅示出了处理器510、存储器520、输入/输出接口530、通信接口540以及总线550,但是在具体实施过程中,该设备还可以包括实现正常运行所必需的其他组件。此外,本领域的技术人员可以理解的是,上述设备中也可以仅包含实现本说明书实施例方案所必需的组件,而不必包含图中所示的全部组件。

82.本实施例的计算机可读介质包括永久性和非永久性、可移动和非可移动媒体可以由任何方法或技术来实现信息存储。信息可以是计算机可读指令、数据结构、程序的模块或其他数据。计算机的存储介质的例子包括,但不限于相变内存(pram)、静态随机存取存储器(sram)、动态随机存取存储器(dram)、其他类型的随机存取存储器(ram)、只读存储器(rom)、电可擦除可编程只读存储器(eeprom)、快闪记忆体或其他内存技术、只读光盘只读存储器(cd

‑

rom)、数字多功能光盘(dvd)或其他光学存储、磁盒式磁带,磁带磁磁盘存储或

其他磁性存储设备或任何其他非传输介质,可用于存储可以被计算设备访问的信息。需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个......”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

83.本说明书中的各个实施例均采用相关的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。

84.尤其,对于装置实施例而言,由于其基本相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例的部分说明即可。

85.为了描述的方便,描述以上装置是以功能分为各种单元/模块分别描述。当然,在实施本发明时可以把各单元/模块的功能在同一个或多个软件和/或硬件中实现。

86.本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以通过计算机程序来指令相关的硬件来完成,所述的程序可存储于一计算机可读取存储介质中,该程序在执行时,可包括如上述各方法的实施例的流程。其中,所述的存储介质可为磁碟、光盘、只读存储记忆体(read

‑

only memory,rom)或随机存储记忆体(randomaccess memory,ram)等。

87.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1