FPGA设计的安全调试的制作方法

fpga设计的安全调试

背景技术:

1.当前处理器可以为诸如安全飞地(secure enclave)的可信执行环境提供支持。安全飞地包括受处理器保护的存储器段(包括代码和/或数据),以防止未经授权的访问,包括未经授权的读取和写入。具体地,某些处理器可以包括software guard extensions(sgx),以提供安全飞地支持。具体地,sgx在安全飞地数据驻留在平台存储器中的同时为数据提供保密性、完整性和回放保护,从而抵御软件和硬件攻击。片上边界形成自然的安全边界,在这里,数据和代码可以以纯文本形式存储并假定为是安全的。

2.现代计算设备可以包括通用处理器核以及用于卸载计算密集型工作负载或执行专门任务的各种硬件加速器。硬件加速器可以包括例如一个或多个现场可编程门阵列(fpga),其可以包括可以由终端用户或系统集成商配置的可编程数字逻辑资源。硬件加速器还可以包括一个或多个专用集成电路(asic)。硬件加速器可以被实现为通过i/o互连与处理器核通信的i/o设备。

3.云服务提供商(csp)向云客户出租硬件,包括现场可编程门阵列(fpga)硬件,以开发硬件(hw)设计或加速在由云服务提供商提供的基础架构上执行的客户工作负载。提供对fpga的访问作为服务的这种模型允许其客户在csp所操作的fpga实例上开发、调试、运行和监视其应用,但同时也引起了各种安全问题。

附图说明

4.本文中描述的概念通过示例的方式示出,而不是作为对附图的限制。为了说明的简单和清楚,附图中示出的元件不一定按比例绘制。在认为合适的情况下,在附图中重复附图标记以指示对应或类似的元件。

5.图1是根据实施例的计算设备的至少一个实施例的简化框图。

6.图2是根据实施例的图1的计算设备的加速器设备的至少一个实施例的简化框图。

7.图3是根据实施例的图1至图2的计算设备的环境的至少一个实施例的简化框图。

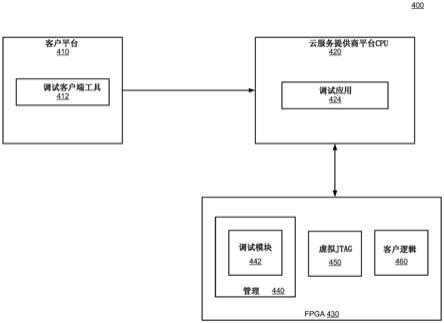

8.图4至图7是根据实施例的可以适于实现用于fpga的安全调试的操作的计算环境的简化框图。

9.图8至图9是根据实施例的示出用于推动fpga的安全调试的方法中的操作的简化流程图。

10.图10是根据实施例的在虚拟化计算环境中提供安全的直接存储器访问事务的设备的组件的示意图。

具体实施方式

11.尽管本公开的概念易于进行各种修改和替代形式,但是其具体实施例已经在附图中通过示例的方式示出,并且将在本文中进行详细描述。然而,应当理解,无意将本公开的概念限制为所公开的特定形式,而是相反,其意图是覆盖与本公开和所附权利要求一致的所有修改、等同形式和替代形式。

12.说明书中对“一个实施例”、“实施例”、“说明性实施例”等的引用表示,所描述的实施例可以包括特定的部件、结构或特点,但是每一个实施例可能或可能不一定包括特定的部件、结构或特点。此外,这样的短语不一定指代相同的实施例。此外,当结合实施例描述特定的部件、结构或特点时,认为结合其他实施例影响这样的部件、结构或特点在本领域技术人员的知识范围内,无论是否明确描述。附加地,应当理解,以“a、b和c中的至少一个”的形式包括在所列内容中的项目可以表示(a);(b);(c);(a和b);(a和c);(b和c);或(a、b和c)。类似地,以“a、b或c中的至少一个”的形式列出的项目可以表示(a);(b);(c);(a和b);(a和c);(b和c);或(a、b和c)。

13.在一些情况下,所公开的实施例可以以硬件、固件、软件或其任何组合来实现。所公开的实施例还可以被实现为由暂时性或非暂时性机器可读(例如,计算机可读)存储介质承载或存储的指令,其可以由一个或多个处理器读取和执行。机器可读存储介质可以被实现为用于以机器可读形式存储或传输信息的任何存储装置、机构或其他物理结构(例如,易失性或非易失性存储器、介质盘或其他介质装置)。

14.在附图中,可以以特定布置和/或顺序示出一些结构或方法特征。然而,应该理解,可能不需要这样的特定布置和/或排序。而是,在一些实施例中,这些特征可以以不同于说明性附图中所示的方式和/或顺序来布置。附加地,在特定图中包含结构或方法特征并不意味着暗示在所有实施例中都需要这样的特征,并且在一些实施例中,可以不包括在内或者可以与其他特征组合。

15.如上所述,一些云服务提供商(csp)向云客户出租硬件,包括现场可编程门阵列(fpga)硬件,以开发硬件(hw)设计或加速在由云服务提供商提供的基础架构上执行的客户工作负载。提供对fpga的访问作为服务的这种模型允许其客户在csp所操作的fpga实例上开发、调试、运行和监视其应用,但同时也引起了各种安全问题。

16.客户对fpga实例的使用分为两大使用类别。第一类包括硬件设计、寄存器传输级(rtl)设计、硬件原型设计和硅前验证的开发。其他实例包括通过将部分工作负载从主机cpu卸载到作为加速器运行的fpga来加速诸如人工智能(ai)和/或机器语言(ml)应用的工作负载。硬件加速逻辑(也称为计算内核)允许客户运行用途特定的逻辑,诸如用于推理用途的深度学习(dk)神经网络。

17.对于这两种使用类别,客户需要对fpga内部的调试接口进行远程访问,以便测试其硬件设计并监视其计算内核的执行。调试功能可以用于识别硬件设计问题或rtl编码错误,以确保其硬件设计按预期运行。客户还可以使用调试探针监视信号和中间状态,以深入了解其计算内核的执行。

18.具有对安全性和隐私敏感的工作负载的云客户可能会担心由于csp的系统软件(os和vmm)的潜在危害而导致其数据和/或知识产权在云平台上的泄漏。对于在云中使用fpga的客户来说,一些主要的安全问题包括:寻找方法来将其比特流编程到远程fpga中,而无需透露代表其ip的设计;寻找方法来防止将其工作负载(例如,数据)从可信执行环境(tee)(诸如sgx)卸载到fpga;以及寻找方法来在不可信csp软件存在的情况下向远程客户端公开调试功能,同时仍保留其资产(诸如fpga设计)的机密性。

19.尽管硬件供应商可以在fpga上提供调试钩挂(debug hook),以使客户能够构建软件解决方案以通过jtag端口监视、更新和调试设计,而无需使用输入/输出(i/o)引脚,但是

大多数现有解决方案都没有限制客户使用调试接口的机制,因此容容易存在客户敏感设计泄漏。本文中描述的主题通过提供如下机制来解决这些问题和其他问题:提供对fpga的调试接口的访问控制,使得客户可以从远程客户端机器调试或监视其在fpga上的比特流,但有助于调试的不可信系统软件无权访问调试过程中生成的调试内容。在一些示例中,可以使用客户的调试应用与fpga调试模块之间的密码协议来提供对fpga调试接口的访问控制。这使客户软件能够监视、更新和调试设计,同时限制有助于调试过程的不可信软件访问明文形式的调试内容或修改中间数据或状态而无需检测。

20.在一个实施方式中,调试加密模块可以位于fpga内部。客户的调试应用可以使用对称密钥来配给调试加密模块。调试加密模块可以与存储器映射io(mmio)内联放置,以访问fpga中的调试寄存器,并且可以加密/解密软件访问的调试数据。

21.在另一实施方式中,调试加密模块可以位于fpga的调试模块内部。在此实施方式中,当软件读取调试数据时,调试模块将调试数据加密,然后再将其写入fpga的调试寄存器。这可以提供更高级别的保护,因为当客户数据离开客户逻辑时,客户数据被加密,从而使其对促进了软件对调试寄存器的读取/写入的csp的管理逻辑不透明。

22.在两种实施方式中,当通过软件读取调试内容时,该内容被加密,并且可选地,可以使用由客户编程的加密密钥(即,对称密钥)进行完整性保护。因此,内容只能由拥有对称密钥的客户调试应用来解密。

23.将参考图1至图10提供用于提供fpga设计的安全调试的结构和技术的更多细节。图1是根据实施例的计算设备的至少一个实施例的简化框图。参考图1,在一些示例中,计算设备100包括处理器120和加速器设备136,诸如现场可编程门阵列(fpga)。在一些示例中,如下文进一步所述,由处理器120建立的可信执行环境(tee)与加速器136安全地进行数据通信。可以使用存储器映射i/o(mmio)事务或直接存储器访问(dma)事务来传送数据。例如,tee可以执行包括加密数据的mmio写入事务,并且加速器136解密数据并执行写入。作为另一示例,tee可以执行mmio读取请求事务,并且加速器136可以读取所请求的数据、加密数据、以及执行包括加密的数据的mmio读取响应事务。在另一示例中,tee可以将加速器136配置为执行dma操作,并且加速器136执行存储器传输,执行密码操作(即,加密或解密),以及转发结果。在一些示例中,tee和加速器136可以为所传输的数据生成认证标签(at),并且可以使用那些at来验证事务。因此,计算设备100可以将计算设备100的不可信软件(诸如操作系统或虚拟机监视器)保持在tee和加速器136的可信代码库(tcb)之外。因此,计算设备100可以确保tee和加速器136从计算设备100的所有者(例如,云服务提供商)或计算设备100的其他租户交换或以其他方式处理的数据。因此,计算设备100可以通过实现加速器的安全使用来提高多租户环境的安全性和性能。

24.计算设备100可以被实现为能够执行本文所述功能的任何类型的装置。例如,计算设备100可以被实现为但不限于计算机、膝上型计算机、平板计算机、笔记本计算机、移动计算设备、智能电话、可穿戴计算设备、多处理器系统、服务器、工作站和/或消费电子设备。如图1所示,示意性计算设备100包括处理器120、i/o子系统124、存储器130和数据存储设备132。附加地,在一些实施例中,一个或多个示意性组件可以结合在另一组件中或以其他方式形成另一组件的一部分。例如,在一些实施例中,存储器130或其部分可以结合在处理器120中。

25.处理器120可以被实现为能够执行本文所述功能的任何类型的处理器。例如,处理器120可以被实现为单核或多核处理器、数字信号处理器、微控制器或其他处理器或处理/控制电路。如图所示,处理器120示意性地包括安全飞地支持122,其允许处理器120建立被称为安全飞地的可信执行环境,在其中可以对执行代码进行测量、验证和/或以其他方式确定为是可靠的。附加地,安全飞地中包括的代码和数据可以被加密或以其他方式被保护,以免被在安全飞地外部执行的代码访问。例如,安全飞地中包括的代码和数据在被执行或存储在处理器120的某些受保护的缓存中时,可以由处理器120的硬件保护机制保护。安全飞地中包括的代码和数据可以在存储在共享缓存或主存储器130中时被加密。安全飞地支持122可以被实现为处理器指令扩展集,允许处理器120在存储器130中建立一个或多个安全飞地。例如,安全飞地支持122可以被实现为software guard extensions(sgx)技术。

26.存储器130可以被实现为能够执行本文所述功能的任何类型的易失性或非易失性存储器或数据存储设备。在操作中,存储器130可以存储在计算设备100的操作期间使用的各种数据和软件,诸如操作系统、应用、程序、库和驱动器。如图所示,存储器130可以经由i/o子系统124通信地耦合至处理器120,该i/o子系统可以被实现为电路和/或组件,以促进与处理器120、存储器130和计算设备100的其他组件的输入/输出操作。例如,i/o子系统124可以被实现为或以其他方式包括存储器控制器中枢、输入/输出控制中枢、传感器中枢、主机控制器、固件设备、通信链路(即,点链接、总线链接、电线、电缆、光导、印刷电路板走线等)和/或其他组件和子系统,以促进输入/输出操作。在一些实施例中,存储器130可以例如经由集成的存储器控制器中枢直接耦合至处理器120。附加地,在一些实施例中,i/o子系统124可以形成片上系统(soc)的一部分,并且与处理器120、存储器130、加速器136和/或计算设备100的其他组件一起结合在单个集成电路芯片上。附加地或替代地,在一些实施例中,处理器120可以包括集成的存储器控制器和系统代理,其可以被实现为逻辑块,其中来自处理器核和i/o设备的数据业务在被发送到存储器130之前汇聚。

27.如图所示,i/o子系统124包括直接存储器访问(dma)引擎126和存储器映射i/o(mmio)引擎128。处理器120,包括与安全飞地支持122一起建立的安全飞地,可以使用dma引擎126与加速器136进行一个或多个dma事务通信和/或使用mmio引擎128与加速器136进行一个或多个mmio事务通信。计算设备100可以包括多个dma引擎126和/或mmio引擎128,用于基于处理器120和加速器136之间的带宽来处理dma和mmio读取/写入事务。尽管被示为包括在i/o子系统124中,但是应当理解,在一些实施例中,dma引擎126和/或mmio引擎128可以包括在计算设备100的其他组件(例如,处理器120、存储器控制器或系统代理)中,或者在一些实施例中,可以被实现为单独的组件。

28.数据存储设备132可以被实现为配置为短期或长期存储数据的任何类型的设备,例如,存储器设备和电路、存储卡、硬盘驱动器、固态驱动器、非易失性闪存或其他数据存储设备。计算设备100还可以包括通信子系统134,其可以被实现为任何通信电路、装置或其集合,能够实现计算设备100和其他远程设备之间在计算机网络(未示出)上的通信。通信子系统134可以被配置为使用任何一种或多种通信技术(例如,有线或无线通信)和相关协议(例如,ethernet、如,ethernet、wimax、3g、4g lte等)来进行这种通信。

29.加速器136可以被实现为现场可编程门阵列(fpga)、专用集成电路(asic)、协处理

器或能够执行加速功能(例如,加速应用功能、加速网络功能或其他加速功能)的其他数字逻辑设备。示意性地,加速器136是fpga,其可以被实现为包括可编程数字逻辑资源的集成电路,该可编程数字逻辑资源可以在制造之后进行配置。fpga可以包括例如通过可配置数据交换进行通信的逻辑块的可配置阵列。加速器136可以经由诸如外围总线(例如,pci express总线)或处理器间互连(例如,芯片内互连(idi)或quickpath互连(qpi))的高速连接接口或经由任何其他适当的互连耦合至处理器120。加速器136可以从处理器120接收待处理的数据和/或命令,并且经由dma、mmio或其他数据传输事务将结果数据返回到处理器120。

30.如图所示,计算设备100还可以包括一个或多个外围设备138。外围设备138可以包括任意数量的附加输入/输出设备、接口设备、硬件加速器和/或其他外围设备。例如,在一些实施例中,外围设备138可以包括触摸屏、图形电路、图形处理单元(gpu)和/或处理器图形、音频设备、麦克风、相机、键盘、鼠标、网络接口和/或其他输入/输出设备、接口设备和/或外围设备。

31.现在参考图2,示出现场可编程门阵列(fpga)200的示意性实施例。如图所示,fpga 200是加速器136的一个潜在实施例。示意性fpga200包括安全mmio引擎202、安全dma引擎204、一个或多个加速器设备206和存储器/寄存器208。如下文进一步所述,安全mmio引擎202和安全dma引擎204对在处理器120(例如,由处理器建立的安全飞地)和fpga 200(例如,一个或多个加速器设备206)之间传输的数据执行在线认证密码操作。在一些实施例中,安全mmio引擎202和/或安全dma引擎204可以在fpga 200的一个或多个缓存一致性互连、内部总线或其他互连上截取、过滤或以其他方式处理数据业务。

32.每个加速器设备206可以被实现为fpga 200的配置为执行加速任务的逻辑资源。每个加速器设备206可以与在安全飞地或其他可信执行环境中由计算设备100执行的应用相关联。每个加速器设备206可以由计算设备100的租户或其他用户配置或以其他方式提供。例如,每个加速器设备206可以对应于被编程到fpga 200的比特流图像。如下文进一步所述,由每个加速器设备206处理的数据,包括与可信执行环境交换的数据,可以进行密码保护,不受计算设备100的不可信组件的影响(例如,不受租户飞地的可信代码库之外的软件影响)。每个加速器设备206可以访问或以其他方式处理存储在存储器/寄存器208中的数据,该存储器/寄存器可以被实现为fpga 200的内部寄存器、缓存、sram、存储设备或其他存储器。在一些实施例中,存储器208还可以包括耦合至fpga 200的外部dram或其他专用存储器。

33.图3是根据实施例的图1至图2的计算设备的环境的至少一个实施例的简化框图。现在参考图3,在示意性实施例中,计算设备100在操作期间建立环境300。示意性环境300包括可信执行环境(tee)302和加速器136。tee 302进一步包括主机加密引擎304、事务分配器306、主机验证器308和直接存储器访问(dma)管理器310。加速器136包括加速器加密引擎312、加速器验证器314、存储器映射器316、认证标签(at)控制器318和dma引擎320。环境300的各种组件可以被实现为硬件、固件、软件或其组合。这样,在一些实施例中,环境300的一个或多个组件可以被实现为电子设备的电路或集合(例如,主机加密引擎电路304、事务分配器电路306、主机验证器电路308、dma管理器电路310、加速器加密引擎电路312、加速器验证器电路314、存储器映射器电路316、at控制器电路318和/或dma引擎电路320)。应当理解,

在这样的实施例中,主机加密引擎电路304、事务分配器电路306、主机验证器电路308、dma管理器电路310、加速器加密引擎电路312、加速器验证器电路314、存储器映射器电路316、at控制器电路318和/或dma引擎电路320中的一个或多个可以形成处理器120、i/o子系统124、加速器136和/或计算设备100的其他组件的一部分。附加地,在一些实施例中,一个或多个示意性组件可以形成另一组件的一部分,和/或一个或多个示意性组件可以彼此独立。

34.tee 302可以被实现为计算设备100的可信执行环境,其使用计算设备100的硬件支持(诸如处理器120的安全飞地支持122)进行认证和保护,以防止未经授权的访问。示意性地,tee 302可以被实现为使用intel sgx技术建立的一个或多个安全飞地。tee 302还可以包括计算设备100的一个或多个驱动器、库或其他组件,或者与之交互,以与加速器136交互。

35.主机加密引擎304被配置为:基于存储器映射i/o(mmio)事务生成认证标签(at)并将该at写入加速器136的at寄存器。对于mmio写入请求,主机加密引擎304还被配置为:对数据项进行加密以生成加密的数据项,并且响应于对数据项进行加密来生成at。对于mmio读取请求,基于与mmio读取请求相关联的地址生成at。

36.事务分配器306被配置为:在将计算出的at写入at寄存器之后,将存储器映射i/o事务(例如,mmio写入请求或mmio读取请求)分配给加速器136。可以将mmio写入请求与加密的数据项一起分配。

37.主机验证器308可以被配置为:响应于分配mmio写入请求而验证mmio写入请求成功。验证mmio写入请求成功可以包括:安全地读取加速器136的状态寄存器,安全地从加速器136读取mmio写入的地址处的值,或者读取加速器136的at寄存器,该at寄存器返回通过加速器136计算出的at值,如下所述。对于mmio读取请求,主机验证器308可以进一步被配置为:基于从加速器136分配的mmio读取响应中包括的加密数据项来生成at;从加速器136的寄存器中读取报告的at;以及确定tee 302生成的at是否与加速器136报告的at相匹配。主机验证器308可以进一步被配置为,如果那些at不匹配,则指示错误,这确保在从tee 302到加速器136的途中没有修改数据。

38.加速器加密引擎312被配置为执行与mmio事务相关联的密码操作,并且响应于mmio事务被分配而基于mmio事务生成at。对于mmio写入请求,密码操作包括:解密从tee 302接收的加密数据项以生成数据项,并且at是基于加密数据项生成的。对于mmio读取请求,密码操作包括:对来自加速器136的存储器的数据项进行加密以生成加密数据项,并且at是基于该加密数据项生成的。

39.加速器验证器314被配置为确定tee 302写入的at是否与加速器136所确定的at匹配。加速器验证器314进一步被配置为,如果那些at不匹配,则丢弃mmio事务。对于mmio读取请求,加速器验证器314可以被配置为响应于丢弃mmio读取请求而生成中毒的at,并且可以进一步被配置为响应于丢弃mmio读取请求而向tee 302分配具有中毒数据项的mmio读取响应。

40.存储器映射器316被配置为响应于确定由tee 302写入的at与由加速器136生成的at匹配来提交mmio事务。对于mmio写入请求,提交事务可以包括:将数据项存储在加速器136的存储器中。存储器映射器316可以进一步被配置为:响应于存储数据项而将状态寄存器设置为指示成功。对于mmio读取请求,提交事务可以包括:读取加速器136的存储器中的

地址处的数据项,并且将具有加密数据项的mmio读取响应分配给tee 302。

41.dma管理器310被配置为:将初始化命令安全地写入加速器136以初始化安全dma传输。dma管理器310进一步被配置为:安全地配置指示主机存储器缓冲器、加速器136缓冲器和传输方向的描述符。传输方向可以是主机到加速器136或加速器136到主机。dma管理器310进一步被配置为:将完成命令安全地写入加速器136,以完成用于安全dma传输的认证标签(at)。初始化命令、描述符和完成命令可以分别被安全地写入和/或配置有mmio写入请求。dma管理器310可以进一步被配置为:响应于安全地配置描述符来确定是否传输附加数据,可以响应于确定没有附加数据要传输来安全地写入完成命令。

42.at控制器318被配置为:响应于来自tee 302的初始化命令而初始化at。at控制器318进一步被配置为:响应于来自tee 302的完成命令来完成at。

43.dma引擎320被配置为:响应于来自tee 302的描述符,在主机存储器缓冲器和加速器136缓冲器之间传输数据。对于从主机到加速器136的传输,传输数据包括从主机存储器缓冲器复制加密数据,并且响应于解密加密的数据而将纯文本数据转发到加速器136缓冲器。对于从加速器136到主机的传输,传输数据包括从加速器136缓冲器复制纯文本数据,并且响应于对纯文本数据进行加密而将加密数据转发到主机存储器缓冲器。

44.加速器加密引擎312被配置为:响应于传输数据而对数据执行密码操作,并且响应于传输数据而更新at。对于从主机到加速器136的传输,执行密码操作包括:解密加密的数据以生成纯文本数据。对于从加速器136到主机的传输,执行密码操作包括:加密纯文本数据以生成加密数据。

45.主机验证器308被配置为:基于安全dma传输来确定预期的at,响应于安全地写入完成命令而从加速器136读取at,并且确定来自加速器136的at是否匹配预期的at。主机验证器308可以进一步被配置为:如果at匹配,则指示成功,如果at不匹配,则指示失败。

46.图4至图7是根据实施例的可以适于实现用于fpga的安全调试的操作的计算环境400的简化框图。图4示出计算环境的高级架构。首先参考图4,在一些示例中,计算环境包括通信耦合至云服务提供商平台cpu 420的客户平台410,该云服务提供商平台cpu 420又通信耦合至fpga 430。在一些示例中,客户平台410托管一个或多个调试客户端工具412,其在客户平台410上执行。云服务提供商平台cpu 420托管调试应用424。fpga 430托管管理模块440,包括调试模块442、虚拟jtag接口450和客户逻辑460,其可以驻留在fpga的合适的计算机可读存储器中。

47.在一些示例中,在云服务提供商平台cpu 420上执行的调试应用424可以经由诸如pcie接口、usb接口或jtag接口的合适的通信接口通信地耦合至fpga 430。调试应用424从fpga 430上的一个或多个调试寄存器中读取或向其写入。调试应用424对在fpga 430上执行的调试模块442进行编程和管理,并在通过网络将调试数据提供给调试客户端工具412之前对调试数据进行格式化。

48.在一些示例中,fpga 430中的一个或多个调试模块442可以探查客户逻辑460并向调试应用424提供调试钩挂。调试模块442中的调试寄存器可供主机软件访问以进行读取和写入。主机软件可以发送读取特定调试向量的请求,或者可以写入值以应用于调试向量。在一些示例中,虚拟jtag模块450使得能够访问客户逻辑460内部的各种调试向量。

49.在一些示例中,在客户平台410上执行的调试客户端工具412经由明确定义的接口

与调试应用424通信,以使客户能够检查或修改其在fpga 430上运行的代码的中间数据和硬件状态。

50.通过高层次概述,在一些示例中,客户可以包括一个或多个硬件供应商提供的调试模块,例如,在编译其用于fpga 430的硬件设计时的信号分接头和/或虚拟jtag接口450。用户可以将比特流编程到fpga430中,例如,在加密应用中使用。然后,客户启动调试客户端工具412,其与云服务平台cpu上的调试应用424通信。调试应用424与fpga 430上的调试模块442交互,其使用虚拟jtag接口450从客户逻辑460中的调试寄存器中读取值。将从客户逻辑中收集的调试数据开放给调试应用424和/或调试客户端工具412。

51.图5提供计算环境400的各种示例的更详细的说明。参考图5,在一些示例中,云服务提供商平台cpu 420可以包括(或通信地耦合至)可信执行环境(tee)422。在这样的实施例中,调试应用424可以驻留在tee 422中。另外,tee 422可以包括证明/密钥配给(akp)模块426。虚拟jtag接口450可以包括在cpu 420和fpga 430之间的mmio路径中通信地耦合至证明/密钥配给模块426的调试加密模块452。客户逻辑460包括多个调试向量,即调试向量1462、调试向量2464、调试向量3466。调试模块442包括一个或多个调试寄存器444。

52.在图5所示的示例中,调试客户端工具412是在客户平台410上执行并通过受保护的网络接口与在云服务提供商平台cpu 420上执行的调试应用424通信的应用。客户可以使用调试客户端工具412来指定fpga430上的哪个ip进行调试,开放哪些调试矢量,等等。调试客户端工具412可以具有图形界面来显示客户请求的调试信息。

53.在一些示例中,调试应用424读取fpga 430中的调试寄存器444,并准备来自调试寄存器444的数据以供调试客户端工具412使用。在图5所示的实施例中,调试应用424驻留在tee 422中,从而可以在从fpga430读取的调试数据上安全地运行。可以假定fpga 430具有信任根,并且能够证明调试应用424。akp模块426从fpga 430获得证明数据并验证fpga430。另外,akp模块426负责将加密密钥(例如,对称密钥)和调试寄存器444的地址范围编程到fpga 430上的调试加密模块452中。这样就确保了调试加密模块452仅在访问调试寄存器444时才执行加密/解密。尽管图5中的akp模块426被示为调试应用424的组件,但是它可以实现为独立的证明和密钥配给服务,该服务由调试应用424调用以证明fpga 430,从而安全地获得fpga配置信息,并代表调试应用424编程共享密钥。

54.在一些示例中,调试加密模块452可以位于fpga 430的静态区域中,使得客户不必将调试加密模块452集成到其硬件设计中。调试加密模块实现调试mmio寄存器444的密码访问控制。在一些示例中,调试寄存器444也可以位于固定位置。在一些示例中,仅当调试内容的完整性很重要时,调试加密模块452才可以实现支持加密的协议。在其他示例中,协议还可以包括发送和验证用于命令和数据的消息认证码(mac)。调试数据完整性受损会导致阻止客户成功调试其设计,与数据泄漏的威胁相比,这可能是较低级别的威胁。在一些示例中,可以用仅调试应用424才知道的共享密钥来对调试加密模块452进行编程。

55.调试模块442将调试寄存器444开放给主机调试客户端工具412。在内部,调试模块442与虚拟jtag模块450通信,该虚拟jtag模块又实现从客户逻辑460读取/写入调试向量462、462、466的机制。

56.图6是计算环境400的另一个示例的示意图。在图6所示的示例中,调试加密模块452可以与客户代码集成在一起,并与虚拟jtag模块450一起编译到客户的设计中。当位于

jtag模块450中时,调试寄存器444中的数据保持加密状态,并且加密/解密发生在下游。

57.图7是计算环境400的另一个示例的示意图。在图7所示的示例中,云服务提供商平台cpu 420不具有tee。在这种情况下,调试应用414在假定安全的客户平台414上执行。在此示例中,调试应用代理428在云服务提供商平台cpu 420上执行,并与客户平台410上的调试应用414通信。调试应用414发送准备好的命令,这些命令用与fpga调试加密模块452共享的密钥加密。调试代理428执行对fpga调试寄存器444的读取和写入。然而,数据由调试应用414加密,并以加密格式通过调试应用代理428。

58.已经描述了适合于实现fpga设计的安全调试的计算环境的各种不同示例,现在将参考图8至图9描述实现fpga设计的安全调试的方法。图8是示出用于实现fpga的安全调试的方法800中的设置操作的流程图。参照图8,在操作810中,akp模块424将证明请求发送至fpga 430。在操作815中,fpga 430接收该请求,并且在操作820中,fpga 430响应于该请求而提供证明数据。在一些示例中,证明数据可以包括fpga制造商id、设备id、一个或多个比特流的标识和度量以及其他元数据。在操作825中,akp模块424使用从fpga 430接收的证明数据来启动验证过程。在一些示例中,可以使用平台外验证服务来执行验证,或者通过与配给到akp模块424的策略进行比较来执行验证。在一些示例中,策略可以指定诸如制造商id、固件版本和比特流度量等的内容。

59.一旦证明被验证,则在操作830中,akp模块424向fpga 430发起对调试寄存器444的存储器地址范围的请求。在操作835中,fpga 430接收该请求,并且在操作840中,fpga向akp模块提供存储器地址范围。

60.在操作845中,akp模块824接收调试寄存器的地址范围,并且在操作850中,akp模块824生成用于与fpga通信的加密密钥(例如,对称密钥对),并将密钥配给到fpga调试fpga 430的调试加密模块452。在一些示例中,可以使用标准协议(例如,带有消息认证码的签名diffie hellman交换)来进行该配给。在操作855中,akp模块824将调试寄存器的存储器地址范围编程到调试加密模块452中,使得仅当mmio请求的目标地址落在调试寄存器的地址范围内时才执行加密/解密。

61.在操作865中,调试加密模块452利用调试客户端工具412发起安全网络会话,其在操作870中往复,从而建立安全网络会话。

62.图9是示出实现fpga的安全调试的方法中的操作的流程图。参考图9,在操作910中,客户平台410上的调试客户端工具412向云服务提供商平台cpu 420上的调试应用424发送对fpga 430的某些调试信息的请求。在操作915中,响应于该请求,调试应用424准备mmio读取请求,对该请求进行加密,并将加密的请求发送至fpga 430。在图5和图7所示的实施例中,该请求可以被发送至调试加密模块452。在图6中描绘的实施例中,该请求可以被发送至调试模块442,该调试模块将其传送到调试加密模块452。

63.在操作920中,调试加密模块452对照调试地址范围检查目标mmio地址,该调试地址范围可以被存储在诸如范围寄存器的存储器位置中。如果目标mmio地址落在调试地址范围内,则在操作925中,调试加密模块452在将读取请求写入调试寄存器444之前对其进行解密。

64.在操作930中,调试寄存器444中命令的存在触发调试加密模块452向虚拟jtag接口450发送请求以从客户逻辑460读取所请求的数据。在操作935中接收到该请求,并且在操

作940中,当数据在调试寄存器444中变得可用时,作为读取响应,调试加密模块452将数据发送到调试应用424。在操作940中,调试加密模块452在将数据发送到调试应用424之前解密数据。

65.在操作945中,调试应用424接收并解密从fpga 430接收的读取数据。可选地,调试应用424可以格式化和/或重构数据。在操作950中,调试应用使用与调试客户端工具412共享的网络加密密钥对数据进行重新加密,并且在操作950中,将数据发送到调试客户端工具412。在操作960中,调试客户端工具412接收读取的数据,并且在操作965中,调试客户端工具可以在用户界面上呈现读取的数据。例如,调试客户端工具412可以在图形用户界面上呈现读取的数据。

66.应当理解,在一些实施例中,图8和图9所示的方法可以被实现为存储在计算机可读介质上的各种指令,其可以由适当的处理电路执行以使一个或多个装置执行相应的方法。计算机可读介质可以被实现为能够由计算设备100读取的任何类型的介质,包括但不限于存储器130、数据存储设备132、固件设备、计算设备100的其他存储器或数据存储设备、计算设备100的外围设备138可读的便携式介质和/或其他介质。

67.因此,参考图1至图7描述的组件和结构以及参考图8至图9描述的方法实现在云计算环境中对fpga器件的安全调试。在虚拟化计算环境中,可以将物理计算设备划分为多个虚拟设备。可以通过操作系统(os)和/或虚拟机管理器(vmm)为在一个或多个cpu上运行的不同用户(即,不同的虚拟机(vm))分派不同的虚拟设备。在虚拟化计算环境中执行的应用依赖于os和vmm来提供对虚拟设备的独占(即,受保护)访问,以便可以与虚拟设备安全地共享应用的机密。在上述用于隔离的各种技术中,计算设备的处理器(即,cpu)可以通过存储器映射输入/输出(mmio)请求来访问设备的存储器。os和/或vmm可以通过将虚拟设备的一部分(或全部)物理存储器地址空间映射到单个vm来管理vm之间的隔离,从而只有一个vm可以访问物理存储器空间的该部分。然而,在一些情况下,应用可以与os或vmm都不具有信任关系,因此应用无法信任os和vmm将不会访问或修改与在物理设备上执行的虚拟设备共享的数据。或者,os或vmm将无法访问分派给其他vm的应用的设备中的物理存储器空间。

68.图10示出可以适用于实现如前所述的各种实施例的示例性计算架构的实施例。在各种实施例中,计算架构1000可以包括或被实施为电子设备的一部分。在一些实施例中,计算架构1000可以代表例如实现上述操作环境的一个或多个组件的计算机系统。在一些实施例中,计算架构1000可以代表实现本文描述的一种或多种技术的数字签名系统的一个或多个部分或组件。实施例在这方面不受限制。

69.如在本技术中所使用的,术语“系统”和“组件”以及“模块”旨在指代与计算机相关的实体,其可以是硬件、硬件和软件的组合、软件或执行中的软件,其示例由示例性计算架构1000提供。例如,组件可以是但不限于在处理器上运行的进程、处理器、硬盘驱动器、(光和/或磁存储介质的)多个存储驱动器、对象、可执行文件、执行线程、程序和/或计算机。举例来说,运行在服务器上的应用和服务器可以是组件。一个或多个组件可以驻留在进程和/或执行线程中,并且组件可以位于一台计算机上和/或分布在两台或多台计算机之间。此外,组件可以通过各种类型的通信介质彼此通信耦合以协调操作。协作可以涉及信息的单向或双向交换。例如,组件可以以在通信介质上传送的信号的形式传送信息。该信息可以被实施为分配给各种信号线的信号。在这种分配中,每个消息都是信号。然而,其他实施例可

以替代地采用数据消息。可以通过各种连接发送这种数据消息。示例性连接包括并行接口、串行接口和总线接口。

70.计算架构1000包括各种通用计算元件,例如一个或多个处理器、多核处理器、协处理器、存储器单元、芯片组、控制器、外围设备、接口、振荡器、定时设备、视频卡、音频卡、多媒体输入/输出(i/o)组件、电源等。然而,实施例不限于计算架构1000的实施方式。

71.如图10所示,计算架构1000包括一个或多个处理器1002和一个或多个图形处理器1008,并且可以是单处理器台式机系统、多处理器工作站系统或具有大量处理器1002或处理器核1007的服务器系统。在一个实施例中,系统1000是结合在片上系统(soc或soc)集成电路内的处理平台,以供在移动、手持或嵌入式设备中使用。

72.系统1000的实施例可以包括或结合在基于服务器的游戏平台、包括游戏和媒体控制台的游戏控制台、移动游戏控制台、手持游戏控制台或在线游戏控制台中。在一些实施例中,系统1000是移动电话、智能电话、平板计算设备或移动互联网设备。数据处理系统1000还可以包括可穿戴设备,与可穿戴设备耦合或集成在可穿戴设备中,诸如智能手表可穿戴设备、智能眼镜设备、增强现实设备或虚拟现实设备。在一些实施例中,数据处理系统1000是电视或机顶盒设备,其具有一个或多个处理器1002以及由一个或多个图形处理器1008生成的图形界面。

73.在一些实施例中,一个或多个处理器1002各自包括一个或多个处理器核1007以处理指令,该指令在被执行时执行针对系统和用户软件的操作。在一些实施例中,一个或多个处理器核1007中的每一个被配置为处理特定指令集1009。在一些实施例中,指令集1009可以促进复杂指令集计算(cisc)、精简指令集计算(risc)或通过超长指令字(vliw)进行的计算。多个处理器核1007可以各自处理不同的指令集1009,该指令集可以包括促进仿真其他指令集的指令。处理器核1007还可以包括其他处理设备,诸如数字信号处理器(dsp)。

74.在一些实施例中,处理器1002包括缓存存储器1004。根据架构,处理器1002可以具有单个内部缓存或多级内部缓存。在一些实施例中,处理器1002的各个组件之间共享缓存存储器。在一些实施例中,处理器1002还使用外部缓存(例如,三级(l3)缓存或最后一级缓存(llc))(未示出),其可以使用已知的缓存一致性技术在处理器核1007之间共享。寄存器堆1006附加地包括在处理器1002中,其可以包括用于存储不同类型的数据的不同类型的寄存器(例如,整数寄存器、浮点寄存器、状态寄存器和指令指针寄存器)。一些寄存器可以是通用寄存器,而其他寄存器可以特定于处理器1002的设计。

75.在一些实施例中,一个或多个处理器1002与一个或多个接口总线1010耦合,以在处理器1002与系统中的其他组件之间传输通信信号,诸如地址、数据或控制信号。在一个实施例中,接口总线1010可以是处理器总线,诸如直接媒体接口(dmi)总线的版本。然而,处理器总线不限于dmi总线,并且可以包括一个或多个外围组件互连总线(例如,pci、pci express)、存储器总线或其他类型的接口总线。在一个实施例中,处理器1002包括集成存储器控制器1016和平台控制器中枢1030。存储器控制器1016促进存储器设备与系统1000的其他组件之间的通信,而平台控制器中枢(pch)1030提供通过本地i/o总线连接到i/o设备。

76.存储器设备1020可以是动态随机存取存储器(dram)设备、静态随机存取存储器(sram)设备、闪存设备、相变存储器设备或具有适当性能以用作过程存储器的一些其他存储器设备。在一个实施例中,存储器设备1020可以用作系统1000的系统存储器,以存储数据

1022和指令1021,以在一个或多个处理器1002执行应用或处理时使用。存储器控制器中枢1016还与可选的外部图形处理器1012耦合,该外部图形处理器可以与处理器1002中的一个或多个图形处理器1008通信以执行图形和媒体操作。在一些实施例中,显示设备1011可以连接到处理器1002。显示设备1011可以是如在移动电子设备或膝上型设备中的内部显示设备,或者是经由显示器接口(例如,displayport等)连接的外部显示设备中的一个或多个。在一个实施例中,显示设备1011可以是头戴式显示器(hmd),诸如用于虚拟现实(vr)应用或增强现实(ar)应用中的立体显示设备。

77.在一些实施例中,平台控制器中枢1030使外围设备能够经由高速i/o总线连接到存储器设备1020和处理器1002。i/o外围设备包括但不限于音频控制器1046、网络控制器1034、固件接口1028、无线收发器1026、触摸传感器1025、数据存储设备1024(例如,硬盘驱动器、闪存等)。数据存储设备1024可以经由存储设备接口(例如,sata)或经由外围总线(诸如,外围组件互连总线(例如,pci、pci express))来连接。触摸传感器1025可以包括触摸屏传感器、压力传感器或指纹传感器。无线收发器1026可以是wi

‑

fi收发器、蓝牙收发器或诸如3g、4g或长期演进(lte)收发器的移动网络收发器。固件接口1028实现与系统固件的通信,并且可以是例如统一的可扩展固件接口(uefi)。网络控制器1034可以实现到有线网络的网络连接。在一些实施例中,高性能网络控制器(未示出)与接口总线1010耦合。在一个实施例中,音频控制器1046是多通道高清音频控制器。在一个实施例中,系统1000包括可选的传统i/o控制器1040,用于将传统(例如,个人系统2(ps/2))设备耦合到系统。平台控制器中枢1030还可以连接到一个或多个通用串行总线(usb)控制器1042,该控制器连接输入设备,诸如键盘和鼠标1043组合、相机1044或其他usb输入设备。

78.示例

79.下面提供本文公开的技术的说明性示例。技术的实施例可以包括以下描述的示例中的任何一个或多个以及它们的任意组合。

80.示例1包括一种装置,该装置包括:加速器设备,包括促进加速远程处理设备上可执行的处理工作负载的处理电路;计算机可读存储器,用于存储加速器设备上可执行的逻辑操作;以及调试模块,包括存储加速器设备上可执行的逻辑操作的调试数据的一个或多个调试寄存器以及处理电路,该处理电路从远程处理设备上的调试应用接收指向一个或多个调试寄存器中的目标调试寄存器的存储器访问请求,对目标调试寄存器中的调试数据进行加密以生成加密的调试数据,以及将加密的调试数据返回到调试应用。

81.示例2包括示例1的主题,进一步包括至少一个范围寄存器,用于存储一个或多个调试寄存器的存储器地址范围。

82.示例3包括示例1

‑

2中任何一个的主题,其中,调试寄存器驻留在设备的静态存储器位置中。

83.示例4包括示例1

‑

3中任何一个的主题,调试模块包括处理电路,该处理电路用于从调试应用接收证明请求;以及响应于该证明请求,将证明数据返回到调试应用。

84.示例5包括示例1

‑

4中任何一个的主题,进一步包括处理电路,该处理电路从调试应用接收对一个或多个调试寄存器的地址范围的请求;以及响应于该请求,将一个或多个调试寄存器的地址范围返回到调试应用。

85.示例6包括示例1

‑

5中任何一个的主题,调试模块包括处理电路,该处理电路从调

试应用接收加密密钥;以及将加密密钥存储在安全存储器位置中。

86.示例7包括示例1

‑

6中任何一个的主题,调试模块包括处理电路,该处理电路使用加密密钥与客户端平台建立安全的网络会话。

87.示例8包括示例1

‑

7中任何一个的主题,调试模块还包括联合测试工作组(jtag)接口。

88.示例9是基于计算机的方法,包括:在装置的调试模块的一个或多个调试寄存器中存储用于加速器设备上可执行的逻辑操作的调试数据;从远程处理设备上的调试应用接收指向一个或多个调试寄存器中的目标调试寄存器的存储器访问请求;对目标调试寄存器中的调试数据进行加密以生成加密的调试数据;以及将加密的调试数据返回到调试应用。

89.示例10包括示例9的主题,进一步包括:在至少一个范围寄存器中存储一个或多个调试寄存器的存储器地址范围。

90.示例11包括示例9

‑

10中任何一个的主题,进一步包括:从调试应用接收证明请求;以及响应于该证明请求,将证明数据返回到调试应用。

91.示例12包括示例9

‑

11中任何一个的主题,进一步包括:从调试应用接收对一个或多个调试寄存器的地址范围的请求;以及响应于该请求,将一个或多个调试寄存器的地址范围返回到调试应用。

92.示例13包括示例9

‑

12中任何一个的主题,进一步包括:从调试应用接收对一个或多个调试寄存器的地址范围的请求;以及响应于该请求,将一个或多个调试寄存器的地址范围返回到调试应用。

93.示例14包括示例9

‑

13中任何一个的主题,进一步包括使用加密密钥与客户端平台建立安全的网络会话。

94.示例15包括一个或多个计算机可读存储介质,包括存储在其上的多个指令,该指令响应于被执行而使计算设备:在装置的调试模块的一个或多个调试寄存器中存储用于加速器设备上可执行的逻辑操作的调试数据;从远程处理设备上的调试应用接收指向一个或多个调试寄存器中的目标调试寄存器的存储器访问请求;对目标调试寄存器中的调试数据进行加密以生成加密的调试数据;以及将加密的调试数据返回到调试应用。

95.示例16包括示例15的主题,进一步包括存储在其上的多个指令,该指令响应于被执行而使计算设备:在至少一个范围寄存器中存储一个或多个调试寄存器的存储器地址范围。

96.示例17包括示例15

‑

16中任何一个的主题,进一步包括存储在其上的多个指令,该指令响应于被执行而使计算设备:从调试应用接收证明请求;以及响应于该证明请求,将证明数据返回到调试应用。

97.示例18包括示例16

‑

17中任何一个的主题,进一步包括存储在其上的多个指令,该指令响应于被执行而使计算设备:从调试应用接收对一个或多个调试寄存器的地址范围的请求;以及响应于该请求,将一个或多个调试寄存器的地址范围返回到调试应用。

98.示例19包括示例16

‑

18中任何一个的主题,进一步包括存储在其上的多个指令,该指令响应于被执行而使计算设备:从调试应用接收对一个或多个调试寄存器的地址范围的请求;以及响应于该请求,将一个或多个调试寄存器的地址范围返回到调试应用。

99.示例20包括示例16

‑

19中任何一个的主题,进一步包括存储在其上的多个指令,该

指令响应于被执行而使计算设备使用加密密钥与客户端平台建立安全的网络会话。

100.以上详细描述包括对形成详细描述的一部分的附图的参考。作为说明,附图示出可以实践的具体实施例。这些实施例在本文中也被称为“示例”。这样的示例可以包括除了所示或所述的那些之外的元件。然而,也可以设想包括所示或所述元件的示例。此外,还可以设想使用关于特定示例(或其一个或多个方面)或关于本文所示或所述的其他示例(或其一个或多个方面)所示或所述的那些元件(或其一个或多个方面)的任何组合或置换的示例。

101.本文中涉及的出版物、专利和专利文件通过引用整体并入本文,如同单独通过引用并入。如果本文件与通过引用并入的那些文件之间的用法不一致,则所并入的参考文献中的用法是对本文件的用法的补充;对于不可调和的不一致,以本文件中的用法为准。

102.在本文件中,如在专利文件中常见的那样,使用词语“一”或“一个”来包括一个或一个以上,独立于“至少一个”或“一个或多个”的任何其他实例或用法。另外,“...集”包括一个或多个元素。除非另有说明,否则在本文中,词语“或”用于指非排他性,或者使得“a或b”包括“a,而非b”、“b,而非a”以及“a和b”。在所附权利要求中,词语“包括”和“其中”用作相应词语“包含”和“在其中”的等同用语。而且,在所附权利要求中,词语“包括”和“包含”是开放式的;即,包括除权利要求中的这样的词语之后列出的要素之外的系统、设备、物品或处理仍然被认为落入该权利要求的范围内。此外,在所附权利要求中,词语“第一”、“第二”、“第三”等仅被用作标注,并不旨在暗示其对象的数字顺序。

103.如本文所指,术语“逻辑指令”涉及可以由一个或多个机器理解的表达以用于执行一个或多个逻辑操作。例如,逻辑指令可以包括可由处理器编译器解释的指令以在一个或多个数据对象上执行一个或多个操作。然而,这仅是机器可读指令的示例,并且示例在这方面不受限制。

104.如本文所指,术语“计算机可读介质”涉及能够维持一个或多个机器可理解的表达的介质。例如,一种计算机可读介质可以包括用于存储计算机可读指令或数据的一个或多个存储装置。这样的存储装置可以包括例如光、磁或半导体存储介质的存储介质。然而,这仅是计算机可读介质的示例,并且示例在这方面不受限制。

105.本文所指的术语“逻辑”涉及用于执行一个或多个逻辑操作的结构。例如,逻辑可以包括基于一个或多个输入信号提供一个或多个输出信号的电路。这样的电路可以包括接收数字输入并提供数字输出的有限状态机,或者包括响应于一个或多个模拟输入信号而提供一个或多个模拟输出信号的电路。可以在专用集成电路(asic)或现场可编程门阵列(fpga)中提供这种电路。而且,逻辑可以包括存储在存储器中的机器可读指令,其与执行这种机器可读指令的处理电路相结合。然而,这些仅仅是可以提供逻辑的结构的示例,并且示例在这方面不受限制。

106.本文描述的一些方法可以被实现为计算机可读介质上的逻辑指令。当在处理器上执行时,逻辑指令使处理器被编程为实现所述方法的专用机器。当处理器由逻辑指令配置为执行本文描述的方法时,该处理器构成用于执行所描述的方法的结构。替代地,本文描述的方法可以被简化为例如现场可编程门阵列(fpga)、专用集成电路(asic)等上的逻辑。

107.在说明书和权利要求中,可以使用术语“耦合”和“连接”以及它们的派生词。在特定示例中,“连接”可以用于指示两个或更多个元件彼此直接物理或电接触。“耦合”可以意

味着两个或更多个元件直接物理或电接触。然而,“耦合”还可以意味着两个或更多个元件可能彼此不直接接触,但仍然可以彼此协作或相互作用。

108.说明书中对“一个示例”或“一些示例”的引用意味着结合该示例描述的特定特征、结构或特点包括在至少一个实施方式中。说明书中各处出现的短语“在一个示例中”可能或可能不全是指同一个示例。

109.以上描述旨在是说明性的而不是限制性的。例如,上述示例(或其一个或多个方面)可以与其他示例组合使用。例如本领域的普通技术人员在查看以上描述时,可以使用其他实施例。摘要是为了让读者快速确定技术公开的性质。提交时的理解是,它不会被用来解释或限制权利要求的范围或含义。而且,在上面的详细描述中,各种特征可以组合在一起以简化本公开。然而,权利要求可能没有阐述本文公开的每个特征,这是因为实施例可能以所述特征的子集为特征。此外,实施例可以包括比在特定示例中公开的那些更少的特征。因此,在此所附的权利要求包括在具体实施方式中,其中每一项权利要求都可以基于其本身,作为单独实施例。本文公开的实施例的范围将参考所附权利要求以及这些权利要求的等同物的全部范围来确定。

110.虽然已经以结构特征和/或方法步骤专用的语言描述了示例,但是应当理解,所要求保护的主题可能不限于所描述的具体特征或步骤。相反,具体特征和步骤作为实施所要求保护的主题的示例形式被公开。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1