一种基于FPGA的信号处理系统的制作方法

一种基于fpga的信号处理系统

技术领域

[0001]

本实用新型涉及通信领域,特别是涉及一种基于fpga的信号处理系统。

背景技术:

[0002]

数据采集和控制系统是对生产过程或科学实验中各种物理量进行实时采集、测试和反馈控制的闭环控制,它在工业控制、军事电子设备、医学监护等许多领域发挥着重要作用。因此基于fpga设计开发的各种数据采集系统应运而出,但是目前市面上基于fpga的数据采集系统,都是偏向于以fpga为中心的设计思路,缺少配套的外围数据处理机制,或许由于pfga开发难度高,也可能由于fpga成本大,因此很少有一整套基于fpga设计的完整的信号处理系统。

[0003]

现有基于fpga开发的各种数据处理板卡配套的处理系统不是很完善,存在以下缺点:采集速率较低、多通道处理能力不够强、数据批量传输效率略低、后端数据处理功能不完善等。

技术实现要素:

[0004]

本实用新型主要解决的技术问题是提供一种基于fpga的信号处理系统,通过采用以fpga为数据采集核心、以pcie接口为数据传输通道、以pc端上位机为数据分析处理中心的三大框架来实现信号处理系统,可以实现对输入多通道中频模拟信号的数字化接收、处理、干扰识别与抑制,波形优化设计,模拟中频信号产生等功能,优化数据传输通道,提高大批量数据传输的能力,在基于fpga的信号处理系统的普及上有着广泛的市场前景。

[0005]

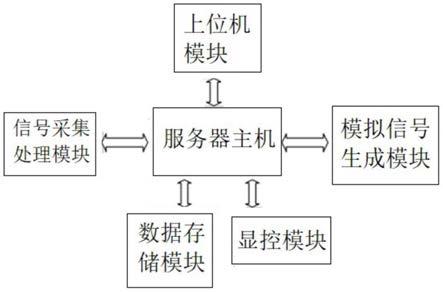

为解决上述技术问题,本实用新型提供一种基于fpga的信号处理系统,包括:服务器主机、信号采集处理模块、模拟信号生成模块、数据存储模块、上位机模块和显控模块,所述信号采集处理模块、模拟信号生成模块、数据存储模块、上位机模块、显控模块分别通信连接所述服务器主机,

[0006]

所述信号采集处理模块、所述模拟信号生成模块均为fpga芯片,所述fpga芯片包括ad子板和pcie板,其中所述ad子板完成adc模块的初始化配置,所述pcie板完成ddc处理器、ddr3控制器、dma控制器、pcie控制器的逻辑和数据的解析和打包,

[0007]

数据经过所述信号采集处理模块的所述ad子板采集后,经过fmc接口传入所述信号采集处理模块的所述pcie板里对ad采样后数据进行降采样、滤波、脉冲压缩处理,然后存储在所述信号采集处理模块的ddr3控制器中,相应的数据再通过pcie总线以dma传输模式传送给所述上位机模块,

[0008]

在本实用新型一个较佳实施例中,所述基于fpga的信号处理系统包括扩展模块,所述扩展模块通信连接所述服务器主机。

[0009]

在本实用新型一个较佳实施例中,所述adc模块的初始化配置包括adc采样时钟的配置、adc采样芯片的配置。

[0010]

在本实用新型一个较佳实施例中,所述ddc处理器包括数字正交本振信号产生器、

混频器、fir滤波器、二选一抽选器。

[0011]

在本实用新型一个较佳实施例中,所述上位机模块包括数字化接收处理单元、数据预处理单元、干扰智能识别单元、波形优化设计单元、抗干扰处理单元、模拟信号产生单元、通信与传输单元、本地控制与显示单元和数据存储单元。

[0012]

在本实用新型一个较佳实施例中,所述显控模块包括板卡状态信息单元、log日志单元、主工作区单元,其中所述板卡状态信息单元显示板卡的状态信息,所述log日志单元显示配置信息、配置结果、调试信息,所述主工作区单元包括参数配置单元、实时处理单元和脱机处理单元。

[0013]

本实用新型的有益效果是:本实用新型基于fpga的信号处理系统通过采用以fpga为数据采集核心、以pcie接口为数据传输通道、以pc端上位机为数据分析处理中心的三大框架来实现信号处理系统,可以实现对输入多通道中频模拟信号的数字化接收、处理、干扰识别与抑制,波形优化设计,模拟中频信号产生等功能,优化数据传输通道,提高大批量数据传输的能力,在基于fpga的信号处理系统的普及上有着广泛的市场前景。

附图说明

[0014]

为了更清楚地说明本实用新型实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图,其中:

[0015]

图1是本实用新型的基于fpga的信号处理系统一较佳实施例的结构示意图;

[0016]

图2是本实用新型的基于fpga的信号处理系统一较佳实施例的信号采集处理模块的处理原理示意图;

[0017]

图3是本实用新型的基于fpga的信号处理系统一较佳实施例的数据存储模块的数据存储原理图;

[0018]

图4是本实用新型的基于fpga的信号处理系统一较佳实施例的上位机模块的组成结构示意图;

[0019]

图5是本实用新型的基于fpga的信号处理系统一较佳实施例的上位机模块的数据处理原理示意图。

具体实施方式

[0020]

下面将对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本实用新型的一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本实用新型保护的范围。

[0021]

请参阅图1-图5,本实用新型实施例包括:

[0022]

一种基于fpga的信号处理系统,包括:服务器主机、信号采集处理模块、模拟信号生成模块、数据存储模块、上位机模块和显控模块。

[0023]

所述信号采集处理模块、模拟信号生成模块、数据存储模块、上位机模块、显控模块分别通信连接所述服务器主机,

[0024]

所述信号采集处理模块、所述模拟信号生成模块均为fpga芯片,所述fpga芯片包括ad子板和pcie板,其中所述ad子板完成adc模块的初始化配置,所述pcie板完成ddc处理器、ddr3控制器、dma控制器、pcie控制器的逻辑和数据的解析和打包,

[0025]

数据经过所述信号采集处理模块的所述ad子板采集后,经过fmc接口传入所述信号采集处理模块的所述pcie板里对ad采样后数据进行降采样、滤波、脉冲压缩处理,然后存储在所述信号采集处理模块的ddr3控制器中,相应的数据再通过pcie总线以dma传输模式传送给所述上位机模块,

[0026]

优选地,所述基于fpga的信号处理系统包括扩展模块,所述扩展模块通信连接所述服务器主机。

[0027]

优选地,所述adc模块的初始化配置包括adc采样时钟的配置、adc采样芯片的配置。

[0028]

优选地,所述ddc处理器包括数字正交本振信号产生器、混频器、fir滤波器、二选一抽选器。

[0029]

优选地,所述上位机模块包括数字化接收处理单元、数据预处理单元、干扰智能识别单元、波形优化设计单元、抗干扰处理单元、模拟信号产生单元、通信与传输单元、本地控制与显示单元和数据存储单元。

[0030]

优选地,所述显控模块包括板卡状态信息单元、log日志单元、主工作区单元,其中所述板卡状态信息单元显示板卡的状态信息,所述log日志单元显示配置信息、配置结果、调试信息,所述主工作区单元包括参数配置单元、实时处理单元和脱机处理单元。

[0031]

图2所示是所述信号采集处理模块的处理原理示意图。在ddc中,输入采样数据与正交混频器(nco)的输出进行混频,对混频之后的实部和虚部分别进行fir滤波、2选1的采样抽选,输出采样频率为输出采样频率的1/2,即100mhz。将抽选之后的数据以脉冲周期为单位进行缓存,但缓存的数据量包括下一个信号周期的前一个脉冲宽度的采样数据。脉冲压缩处理器采用相关法,利用快速算法(快速傅里叶变换)实现,快速傅里叶变换点数(采样基2算法):8192;(1)计算一个脉冲宽度内调频脉冲基带采样(记为c)共轭的离散傅里叶变换(点数8192),记为c_fft,c_fft是初始化系数。系统波形参数不变,该系数不变;(2)对输入信号(ddc输出)数据截取长度为:单信号周期内信号采样点数+单脉冲宽度内信号采样点数,6000点,该序列记为x,对x进行离散傅里叶变换(点数8192)记为x_fft;(3)对c_fft和x_fft的乘机进行点数8192的逆离散傅里叶变换,并取前5000,就是前5000个距离门的处理结果。

[0032]

图3所示是所述数据存储模块的数据存储原理图。处理流程如下:

[0033]

处理流程如下:

[0034]

(1)pc开辟2gb内存,驱动分配2块连续1gb内存空间aa和bb;

[0035]

(2)驱动配置aa的起始地址和长度给fpga,配置bb的起始地址和长度给fpga;

[0036]

(3)fpga等待外部sma给出的启动数据传输信号,上升沿有效(启动脉冲高电平不少于1us)。当检测启动信号有效后,fpga内部启动pcie dma,主动写数据到aa内存空间;

[0037]

(4)fpga完成aa内存空间写操作后,发起中断给驱动;

[0038]

(5)驱动收到中断后,读取fpga内部寄存器,获取数据在aa内存空间,驱动处理aa内存空间数据;

[0039]

(6)fpga监测到有数据需要传输时,主动写数据到bb内存空间

[0040]

(7)fpga完成bb内存空间写操作后,发起中断给驱动;

[0041]

(8)驱动收到中断后,读取fpga内部寄存器,获取数据在bb内存空间,驱动处理bb内存空间数据;

[0042]

重复(3)-(8)步骤操作;

[0043]

(9)收到驱动停止命令,判断当前dma是否传输完成,如果没有完成,则传输完成后发送一次中断后停止数据传输;

[0044]

(10)等待新的传输触发命令,重复步骤(3)-(10)。

[0045]

图4所示是所述上位机模块的组成结构示意图。各个单元的主要任务如下:

[0046]

(1)数字化接收处理单元:完成多通道高速中频信号采集、宽带实时正交化处理、数字信号下变频处理;

[0047]

(2)数据预处理单元:完成采集数字信号的各种预处理,如脉冲压缩、各种变换、归一化处理等;

[0048]

(3)干扰智能识别单元:采用机器学习算法实现对干扰类型的智能识别;

[0049]

(4)波形优化设计单元:根据识别的干扰类型优化设计和选择信号波形;

[0050]

(5)抗干扰处理单元:实现干扰信号抑制、抗干扰决策等抗干扰处理;

[0051]

(6)模拟信号产生单元:根据设计的干扰对抗波形产生相应的模拟中频信号;

[0052]

(7)通信与传输单元:完成信号处理机内部模块之间以及信号处理机与外部接口的通信与数据传输;

[0053]

(8)本地控制与显示单元:完成信号处理机的各项控制与显示功能;

[0054]

(9)数据存储单元:完成对采集和处理后的各种数据的存储与记录。

[0055]

图5所示是所述上位机模块的数据处理原理示意图。可以看出,除了本地控制与数据存储外,其他模块是一种基于数据信号流水线处理框架。上一级的处理不结束,下一级的处理不会开始。这样的流水线结构便于实现,可靠性高,同时便于故障的定位和处理。

[0056]

本实用新型基于fpga的信号处理系统的有益效果是:

[0057]

通过采用以fpga为数据采集核心、以pcie接口为数据传输通道、以pc端上位机为数据分析处理中心的三大框架来实现信号处理系统,可以实现对输入多通道中频模拟信号的数字化接收、处理、干扰识别与抑制,波形优化设计,模拟中频信号产生等功能,优化数据传输通道,提高大批量数据传输的能力。

[0058]

以上所述仅为本实用新型的实施例,并非因此限制本实用新型的专利范围,凡是利用本实用新型说明书内容所作的等效结构或等效流程变换,或直接或间接运用在其它相关的技术领域,均同理包括在本实用新型的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1