用于在微控制器中提供有限利用运行时间应用控制的系统的制作方法

用于在微控制器中提供有限利用运行时间应用控制的系统

背景技术:

1.计算装置用于从天气预报到娱乐的多种有用任务。许多此类任务由处理器装置执行,该处理器装置执行存储在存储器装置上的代码和/或访问存储在此类存储器装置上的其它数据。有用的计算产品(例如,计算机程序、媒体文件等)的开发者可能无法有效地将其创作货币化,因为一旦计算产品存储在存储器装置上,通信地耦合到该存储器装置的处理器装置就可对该计算产品具有无限的访问权限。

技术实现要素:

2.根据本公开,一种设备包括微控制器,该微控制器与存储器装置集成并且适于通信地耦合到处理器装置。微控制器控制处理器对存储器装置的访问。微控制器基于同样存储在存储器装置中的授权数据来设置对存储在该存储器装置中的受控数据的访问权限。微控制器基于这些访问权限响应来自处理器的存储器访问请求。授权数据包括每个受控数据项的条目。授权数据中的每个条目包括相应受控数据项的数据标识符(例如,存储器地址)和使用日志。使用日志指示与受控数据项相关联的限制。例如,访问日志可存储对受控数据的访问计数和最大允许访问次数,或者使用日志可存储经过的访问时间(例如,与对受控数据的访问相关联)和授予访问持续时间。因此,微控制器可对受控数据强制执行基于时间和/或基于访问计数的限制。由于处理器通过微控制器访问存储器装置而不是直接访问存储器装置,因此可防止在处理器上执行的软件规避限制。因此,计算产品的开发者可能够更有效地对其产品设置访问控制。因此,开发者可更能有效地将对其产品的访问货币化。

3.一种设备包括存储器装置和与该存储器装置集成的微控制器装置。微控制器装置适于通信地耦合到处理器装置,并且被配置为管理该处理器装置对存储在存储器装置上的数据的访问。管理处理器装置对存储在存储器装置上的数据的访问包括基于存储在该存储器装置中的授权数据来设置对该存储器装置存储的受控数据的访问权限。管理处理器装置的访问进一步包括从该处理器装置接收访问受控数据的请求。管理处理器装置的访问进一步包括基于访问权限确定是否发起该处理器装置对受控数据的访问。

4.一种方法包括在集成到存储器装置中的微控制器装置处管理处理器装置对存储在该存储器装置上的数据的访问。管理处理器装置对存储在存储器装置上的数据的访问包括基于存储在该存储器装置中的授权数据来设置对该存储器装置存储的受控数据的访问权限。管理处理器装置对存储在存储器装置上的数据的访问进一步包括从该处理器装置接收访问受控数据的请求。管理处理器装置对存储在存储器装置上的数据的访问进一步包括基于访问权限确定是否发起该处理器装置对受控数据的访问。

5.一种计算机可读存储装置存储可由一或多个处理器执行的指令,以在集成到存储器装置中的微控制器装置处管理处理器装置对存储在该存储器装置上的数据的访问。管理处理器装置对存储在存储器装置上的数据的访问包括基于存储在该存储器装置中的授权数据来设置对该存储器装置存储的受控数据的访问权限。管理处理器装置对存储在存储器装置上的数据的访问进一步包括从该处理器装置接收访问受控数据的请求。管理处理器装

置对存储在存储器装置上的数据的访问进一步包括基于访问权限确定是否发起该处理器装置对受控数据的访问。

附图说明

6.对于各种实例的详细描述,现在将参考附图,其中:

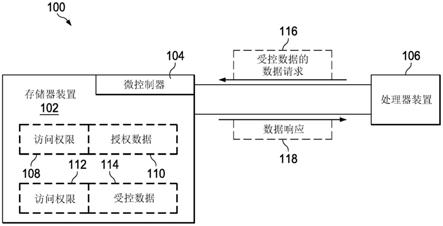

7.图1示出了用于控制对存储在存储器装置上的受控数据的访问的系统。

8.图2示出了其中存储器装置进一步存储通用数据的实例

9.图3示出了其中访问权限和授权数据存储在与存储器装置不同的第二存储器装置上的实例。

10.图4示出了其中示出了授权数据的实例的系统的实例。

11.图5示出了其中授权数据包括与受控数据相关联的基于时间的限制的系统的实例。

12.图6示出了其中授权数据包括与受控数据相关联的基于访问计数的限制的系统的实例。

13.图7示出了其中存储器装置存储多个受控数据项的系统的实例。

14.图8示出了其中存储器装置包括中断机制的系统的实例。

15.图9示出了用于基于访问时间来控制对存储在存储器装置上的受控数据的访问的方法。

16.图10示出了用于基于访问计数来控制对存储在存储器装置上的受控数据的访问的方法。

17.图11是可集成到存储器装置中以控制对存储在该存储器装置上的受控数据的访问的计算装置的框图。

具体实施方式

18.参考图1,示出了用于限制对存储器装置上的数据的访问的系统100。系统100包括存储器装置102和处理器装置106。存储器装置102可对应于闪存装置、硬盘驱动器、另一种类型的存储器装置或其组合。处理器装置106可对应于中央处理器(cpu)或另一种类型的装置。

19.微控制器104集成到存储器装置102中。微控制器104包括一或多个cpu内核和存储指令的存储器(例如,随机存取存储器),该指令可由微控制器104的一或多个cpu内核执行以控制对存储器装置102的访问,如本文所述。下文进一步描述的图11描绘了微控制器的实例,诸如微控制器104。微控制器104被配置为通信地耦合到利用存储器装置102的一或多个处理器装置,并控制任何此类处理器装置对存储器装置102的访问。由于嵌入存储器装置102中的微控制器104被配置为从利用存储器装置102的处理器装置接收访问存储器装置102的所有请求,并且由于微控制器装置102的存储器对于那些处理器装置是不可访问的,因此可防止那些处理器装置(例如,在那些处理器装置上执行的程序)规避由微控制器104强制执行的数据访问限制。因此,用户可能无法通过在有权访问存储器装置102的处理器上执行黑客软件来规避数据访问限制。在所示的实例中,处理器装置106耦合到微控制器104和存储器装置102。虽然示出了一个处理器装置,但在其它实例中,微控制器104控制多个处

理器对存储器装置102的访问。如图所示,处理器装置106耦合到微控制器104和存储器装置102。

20.微控制器104被配置为向处理器装置106暴露支持一或多个存储器访问命令的应用编程接口(api)。处理器装置106被配置为使用api向微控制器104发出存储器访问请求。此类访问请求可对应于读请求或写请求。微控制器104被配置为接收访问请求并响应于访问请求基于与数据相关联的一或多个访问权限来发起或拒绝对存储在存储器装置102上的数据的访问。此外,微控制器104被配置为基于授权数据管理与受控数据相关联的访问权限。示例性授权数据可指示一或多个基于时间的限制、一或多个使用计数限制、一或多个其它类型的限制或其组合。如本文所使用的,受控数据是指微控制器104基于存储的授权数据管理其一或多个访问权限的数据。在一些实施方式中,可分配给受控数据的访问权限可被限制为仅执行访问和无访问。相反,由存储器装置102存储的通用数据和/或存储器装置102的通用数据区可与读和写访问权限相关联。处理器装置106可包括防止处理器装置106在被激活时复制数据的仅执行机制。微控制器104可结合发起对相关联的数据的访问来发起仅执行机制的激活并执行仅访问权限。

21.处理器装置106无法直接向存储器装置102发出存储器访问请求。例如,存储器装置102的字线和/或位线选择输入可物理地连接到微控制器104,使得处理器装置106不能在没有通过api向微控制器104发出信号的情况下致使这些线被驱动。因此,图1所示的处理器装置106与存储器装置102之间的耦合可限于处理器装置106接收由存储器装置102输出的数据。在一些实施方式中,处理器装置106与存储器装置102之间的所有耦合都是通过微控制器104建立的。由于处理器装置106将所有存储器访问请求传输到微控制器104,因此可防止由处理器装置106执行的软件规避由微控制器104施加的访问控制。

22.在所示的实例中,存储器装置102存储具有相关联的第一访问权限108的授权数据110。授权数据110标识由存储器装置102存储的受控数据114。例如,授权数据110可包括受控数据114的存储器地址、受控数据114的大小或其组合。受控数据114与第二访问权限112相关联并且授权数据110指示一或多个限制,微控制器104基于这些限制来管理第二访问权限112。

23.在特定实例中,第一访问权限108可对应于无访问权限。因此,微控制器104可拒绝处理器装置106访问授权数据110的任何请求。这可防止处理器装置106篡改授权数据110。

24.在所示的实例中,处理器装置106根据微控制器104暴露的api向微控制器104传输对受控数据114的数据请求116。响应于数据请求116,微控制器104基于访问权限112来确定是否发起对受控数据114的访问。在一些实施方式中,微控制器104可进一步基于授权数据110来确定是否响应于数据请求116并且在确定是否发起访问之前更新访问权限112。

25.一旦微控制器104确定是否发起对受控数据114的访问,微控制器104就基于该确定发起数据响应118的输出。数据响应118可对应于由存储器装置102或由微控制器104输出的一或多个信号。例如,响应于对应于读请求的数据请求116和确定第二访问权限112指示仅执行权限,微控制器104可致使存储器装置102输出受控数据114作为数据响应118。此外,微控制器104可用信号通知处理器装置106的仅执行机制以防止处理器装置106复制受控数据114。作为另一个实例,响应于对应于写请求的数据请求116和确定第二访问权限112指示仅执行权限,微控制器104可致使存储器装置102输出错误消息作为数据响应118。作为另一

个实例,响应于确定第二访问权限112指示无访问权限,微控制器104可致使存储器装置102输出错误消息作为数据响应118。

26.因此,微控制器104可基于第二访问权限112来控制处理器装置106对受控数据114的访问。如下文进一步解释的,微控制器104基于授权数据110进一步管理第二访问权限112。因此,可强制执行对访问受控数据114的限制,并且受控数据114的创建者可更有效地将对受控数据114的访问货币化。

27.在一些实施方式中,授权数据110、受控数据114、第一访问权限108或其组合由存储器装置102的原始装置制造商设置。在一些实施方式中,可在包括存储器装置102的装置的硬件引导过程期间设置或更新授权数据110、受控数据114、第一访问权限108或其组合中的一或多者。例如,微控制器104的api的某些命令可仅在引导序列期间可操作。在一些实施方式中,api的某些命令需要密码或其它类型的认证方法才能起作用。

28.在示例性实例中,存储器装置102对应于包括在个人计算装置中的快闪存储器并且处理器装置106对应于个人计算装置的通用处理器。为了访问存储在存储器装置102上的数据,处理器装置106使用微控制器104的api发出请求。微控制器104基于存储在微控制器104的存储器中的指令并基于访问权限108、112和授权数据110来控制对存储器装置102的访问。处理器装置106可能无法直接访问存储器装置102(例如,在不向微控制器104发出请求的情况下)并且可能无法改变微控制器104的存储器。因此,个人计算装置的用户可能无法使用由处理器装置106执行的软件(例如,黑客工具)来规避由微控制器104对存储在存储器装置102中的数据施加的访问限制。

29.在一些实施方式中,除了受控数据114之外,通用数据也由存储器装置102存储。图2示出了其中存储器装置102存储通用数据204的系统100的实例。通用数据204与独立于授权数据110的第三访问权限202相关联。在一些实施方式中,第三访问权限202可由微控制器104基于从处理器装置106接收的命令来设置。在所示的实例中,处理器装置106向微控制器104传输数据请求206。微控制器104然后响应于数据请求206发起数据响应208。

30.在其中数据请求206标识授权数据110的实例中,微控制器104基于第一访问权限108发起数据响应208。例如,响应于确定第一访问权限108指示无访问,微控制器104可致使存储器装置102输出错误消息。

31.在其中数据请求206标识受控数据114的实例中,微控制器104基于第二访问权限112发起数据响应208。例如,响应于确定第二访问权限112指示无访问权限,微控制器104可致使存储器装置102输出错误消息。另选地,响应于对应于写请求的数据请求206和确定第二访问权限112指示仅执行权限,微控制器104可致使存储器装置102输出错误消息。另选地,响应于对应于读请求的数据请求206和确定第二访问权限112指示仅执行访问,微控制器104可致使存储器装置102输出受控数据114。此外,响应于确定第二访问权限112指示仅执行访问,微控制器104可发起处理器装置106的仅执行机制的激活。

32.在其中数据请求206标识通用数据204的实例中,微控制器104基于第三访问权限202发起数据响应208。例如,响应于确定第三访问权限202指示无访问权限,微控制器104可致使存储器装置102输出错误消息。另选地,响应于对应于写请求的数据请求206和确定第三访问权限202指示仅执行权限,微控制器104可致使存储器装置102输出错误消息。另选地,响应于对应于读请求的数据请求206和确定第三访问权限202指示仅执行访问,微控制

器104可致使存储器装置102输出通用数据204。此外,响应于确定第三访问权限202指示仅执行访问,微控制器104可发起处理器装置106的仅执行机制的激活。另选地,响应于对应于读请求的数据请求206和确定第三访问权限202指示读写访问,微控制器104可致使存储器装置102输出通用数据204。另选地,响应于对应于写请求的数据请求206和确定第三访问权限202指示读写访问,微控制器104可致使存储器装置102将数据请求206所指示的数据存储在通用数据204中。在此类实例中,数据响应208可对应于写确认消息或信号。

33.因此,图2示出了存储器装置102可如何支持受控数据和通用数据两者。因此,系统可为分布式的以用于存储通用数据同时还包括增值(例如,受控)数据的一般用途。

34.在上述实例中,访问权限和授权数据与任何相关联的数据(非受控的或受控的)一起存储在存储器装置102中。然而,在替代实施方式中,访问权限和/或授权数据可存储在单独的存储器装置中。图3示出了其中访问权限和授权数据存储在单独的存储器装置中的实例。在所示的实例中,微控制器104与存储第一访问权限108、授权数据110和第二访问权限112的第二存储器装置302通信地耦合。微控制器104响应于数据请求316发起数据响应318以基于存储在第二存储器装置302上的数据访问存储在存储器装置102上的数据。

35.现在参考图4,示出了更详细地示出授权数据的系统100的示意图。在图4的所示的实例中,授权数据110包括标识符402和日志406。标识符402标识受控数据114。在一些实例中,标识符402对应于受控数据114的存储器地址、受控数据114的大小或其组合。授权数据110进一步包括日志406。日志406指示对受控数据114的使用的一或多个限制。此类限制可为基于时间的、基于访问计数的、基于一些其它特征的或其组合。在一些实施方式中,日志406进一步包括受控数据114的使用指示符,诸如访问计数或受控数据114已经被使用的持续时间。例如,日志406可存储指示受控数据可被执行30分钟的限制以及受控数据114已经被执行多长时间的指示符。在一些实施方式中,存储在日志406中的使用指示符被周期性地重置。例如,受控数据114已经被执行多长时间的指示符可每天重置一次。

36.在所示的实例中,处理器装置106基于日志406设置第二访问权限112。微控制器104在接收到对受控数据114的数据请求时或在更新日志406(例如,访问计数或受控数据114已经被使用的持续时间)时周期性地更新访问权限。此外,微控制器104基于对受控数据114的访问(例如,实时)更新日志406。因此,微控制器104强制执行对存储在日志406中的受控数据114的访问的限制。

37.图4进一步示出了处理器装置106根据微控制器104暴露的api向微控制器104传输对受控数据114的数据请求416,并且微控制器104发起数据响应418。

38.参考图5,示出了其中存储在日志中的限制基于时间的实例。在图5中,日志406存储授予时间502。授予时间502指示受控数据114被授权执行的持续时间。例如,授予时间502可指示30分钟。日志406进一步包括经过时间504(例如,经过的访问持续时间)。经过时间504指示受控数据114已经被处理器装置106访问了多长时间。微控制器104被配置为基于授予时间502与经过时间504的比较来设置第二访问权限112。例如,响应于确定授予时间502大于经过时间504,微控制器104可将第二访问权限112设置为仅执行权限。作为另一个实例,响应于确定授予时间502小于或等于经过时间504,微控制器104可将第二访问权限112设置为无访问。在一些实施方式中,微控制器104周期性地设置访问权限112。例如,微控制器104可每10分钟将授予时间502与经过时间504进行比较,并相应地设置第二访问权限

112。在其它实施方式中,微控制器104响应于数据请求基于日志406更新第二访问权限112。

39.在所示的实例中,系统100包括耦合到微控制器104的时钟508。微控制器104被配置为基于来自时钟508的信号测量处理器装置106访问受控数据114所花费的时间并且相应地更新经过时间504。例如,微控制器104可接收对受控数据114的数据请求416。基于第二访问权限112,微控制器104可发起对受控数据114的访问。一旦发起对受控数据114的访问,微控制器104可进一步基于来自时钟508的信号周期性地增加经过时间504,直到微控制器104从处理器装置106接收到访问完成消息510(或者直到经过时间504大于或等于授予时间502)。在一些实施方式中,微控制器104被配置为在处理器装置106正在访问受控数据114时响应于确定经过时间504和等于或超过授予时间502而禁用对受控数据114的访问。例如,微控制器104可将第二访问权限112设置为无访问并致使存储器装置102停止输出受控数据114和/或向处理器装置106发送一或多个信号以致使处理器装置106停止使用受控数据114。

40.因此,图5示出了其中微控制器104强制执行与数据相关联的基于时间的访问限制的实例。因此,存储在存储器装置102上的增值内容可限于特定的使用持续时间。如上所述,微控制器104可周期性地重置存储在日志406中的使用指示符,诸如经过时间504。因此,有限的持续时间(例如,30分钟)可对应于一个时间段(例如,一天)。

41.参考图6,示出了其中存储在日志中的限制基于访问计数的实例。在图6中,日志406存储授予访问602的次数。授予访问602指示处理器装置106被授权访问受控数据114的次数。例如,授予访问602可指示5次访问。日志406进一步包括访问计数604。访问计数604指示受控数据114已经被处理器装置106访问的次数计数。微控制器104被配置为基于授予访问602与访问计数604的比较来设置第二访问权限112。例如,响应于确定授予访问602大于访问计数604,微控制器104可将第二访问权限112设置为仅执行权限。作为另一个实例,响应于确定授予访问602小于或等于访问计数604,微控制器104可将第二访问权限112设置为无访问。在一些实施方式中,微控制器104周期性地设置访问权限112。例如,微控制器104可每10分钟将授予访问602与访问计数604进行比较,并相应地设置第二访问权限112。在其它实施方式中,微控制器104响应于数据请求更新第二访问权限112。

42.在所示的实例中,微控制器104被配置为基于授予访问602与访问计数604的比较来设置第二访问权限112。响应于接收到数据请求416,微控制器104被配置为基于第二访问权限112来确定是否授予对受控数据114的访问。微控制器104被进一步配置为响应于确定发起对受控数据114的访问来增加访问计数604并更新第二访问权限112。

43.因此,图6示出了其中微控制器104强制执行与数据相关联的基于访问计数的访问限制的实例。因此,存储在存储器装置102上的增值内容可限于特定的访问计数。如上所述,微控制器104可周期性地重置存储在日志406中的使用指示符,诸如访问计数604。因此,授予访问602(例如,5次访问)可对应于一个时间段(例如,一天)。

44.参考图7,示出了其中存储器装置102存储多个受控数据项的系统100的实例。在所示的实例中,除了受控数据114之外,存储器装置102还存储第二受控数据704。第二受控数据704与由微控制器104基于包括在授权数据110中的第二日志708设置的第四访问权限702相关联。第二日志708与指示第二受控数据704的第二标识符706相关联。在一些实施方式中,日志406、708包括不同类型的限制。例如,日志406可包括与受控数据114相关联的基于

时间的限制并且第二日志708可包括与第二受控数据704相关联的基于访问计数的限制。

45.因此,图7示出了微控制器104可控制对不同受控数据项的访问。此外,微控制器104可基于不同类型的限制来控制对不同受控数据项的访问。因此,存储器装置102可支持对数据的多种使用限制。

46.参考图8,描绘包括中断机制的存储器装置102的系统100的示意图。在所示的实例中,存储器装置102包括中断机制802。中断机制802可对应于硬件中断机制或者可对应于由微控制器104执行的软件。中断机制802被配置为监控对受控数据114的访问。响应于检测到对受控数据114的访问,中断机制802可从/向微控制器104传输信号以致使微控制器104增加访问计数604并重新计算访问权限112。因此,图8示出了用于通知微控制器104受控数据114已经被访问的机制。在替代实例中,微控制器104监控来自处理器装置106的请求以确定受控数据被访问。

47.参考图9,示出了示出控制对数据的访问的方法900的流程图。方法900可由与存储器装置集成的微控制器(诸如微控制器104)来执行。方法900包括在902处基于授予时间和经过时间来设置对存储器装置存储的受控数据的访问权限。例如,微控制器104可将授予时间502与包括在授权数据110中的经过时间504进行比较,并基于比较的结果设置第二访问权限112。举例说明,微控制器104可响应于确定授予时间502大于经过时间504将第二访问权限112设置为仅执行权限,或者可响应于确定授予时间502小于或等于经过时间504将第二访问权限112设置为无访问权限。

48.方法900进一步包括在904处接收访问受控数据的请求。例如,微控制器104可从处理器装置106接收访问受控数据114的数据请求416。

49.方法900进一步包括在906处确定访问权限是否与请求一致。例如,微控制器104可基于第二访问权限112来确定对于受控数据114是否允许由数据请求416指定的操作(例如,读、写、执行)。

50.响应于确定请求与访问权限不一致,方法900包括在918处拒绝对受控数据的访问,并继续监测访问请求。例如,响应于指示写请求的数据请求416和指示仅执行权限的第二访问权限112,微控制器104可生成指示写请求被拒绝的数据响应418并且可继续监测数据请求。作为另一个实例,响应于确定数据请求416标识对受控数据114的读请求并且第二访问权限112指示无访问权限,微控制器104可生成指示读请求被拒绝的数据响应418并且可继续监测数据请求。

51.响应于确定请求与访问权限一致,方法900包括在908处发起对受控数据的访问。例如,响应于指示读请求的数据请求416和指示仅执行权限的第二访问权限112,微控制器104可生成包括受控数据114的数据响应418。此外,微控制器104可用信号通知处理器装置106的仅执行机制以防止处理器装置106复制受控数据114。

52.方法900进一步包括在910处基于时钟更新经过时间。例如,当受控数据114被处理器装置106访问时,微控制器104可基于来自时钟508的信号周期性地更新经过时间504。

53.方法900进一步包括在912处确定经过时间是否大于或等于授予时间。例如,当受控数据114被处理器装置106访问时,微控制器104可周期性地确定经过时间504是否已经超过授予时间502。

54.响应于确定经过时间大于或等于授予时间,方法900包括在916处更新访问权限,

并在918处拒绝对受控数据的访问。例如,响应于确定经过时间504等于或超过授予时间502,微控制器104可将第二访问权限112设置为无访问权限。此外,微控制器104可向处理器装置106发出信号以停止使用受控数据114或以其它方式禁用对受控数据114的访问。在替代实例中,方法900可包括允许处理器装置106完成使用受控数据114但不允许未来使用。

55.响应于确定经过时间小于授予时间,方法900包括在914处确定是否已经接收到访问完成消息。如果没有接收到访问完成消息,则方法900包括在910处继续基于时钟更新经过时间。如果已经接收到访问完成消息,则方法900包括在902处基于授予时间和经过时间来设置对存储器装置存储的受控数据的访问权限。例如,微控制器104可继续更新经过时间504,直到从处理器装置106接收到访问完成消息510。响应于接收到访问完成消息510,微控制器104可停止更新经过时间504并基于授予时间502和经过时间504重新计算第二访问权限112。

56.因此,图9示出了可由微控制器用来对数据强制执行基于时间的访问限制的方法的实例。由于该方法可由与存储器装置集成的微控制器来执行,因此可防止访问该存储器装置的处理器装置规避访问限制。

57.参考图10,示出了示出控制对数据的访问的方法1000的流程图。方法1000可由与存储器装置集成的微控制器(诸如微控制器104)来执行。方法1000包括在1002处基于授予访问的数量和访问计数来设置对存储器装置存储的受控数据的访问权限。例如,微控制器104可将授予访问602与包括在授权数据110中的访问计数604进行比较,并基于比较的结果设置第二访问权限112。举例说明,微控制器104可响应于确定授予访问602大于访问计数604将第二访问权限112设置为仅执行权限,或者可响应于确定授予访问602小于或等于访问计数604将第二访问权限112设置为无访问权限。

58.方法1000进一步包括在1004处接收访问受控数据的请求。例如,微控制器104可从处理器装置106接收访问受控数据114的数据请求416。

59.方法1000进一步包括在1006处确定访问权限是否与请求一致。例如,微控制器104可基于第二访问权限112来确定对于受控数据114是否允许由数据请求416指定的操作(例如,读、写、执行)。

60.响应于确定请求与访问权限不一致,方法1000包括在1010处拒绝对受控数据的访问,并继续监测访问请求。例如,响应于指示写请求的数据请求416和指示仅执行权限的第二访问权限112,微控制器104可生成指示写请求被拒绝的数据响应418并且可继续监测数据请求。作为另一个实例,响应于确定数据请求416标识对受控数据114的读请求并且第二访问权限112指示无访问权限,微控制器104可生成指示读请求被拒绝的数据响应418并且可继续监测数据请求。

61.响应于确定请求与访问权限一致,方法1000包括在1008处发起对受控数据的访问。例如,响应于指示读请求的数据请求416和指示仅执行权限的第二访问权限112,微控制器104可生成包括受控数据114的数据响应418。此外,微控制器104可用信号通知处理器装置106的仅执行机制以防止处理器装置106复制受控数据114。

62.方法1000进一步包括在1012处增加访问计数,并在1002处重新计算访问权限。例如,在处理器装置106发起对受控数据114的访问之后,微控制器104可增加访问计数604并将更新的访问计数604与授予访问602进行比较。如果更新的访问计数604等于或超过授予

访问602,则微控制器104可将第二访问权限112更改为无访问。在一些实施方式中,微控制器104基于从中断机制802接收的信号更新访问计数604。

63.因此,图10示出了可由微控制器用来对数据强制执行基于访问计数的访问限制的方法的实例。由于该方法可由与存储器装置集成的微控制器来执行,因此可防止访问该存储器装置的处理器装置规避访问限制。

64.应当注意,与存储器装置集成的微控制器可实施不同的方法来强制执行对受控数据的访问限制。例如,在一些实施方式中,微控制器(例如,微控制器104)可通过评价响应于数据请求(例如,数据请求416)的限制而不是基于访问权限来确定是否发起对受控数据(例如,受控数据114)的访问。例如,响应于接收到数据请求416,微控制器104可基于访问计数604与授予访问602的比较或基于授予时间502与经过时间504的比较来确定是否发起对受控数据114的访问。

65.参考图11,示出了可对受控数据强制执行访问限制的计算机系统1100的框图。计算机系统1100包括计算装置1102。计算装置1102可对应于微控制器104并且可与诸如存储器装置102的存储器装置集成。计算机系统1100包括一或多个处理器1104和一或多个计算机可读存储装置1106。一或多个处理器1104可包括一或多个cpu、一或多个gpu、一或多个其它处理器或其组合。一或多个计算机可读存储装置1106可包括一或多个只读存储器(rom)装置、一或多个随机存取存储器(ram)装置、一或多个磁盘驱动器装置、一或多个其它类型的存储器装置或其组合。一或多个计算机可读存储装置1106存储可由一或多个处理器1104执行的数据访问控制指令1108,以执行本文所述的一或多个功能。

66.执行指令1108的一或多个处理器1104被配置为执行本文描述的操作。例如,一或多个处理器1104可接收和处理来自处理器装置的数据访问请求。一或多个处理器1104可根据本文描述的各种技术来强制执行与受控数据相关联的访问限制。

67.在本说明书中,术语“耦合(couple或couples)”意指间接或直接的有线或无线连接。因此,如果第一装置耦合到第二装置,则该连接可通过直接连接或通过经由其它装置和连接的间接连接。表述“基于”意指“至少部分基于”。因此,如果x基于y,则x可为y的函数和任意数量的其它因素。

68.在权利要求的范围内,在所描述的实施例中,修改是可能的,并且其它实施例也是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1