浮点数的编码与译码的方法与装置与流程

1.本发明涉及一种浮点数的编码与译码的方法与装置。

背景技术:

2.浮点(floating point,fp)数是一种实数的近似值数值表现法。在ieee二进制浮点数算术标准(例如ieee 754)中,规范了浮点数包括三个域:“符号(sign)”、“指数(exponent)”以及“尾数(fraction)”。“符号”可以表示浮点数的正负号,“指数”可以表示浮点数的次方数(以二为基底),以及“尾数”可以表示浮点数的小数(在正规化形式的浮点数的整数部分被预设为1,在非正规化形式的浮点数的整数部分被预设为0)。ieee二进制浮点数算术标准使用固定的“指数偏移值”(exponent bias)。指数偏移值固定为“127”。浮点数的指数值加上127(固定的指数偏移值)即为实数的指数值。例如,以ieee 754所规范的32位(bit)单精度(single-precision)浮点数为例,其符号、指数及尾数的位数量分别为1、8、23位。假设浮点数的符号值为s,浮点数的指数值为exp,浮点数的尾数值为f,则实数为(-1)s*2

(exp-127)

*1.f。ieee754所规范的浮点数的指数范围为0~255,而浮点数所表示的实数的指数范围为-126~127。

3.然则,在实际应用中,一群实数(浮点数)的指数值可能会集中在某个狭窄范围。例如,假设一群实数的指数是在-10~-3之间,则所对应的浮点数的指数是在117~124之间。很明显地,这一群实数仅使用了浮点数所能表示的指数范围-126~127中的极小部分,造成浮点数存储空间的浪费。

技术实现要素:

4.本发明提供一种浮点数的编码与译码的方法与装置,可以对浮点数进行编码/译码,以有效减少浮点数的数据量。

5.在本发明的实施例中,所述浮点数的编码方法用以将至少一个原浮点数转换为至少一个已编码浮点数。编码方法包括:依据至少一个原浮点数的至少一个原指数值,决定至少一个已编码浮点数的指数位数量以及计算指数偏移值;以及依据指数偏移值,将至少一个原浮点数中的一个目前原浮点数的原指数值转换为至少一个已编码浮点数中的一个目前已编码浮点数的已编码指数值。

6.在本发明的实施例中,所述浮点数的编码装置包括运算电路、存储单元以及转换电路。运算电路产生至少一个原浮点数。转换电路耦接至运算电路以接收至少一个原浮点数。转换电路依据至少一个原浮点数的至少一个原指数值去决定至少一个已编码浮点数的指数位数量以及计算指数偏移值。转换电路依据指数偏移值将至少一个原浮点数中的一个目前原浮点数的原指数值转换为至少一个已编码浮点数中的一个目前已编码浮点数的已编码指数值。转换电路将至少一个已编码浮点数存储至存储单元。

7.在本发明的实施例中,所述浮点数的译码方法用以将至少一个已编码浮点数转换为至少一个译码浮点数。解码方法包括:接收至少一个已编码浮点数所对应的指数偏移值;

依据指数偏移值与标准偏移值,将至少一个已编码浮点数中的一个目前已编码浮点数的已编码指数值转换为至少一个译码浮点数中的一个目前译码浮点数的译码指数值。

8.在本发明的实施例中,所述浮点数的译码装置包括存储单元、运算电路以及转换电路。存储单元被配置为存储至少一个已编码浮点数以及至少一个已编码浮点数所对应的指数偏移值。转换电路耦接至存储单元以接收至少一个已编码浮点数与指数偏移值。转换电路依据指数偏移值与标准偏移值将至少一个已编码浮点数中的一个目前已编码浮点数的已编码指数值转换为至少一个译码浮点数中的一个目前译码浮点数的译码指数值。转换电路将至少一个译码浮点数提供给运算电路。

9.基于上述,本发明诸实施例提供一种浮点数的压缩与解压缩技术。所述的浮点数的编码方法可以依据原浮点数的原指数值来动态调整指数位数量及指数偏移值,并依据指数位数量及指数偏移值将原浮点数转换为已编码浮点数。已编码浮点数的指数位数量相关于原浮点数的指数范围。如此一来,可以依据原浮点数的实际指数范围去动态改变浮点数的数据结构,以有效压缩浮点数的数据量,进而节省浮点数存储空间。另一方面,所述的浮点数的译码方法可以依据标准偏移值与已编码浮点数所对应的指数偏移值,来将已编码浮点数的已编码指数值转换回译码浮点数的译码指数值,进而可以将已编码浮点数转换为译码浮点数。如此一来,依据实际的应用需求,编码后的浮点数(经压缩浮点数)的数据结构可以被译码回标准的浮点数的数据结构。

附图说明

10.图1是依照本发明一实施例的一种浮点数的编码装置的电路方块(circuit block)示意图。

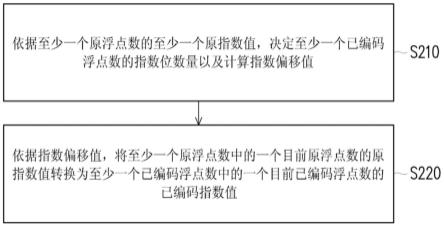

11.图2绘示本发明一实施例的浮点数的编码方法的流程示意图。

12.图3是依照本发明一实施例的一种浮点数的译码装置的电路方块示意图。

13.图4绘示本发明一实施例的浮点数的译码方法的流程示意图。

14.附图标记说明

15.100:浮点数的编码装置

16.110、330:运算电路

17.120、320:转换电路

18.130、310:存储单元

19.300:浮点数的译码装置

20.exp_b3:指数偏移值

21.fp1:原浮点数

22.fp2、fp3:已编码浮点数

23.fp4:解码浮点数

24.s210、s220、s410、s420:步骤

具体实施方式

25.现将详细地参考本发明的示范性实施例,示范性实施例的示例说明于附图中。只要有可能,相同元件附图标记在附图和描述中用来表示相同或相似部分。

26.在本案说明书全文(包括权利要求)中所使用的“耦接(或连接)”一词可指任何直接或间接的连接手段。举例而言,若文中描述第一装置耦接(或连接)于第二装置,则应该被解释成该第一装置可以直接连接于该第二装置,或者该第一装置可以透过其他装置或某种连接手段而间接地连接至该第二装置。本案说明书全文(包括权利要求)中提及的“第一”、“第二”等用语是用以命名组件(element)的名称,或区别不同实施例或范围,而并非用来限制组件数量的上限或下限,亦非用来限制组件的次序。另外,凡可能之处,在附图及实施方式中使用相同附图标记的组件/构件/步骤代表相同或类似部分。不同实施例中使用相同附图标记或使用相同用语的组件/构件/步骤可以相互参照相关说明。

27.图1是依照本发明一实施例的一种浮点数的编码装置100的电路方块(circuit block)示意图。于图1所示实施例中,编码装置100包括运算电路110、转换电路120以及存储单元130。依照实际设计,运算电路110可以进行任何应用运算,例如神经网络(neural network)运算或是其他运算。运算电路110的运算结果包含了一个或多个原浮点数fp1。存储单元130被用来存储运算电路110的运算结果。为了节省浮点数存储空间,原浮点数fp1需要被压缩。转换电路120耦接至运算电路110,以接收运算电路110所产生的原浮点数fp1。转换电路120可以对原浮点数fp1进行数据结构的转换(亦即进行编码方法,或是进行压缩方法),以产生已编码浮点数(已压缩浮点数)fp2。存储单元130耦接至转换电路120,以接收并且存放已编码浮点数fp2。

28.运算电路110与(或)转换电路120的相关功能可以利用硬件描述语言(hardware description languages,例如verilog hdl或vhdl)或其他合适的编程语言来实现为硬件。举例来说,运算电路110与(或)转换电路120的相关功能可以被实现于一或多个微控制器、微处理器、特殊应用集成电路(application-specific integrated circuit,asic)、数字信号处理器(digital signal processor,dsp)、场可程序逻辑门阵列(field programmable gate array,fpga)及/或其他处理单元中的各种逻辑区块、模块和电路。以软件形式及/或固件形式而言,运算电路110与(或)转换电路120的相关功能可以被实现为编程码(programming codes)。例如,利用一般的编程语言(programming languages,例如c、c++或汇编语言)或其他合适的编程语言来实现。所述编程码可以被记录/存放在“非临时的计算机可读取媒体(non-transitory computer readable medium)”中,例如包括只读存储器(read only memory,rom)、带(tape)、碟(disk)、卡(card)、半导体内存、可程序设计的逻辑电路及/或存储装置。中央处理器(central processing unit,cpu)、微控制器或微处理器可以从所述非临时的计算机可读取媒体中读取并执行所述编程码,从而达成相关功能。存储单元130例如可以是任意型式的随机存取内存(random access memory,ram)、只读存储器(read-only memory,rom)、闪存(flash memory)、硬盘或其他类似装置或这些装置的组合。

29.图2绘示本发明一实施例的浮点数的编码方法的流程示意图。请参照图1与图2。图2所示编码方法可以将原浮点数fp1转换为已编码浮点数fp2。于步骤s210中,转换电路120可以依据原浮点数fp1的原指数值,决定已编码浮点数fp2的指数位数量,以及计算指数偏移值。

30.例如,在一些实施例中,原浮点数fp1包括多个原浮点数。转换电路120可以统计这些原浮点数fp1的原指数值,以获得这些原指数值的数值范围。转换电路120可以依据所述

数值范围来决定已编码浮点数fp2的指数位数量。转换电路120可以从这些原指数值中选择其中一个作为第一代表值。所述第一代表值的选择可以依据设计需求来决定。举例来说,在一些实施例中,所述第一代表值可以是这些原指数值中的最大原指数值。依照实际设计,在其他实施例中,所述第一代表值也可以是这些原指数值中的最小原指数值、平均值或任意阀值。转换电路120可以从已编码浮点数fp2的指数位数量的值域中选择第一代表值所对应的一个值作为第二代表值。转换电路120可以使用第一代表值与第二代表值去计算已编码浮点数fp2的指数偏移值。在一些实施例中,所述第二代表值可以为已编码浮点数fp2的指数位数量的值域中的最大值。依照实际设计,在其他实施例中,所述第二代表值也可以为已编码浮点数fp2的指数位数量的值域中的最小值、中间值或任意阀值。

31.在此以表1所示具体数字作为步骤s210的操作范例。表1所示s1表示原浮点数fp1的原符号(sign)值,表1所示exp1表示原浮点数fp1的原指数(exponent)值,以及表1所示frac1表示原浮点数fp1的原尾数(fraction)值。在此假设原浮点数fp1的数据结构符合ieee二进制浮点数算术标准(例如ieee 754)的规范,亦即原符号值s1为1位数值,原指数值exp1为8位数值,原尾数值frac1为23位数值。

32.表1:一群原浮点数fp1的具体范例

[0033][0034][0035]

转换电路120可以统计表1所示这些原浮点数fp1的原指数值exp1,以获得这些原指数值exp1的数值范围。转换电路120可以依据表1所示这些原指数值exp1的数值范围来决定已编码浮点数fp2的指数位数量。表1所示这些原指数值exp1的数值范围为119~124,而在这个数值范围119~124中有6个整数。因此,已编码浮点数fp2的指数位数量可以被设定为3位,其中已编码浮点数fp2的指数位的值域为0~7。

[0036]

转换电路120可以从表1所示这些原指数值exp1中选择其中一个作为第一代表值。举例来说,所述第一代表值可以是这些原指数值exp1中的最大原指数值“124”。转换电路120可以从已编码浮点数fp2的指数位数量(3个位)的值域中选择第一代表值所对应的一个值作为第二代表值。举例来说,所述第二代表值可以是已编码浮点数fp2的指数位的值域“0~7”中的最大值“7”。转换电路120可以使用第一代表值“124”与第二代表值“7”去计算已编

码浮点数fp2的指数偏移值exp_b2。此时,exp1-exp_b1=124-127=7-exp_b2,其中exp_b1表示ieee二进制浮点数算术标准所使用的固定指数偏移值“127”。所以,已编码浮点数fp2的指数偏移值exp_b2为“10”。

[0037]

在步骤s220中,转换电路120可以依据已编码浮点数fp2的指数偏移值,将原浮点数fp1中的一个目前原浮点数的原指数值转换为已编码浮点数fp2中的一个目前已编码浮点数的已编码指数值。此外,依照实际设计,转换电路120还可以使用目前原浮点数的符号值作为目前已编码浮点数的符号值,以及转换电路120还可以使用目前原浮点数的尾数值作为目前已编码浮点数的尾数值。然后,转换电路120可以将已编码浮点数fp2的目前已编码浮点数存储至存储单元130。

[0038]

在此继续沿用表1所示原浮点数fp1的具体范例来说明步骤s220的操作,并将步骤s220的操作结果呈现于下述表2。表2所示范例可以参照表1的相关说明。表2所示exp2表示已编码浮点数fp2的已编码指数值,以及表2所示frac2表示已编码浮点数fp2的尾数值。在此假设原浮点数fp1的数据结构为符合ieee二进制浮点数算术标准(例如ieee 754)规范的32位数值,而已编码浮点数fp2的数据结构为8位数值。其中,已编码浮点数fp2的符号值为1位数值,已编码浮点数fp2的已编码指数值exp2为3位数值(这个已编码指数值exp2的位数量由步骤s210来动态决定)。使用已编码浮点数fp2的总位数量“8位”去扣除符号字段(1位)与指数字段(3位)后的剩余位数量为“4位”,而此剩余位可以被用来记录已编码浮点数fp2的尾数值frac2。因此,表2所示已编码浮点数fp2的尾数值frac2为4位数值。

[0039]

表2:对已编码浮点数fp2的转换结果

[0040][0041]

在表1与表2所示实施例中,步骤s210可以计算出已编码浮点数fp2的指数偏移值exp_b2为“10”。转换电路120可以依据已编码浮点数fp2的指数偏移值exp_b2,将表2所示原浮点数fp1中的一个目前原浮点数的原指数值exp1转换为表2所示已编码浮点数fp2中的一个目前已编码浮点数的已编码指数值exp2。举例来说,转换电路120可以计算exp2=exp1-exp_b1+exp_b2,以获得目前已编码浮点数的已编码指数值exp2。以表2所示第一笔浮点数作为计算范例,exp2=exp1-exp_b1+exp_b2=124-127+10=7。以表2所示第二笔浮点数作为计算范例,exp2=120-127+10=3。表2所示其他浮点数可以依此类推。针对指数部份转换电路120可以将8位的原指数值exp1转换为3位的已编码指数值exp2。因此,转换电路120可以有效减少已编码浮点数fp2的位数量。

[0042]

在一些实施例中,已编码浮点数fp2的尾数值frac2的位数量可以相同于原浮点数fp1的尾数值frac1的位数量。在这样的实施范例中,转换电路120可以使用目前原浮点数fp1的符号值s1作为目前已编码浮点数fp2的符号值,以及转换电路120还可以使用目前原浮点数fp1的尾数值frac1作为目前已编码浮点数fp2的尾数值frac2。然后,转换电路120可以将已编码浮点数fp2的目前已编码浮点数存储至存储单元130。在这样的实施范例中,转换电路120可以实现“无损压缩”而有效减少已编码浮点数fp2的位数量。

[0043]

依照实际设计,在另一些实施例中,转换电路120还可以进一步减少已编码浮点数fp2的位数量。例如,存储单元130中的已编码浮点数fp2的符号值字段可以依照实际设计省略。例如,转换电路120可以具有符号值缓存器(未绘示,例如是单一位缓存器);若转换电路120判断原浮点数fp1的每一个的符号值s1都为某一个共同符号值时(例如都为1或0),转换电路120可以将所述共同符号值存入所述符号值缓存器,并且在将原浮点数fp1转换为已编码浮点数fp2的过程中舍弃原浮点数fp1的每一个的符号值s1。亦即,在一些实施例中,原浮点数fp1的每一个的符号值s1可以不用存入存储单元130(存储单元130中的已编码浮点数fp2没有符号值字段)。在其他实施例中,若已知原浮点数fp1固定为正值或负值(原浮点数fp1的每一个的符号值都固定为某一个共同符号值)时,所述符号值缓存器可以依照实际设计被进一步省略。

[0044]

此外,在另一些实施例中,转换电路120还可以有效减少已编码浮点数fp2的尾数值frac2的位数量。例如在表2所示实施例中,已编码浮点数fp2的尾数值frac2的位数量从23位被缩减为4位,亦即已编码浮点数fp2的总位数量“8位”去扣除符号字段(1位)与指数字段(3位)后的剩余位数量作为尾数值frac2的位数量。当尾数值frac1的位数量大于尾数值frac2的位数量时,舍去或舍入该尾数值的一剩余部份。举例来说,以表2所示第一笔浮点数作为计算范例,尾数值frac1“1235141”的二进值为“001 0010 1101 1000 1100 0101”,则转换电路120可以使用尾数值frac1的高位(msb)的4位值“001 0”(十进值为“2”)作为尾数值frac2,以及舍去或舍入尾数值frac1的剩余部份。以表2所示第二笔浮点数作为计算范例,尾数值frac1“601492”的二进值为“000 1001 0010 1101 1001 0100”,则转换电路120可以使用尾数值frac1的高位(msb)的4位值“000 1”(十进值为“1”)作为尾数值frac2,以及舍去或舍入尾数值frac1的剩余部份。表2所示其他浮点数可以依此类推。在这样的实施范例中,转换电路120可以实现“有损压缩”而有效减少已编码浮点数fp2的位数量。在一些应用情境中,例如在神经网络运算的应用情境中,尾数值frac2的低位(lsb)的误差是可以接受的。

[0045]

综上所述,本实施例提供一种浮点数的压缩技术(编码方法)。所述的浮点数的编码方法可以依据原浮点数fp1的原指数值exp1来动态调整指数位数量及指数偏移值exp_b2。转换电路120可以依据指数位数量及指数偏移值exp_b2将原浮点数fp1转换为已编码浮点数fp2。已编码浮点数fp2的指数位数量相关于原浮点数fp1的指数范围。如此一来,可以依据原浮点数fp1的实际指数范围去动态改变浮点数fp2的数据结构,以有效压缩浮点数fp2的数据量,进而节省浮点数存储空间。

[0046]

图3是依照本发明一实施例的一种浮点数的译码装置300的电路方块示意图。于图3所示实施例中,译码装置300包括存储单元310、转换电路320以及运算电路330。存储单元310可以存储至少一个已编码浮点数fp3以及已编码浮点数fp3所对应的指数偏移值exp_

b3。图3所示已编码浮点数fp3与指数偏移值exp_b3可以参照图1与图2所示实施例所提及的已编码浮点数fp2与指数偏移值exp_b2的相关说明,故不再赘述。依照实际设计,在一些实施例中,图3所示存储单元310以及运算电路330可以参照图1所示存储单元130以及运算电路110的相关说明。

[0047]

图4绘示本发明一实施例的浮点数的译码方法的流程示意图。请参照图3与图4。图4所示译码方法可以将已编码浮点数fp3转换为译码浮点数fp4。于步骤s410中,转换电路320耦接至存储单元310,以接收已编码浮点数fp3与指数偏移值exp_b3。于步骤s420中,转换电路320可以依据指数偏移值exp_b3与标准偏移值exp_b4,将已编码浮点数fp3中的目前已编码浮点数的已编码指数值exp3转换为译码浮点数fp4中的目前译码浮点数的译码指数值exp4。此外,依照实际设计,转换电路320还可以使用目前已编码浮点数fp3的符号值作为目前译码浮点数fp4的符号值,以及转换电路320还可以使用目前已编码浮点数fp3的尾数值作为目前译码浮点数fp4的尾数值。然后,转换电路320可以将译码浮点数fp4的目前已编码浮点数提供给运算电路330。依照实际设计,运算电路330可以使用译码浮点数fp4去进行任何应用运算,例如神经网络运算或是其他运算。

[0048]

依照实际设计,译码浮点数fp4的数据结构可以是符合ieee二进制浮点数算术标准(例如ieee 754)所规范的浮点数数据结构或是其他数据结构。例如,译码浮点数fp4的符号值为1位数值,译码浮点数fp4的解码指数值exp4为8位数值,而译码浮点数fp4的尾数值frac4为23位数值。当解码浮点数fp4是符合ieee 754所规范的浮点数时,所述标准偏移值exp_b4可以是ieee 754所规范的固定指数偏移值“127”。

[0049]

在一些实施例中,转换电路320于步骤s420中可以计算指数偏移值exp_b3与标准偏移值exp_b4的差值。依照实际设计,在其他实施例中,译码装置300可以包括偏移差值缓存器(未绘示),用以存放预设的所述差值。这样的差值可以是一个固定值,或是先前计算好的数值。例如,以脱机(off line)方式预先计算好指数偏移值exp_b3与标准偏移值exp_b4的差值,然后将所述差值存放在所述偏移差值缓存器,以便于步骤s420使用。在这样的实施例中,步骤s420可以依照实际设计省略指数偏移值exp_b3与标准偏移值exp_b4的差值的动态计算。转换电路320可以使用所述差值将目前已编码浮点数fp3的已编码指数值exp3转换为目前译码浮点数fp4的解码指数值exp4。

[0050]

举例来说,在一实施例中,转换电路320可以将标准偏移值exp_b4减去指数偏移值exp_b3而产生所述差值,以及转换电路320可以将目前已编码浮点数fp3的已编码指数值exp3加上所述差值而产生目前解码浮点数fp4的解码指数值exp4。假设标准偏移值exp_b4为“127”,指数偏移值exp_b3为“10”,而目前已编码浮点数fp3的已编码指数值exp3为“7”,则目前解码浮点数fp4的解码指数值exp4为exp3+(exp_b4-exp_b3)=7+(127-10)=124。假设目前已编码浮点数fp3的已编码指数值exp3为“3”,则目前解码浮点数fp4的解码指数值exp4为3+(127-10)=120。

[0051]

在另一实施例中,转换电路320可以将指数偏移值exp_b3减去标准偏移值exp_b4而产生所述差值,以及转换电路320可以将目前已编码浮点数fp3的已编码指数值exp3减去所述差值而产生目前解码浮点数fp4的解码指数值exp4。假设标准偏移值exp_b4为“127”,指数偏移值exp_b3为“10”,而目前已编码浮点数fp3的已编码指数值exp3为“7”,则目前解码浮点数fp4的解码指数值exp4为exp3-(exp_b3-exp_b4)=7-(10-127)=124。假设目前已

编码浮点数fp3的已编码指数值exp3为“3”,则目前解码浮点数fp4的解码指数值exp4为3-(10-127)=120。

[0052]

在一些实施例中,已编码浮点数fp3的尾数值frac3的位数量可以相同于译码浮点数fp4的尾数值frac4的位数量。在这样的实施范例中,转换电路320可以使用目前已编码浮点数fp3的符号值作为目前译码浮点数fp4的符号值,以及转换电路320还可以使用目前已编码浮点数fp3的尾数值frac3作为目前解码浮点数fp4的尾数值frac4。然后,转换电路320可以将译码浮点数fp4的目前译码浮点数提供给运算电路330。

[0053]

此外,在另一些实施例中,解码浮点数fp4的尾数值frac4的位数量可以大于已编码浮点数fp3的尾数值frac3的位数量。当目前解码浮点数fp4的尾数值frac4(尾数字段)的位数量大于目前已编码浮点数fp3的尾数值frac3的位数量时,在将目前已编码浮点数fp3的尾数值frac3填入目前解码浮点数fp4的尾数字段后,转换电路320可以填入0于目前译码浮点数fp4的尾数字段的剩余部份。

[0054]

举例来说,假设解码浮点数fp4的尾数值frac4的位数量为23个位,而已编码浮点数fp3的尾数值frac3的位数量为4个位。转换电路320可以已编码浮点数fp3的尾数值frac3“001 0”填入目前解码浮点数fp4的尾数字段作为尾数值frac4的高位(msb)的4位值,以及转换电路320可以填入0于目前译码浮点数fp4的尾数字段的剩余部份。因此,目前译码浮点数fp4的尾数值frac4(尾数字段)为“001 0000 0000 0000 0000 0000”。

[0055]

综上所述,本实施例提供一种浮点数的解压缩技术(译码方法)。所述的浮点数的译码方法可以依据标准偏移值exp_b4与已编码浮点数fp3所对应的指数偏移值exp_b3,来将已编码浮点数fp3的已编码指数值exp3转换回译码浮点数fp4的解码指数值exp4。因此,依据实际的应用需求,转换电路320可以将已编码浮点数fp3的数据结构转换(解压缩)为标准的浮点数的数据结构。

[0056]

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1