半导体存储器及数据保护方法与流程

1.本公开涉及一种存储装置,且具体来说涉及一种半导体存储器及一种数据保护方法。

背景技术:

2.通用与非门(nand)快闪存储器具有电源切断干扰故障的问题。在此方面,电源切断干扰故障的问题可能是由存储器的数据写入期间非预期的电源切断引起的。具体言之,在存储器对存储器的存储器阵列中的现行页执行数据程序期间,若存储器的电源电压瞬间下降,则无法将数据成功地写入至存储器阵列中的现行页,且先前记录在存储器阵列的先前页或其他相邻页中的数据可能发生损耗或损坏。因此,关于如何提供在电源意外下降至停止运转时保护先前写入在存储器中的数据的数据保护功能,下文提供若干实施例的解决方案。

技术实现要素:

3.本公开涉及一种半导体存储器及一种数据保护方法,且可操作有效数据保护功能。

4.本公开的半导体存储器包含存储器阵列、开关电路、控制电路以及电源切断监视电路。开关电路耦接至存储器阵列。控制电路耦接至开关电路。电源切断监视电路耦接至控制电路及电源电压。电源切断监视电路用以判定电源电压是否在写入期间下降至第一电源切断检测电平以下,以将触发信号输出至控制电路。控制电路根据触发信号执行半导体存储器的重设程序。第一电源切断检测电平低于半导体存储器的数据表中记录的电源电压的最小值。

5.本公开的半导体存储器的数据保护方法包含以下步骤:藉由控制电路在写入期间执行半导体存储器的写入操作;藉由电源切断监视电路判定电源电压是否在写入期间下降至第一电源切断检测电平以下;当电源电压下降至第一电源切断检测电平以下时,藉由电源切断监视电路将触发信号输出至控制电路;藉由控制电路根据触发信号执行半导体存储器的重设程序,其中第一电源切断检测电平低于半导体存储器的数据表中记录的电源电压的最小值。

6.基于上述,根据本公开的半导体存储器及数据保护方法,在写入期间,半导体存储器能够自动监视电源电压是否非预期地下降至第一电源切断检测电平以下,以自动执行数据保护以防止瞬时电源故障。

7.为使前述内容更容易理解,如下详细描述附有图式的若干实施例。

附图说明

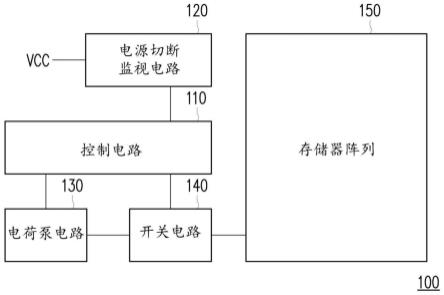

8.图1为示出根据本公开的实施例的半导体存储器的示意图。

9.图2为示出根据本公开的实施例的存储器阵列及其周边电路的示意图。

10.图3为示出根据本公开的实施例的数据保护方法的流程图。

11.图4为示出根据本公开的实施例的电源电压的电压波形图。

12.图5为示出根据本公开的实施例的电源切断监视电路的示意图。

13.图6为示出根据本公开的另一实施例的电源电压及输出电压的电压关系图。

14.图7为示出根据本公开的实施例的重设程序的流程图。

15.【符号说明】

16.100:半导体存储器

17.110:控制电路

18.120:电源切断监视电路

19.121:分压器

20.122:电压产生器

21.123:比较器

22.130:电荷泵电路

23.131:第一电荷泵

24.132:第二电荷泵

25.140:开关电路

26.141:第一解码器

27.142:第二解码器

28.143:第三解码器

29.150:存储器阵列

30.151_1~151_p:页缓冲器

31.blse、blso:位线选择信号

32.c(0,0)~c(n,m):存储器区

33.cs1_1~cs1_k、cs2_1~cs2_k、sd_0~sd_m、ss_0~ss_m、ble_1~ble_p、blo_1~blo_p:选择开关

34.gsgd、gsgs:全域选择栅极线

35.gwl0~gwln:全域字线

36.lwl0~lwln:局部字线

37.pasv:选择信号

38.s310、s320、s330、s340、s710、s720、s730:步骤

39.sgd、sgs:选择栅极线

40.sl:选择线

41.t0:时间

42.vcc:电源电压

43.v_div:分压电压

44.v_max:最大电压电平

45.v_min:最小电压电平

46.vo:输出信号

47.v_ref:参考电压

48.v_typ:中央电压电平

49.v_th:第一电源切断检测电平

具体实施方式

50.应理解,在不脱离本公开的范围的情况下,可利用其他实施例,且可进行结构改变。此外,应理解,本文中所使用的成语及术语是出于描述目的且不应被视为限制性的。“包含”、“包括”或“具有”以及其变体在本文中的使用意谓涵盖其后所列举的项目及其等效物以及额外项目。除非以其他方式受限,否则本文中的术语“连接”、“耦接”及“电连接”以及其变体被广泛使用,且涵盖直接及间接的连接、耦接以及安装。

51.图1为示出根据本公开的实施例的半导体存储器的示意图。参考图1,半导体存储器100包含控制电路110、电源切断监视电路120、电荷泵电路130、开关电路140以及存储器阵列150。半导体存储器100可为与非门快闪存储器。控制电路110耦接至电源切断监视电路120、电荷泵电路130以及开关电路140。开关电路140耦接至电荷泵电路130及存储器阵列150。控制电路110控制电荷泵电路130及开关电路140执行存储器阵列150的存取操作。举例而言,控制电路110可对存储器阵列150执行写入操作或抹除操作,以读取数据或将数据写入至存储器阵列150中。写入操作的写入信号(写入电压)及抹除操作的抹除信号(抹除电压)由电荷泵电路130产生。在本实施例中,电荷泵电路130在写入期间经由开关电路140将多个字线电压提供至存储器阵列150。

52.在本实施例中,电源切断监视电路120用以检测电源电压vcc是否在半导体存储器100的写入期间非预期地下降至0或存储器在此处不可正常操作的电压电平,以自动执行半导体存储器100的重设程序,以防止存储器阵列150中先前记录(写入)的数据。应注意,在本实施例中,电源切断监视电路120仅在写入期间启用,但本公开不限于此。在另一实施例中,电源切断监视电路120可在半导体存储器100的抹除时段或其他操作时段期间启用。

53.图2为示出根据本公开的实施例的存储器阵列及其周边电路的示意图。参考图1及图2,电荷泵电路130包含第一电荷泵131及第二电荷泵132。开关电路140包含第一解码器141、第二解码器142、第三解码器143以及多个选择开关cs1_1至cs1_k以及cs2_1至cs2_k,其中k为大于0的正整数。第一电荷泵131耦接至控制电路110及第一解码器141。第二电荷泵132耦接至控制电路110、第二解码器142以及第三解码器143。选择开关cs1_1至选择开关cs1_k的多个第一端耦接至全域选择栅极线gsgd、全域选择栅极线gsgs以及多个全域字线gwl0至gwln,且选择开关cs1_1至选择开关cs1_k的多个第二端耦接至第一解码器141。选择开关cs1_1至选择开关cs1_k的多个控制端耦接至第二解码器142。第三解码器143耦接在第二电荷泵132与选择开关cs2_1至选择开关cs2_k的多个控制端之间。

54.在本实施例中,存储器阵列150的存储器区中的一个可如图2中所示,存储器阵列150的存储器区中的一个可包含多个存储器单元c(0,0)至c(n,m),其中n及m为大于0的正整数。在本实施例中,全域选择栅极线gsgd、全域选择栅极线gsgs以及全域字线gwl0至全域字线gwln经由选择开关cs2_1至选择开关cs2_k耦接至选择栅极线sgd及选择栅极线sgs以及多个局部字线lwl0至lwln。选择栅极线sgd耦接至多个选择开关sd_0至sd_m的多个控制端,且选择栅极线sgs耦接至多个选择开关ss_0至ss_m的多个控制端。局部字线lwl0至局部字线lwln耦接至存储器单元c(0,0)至存储器单元c(n,m)。在本实施例中,存储器单元c(0,0)

至存储器单元c(n,m)中的每一行经由选择开关sd_0至选择开关sd_m耦接至多个全域位线gbl0至gblm中的一个,且存储器单元c(0,0)至存储器单元c(n,m)经由选择开关ss_0至选择开关ss_m耦接至选择线sl。偶数的全域位线经由选择开关ble_1至选择开关ble_p耦接至多个页缓冲器151_1至151_p,且奇数的全域位线经由选择开关blo_1至选择开关blo_p耦接至页缓冲器151_1至页缓冲器151_p,其中p为大于0的正整数。页缓冲器151_1至页缓冲器151_p中的每一个耦接至一个偶数的全域位线及一个奇数的全域位线。选择开关ble_1至选择开关ble_p以及选择开关blo_1至选择开关blo_p由位线选择信号blse及位线选择信号blso控制。

55.在半导体存储器100的写入操作中,控制电路110可控制第一电荷泵131及第一解码器141经由选择开关cs1_1至选择开关cs1_k提供写入信号(字线电压),且控制第二电荷泵132、第二解码器142以及第三解码器143提供多个导通信号(控制电压)及选择信号pasv(控制电压)以选择性地导通多个选择开关cs1_1至cs1_k以及cs2_1至cs2_k,以将数据写入至多个存储器单元c(0,0)至c(n,m)中。此外,当控制电路110执行第一数据页的写入操作时,第一列的存储器单元c(0,0)、c(0,2)至c(0,m-1)及偶数行的存储器单元c(0,0)至c(n,m)可藉由对应写入信号用数据写入。接着,当控制电路110执行第二数据页的写入操作时,第一列的存储器单元c(0,1)、c(0,3)至c(0,m)及奇数行的存储器单元c(0,0)至c(n,m)可藉由对应写入信号用数据写入。接着,当控制电路110执行第三数据页的写入操作时,第二列的存储器单元c(1,0)、c(1,2)至c(1,m-1)及偶数行的存储器单元c(0,0)至c(n,m)可藉由对应写入信号用数据写入。类似地,控制电路110可依序且定期将数据写入至存储器单元c(0,0)至存储器单元c(n,m)的不同数据页中。

56.然而,举例而言,在写入期间,当控制电路110执行第二数据页的写入操作时,若电源电压vcc非预期地下降至0或存储器在此处不可正常操作的电压电平,则由于存储器单元c(0,0)、存储器单元c(0,2)至存储器单元c(0,m-1)邻近于存储器单元(0,1)、存储器单元c(0,3)至存储器单元c(0,m),存储器单元c(0,0)、存储器单元c(0,2)至存储器单元c(0,m-1)的非预期的电源切断情况可影响存储器单元c(0,1)、存储器单元c(0,3)至存储器单元c(0,m)。换句话说,不仅第二数据页尚未完成写入,而且先前已记录第一数据页的存储器单元c(0,0)、存储器单元c(0,2)至存储器单元c(0,m-1)可能损坏及损失数据。因此,本公开的控制电路110可执行以下实施例的数据保护操作以有效地保护先前写入数据。

57.图3为示出根据本公开的实施例的数据保护方法的流程图。图4为示出根据本公开的实施例的电源电压的电压波形图。参考图1、图3以及图4,半导体存储器100可执行以下步骤s310至s340以实施数据保护功能。在步骤s310中,控制电路110可在写入期间执行半导体存储器100的写入操作。在步骤s320中,电源切断监视电路120可判定电源电压vcc是否在写入期间下降至第一电源切断检测电平v_th以下。具体来说,如图4中所示,电源电压vcc可具有中央电压电平v_typ,且在最大电压电平v_max与最小电压电平v_min之间上下摆动。电源切断监视电路120可检测电源电压vcc是否下降至第一电源切断检测电平v_th以下。最小电压电平v_min在半导体存储器的数据表中界定,且第一电源切断检测电平v_th低于电源电压vcc的电平v_min。在步骤s330中,当电源电压下降至第一电源切断检测电平v_th以下时,电源切断监视电路120可将触发信号输出至控制电路110。在步骤s340中,控制电路110根据触发信号执行半导体存储器100的重设程序。

58.在本实施例中,在时间t0处,重设程序可包含控制电路110控制电荷泵电路130停止将字线电压提供至字线。如图2中所示,第一电荷泵131停止将字线电压提供至全域字线gwl0至全域字线gwln,但第二电荷泵132可连续地将控制电压提供至选择开关cs1_1至选择开关cs1_k以及选择开关cs2_1至选择开关cs2_k的控制端。因此,控制选择开关cs1_1至选择开关cs1_k以及选择开关cs2_1至选择开关cs2_k在导通状态下保持操作,使得全域字线gwl0至全域字线gwln上的剩余电压可有效地释放(放电)。然而,在另一实施例中,当第一电荷泵131停止将字线电压提供至全域字线gwl0至全域字线gwln时,第二电荷泵132也可同步地停止将控制电压提供至选择开关cs1_1至选择开关cs1_k以及选择开关cs2_1至选择开关cs2_k的控制端,以同步地断开选择开关cs1_1至选择开关cs1_k以及选择开关cs2_1至选择开关cs2_k。在又一实施例中,当第一电荷泵131停止将字线电压提供至全域字线gwl0至全域字线gwln时,第二电荷泵132可在电源电压下降至第二电源切断检测电平以下时停止将控制电压提供至选择开关cs1_1至选择开关cs1_k以及选择开关cs2_1至选择开关cs2_k的控制端,以断开选择开关cs1_1至选择开关cs1_k以及选择开关cs2_1至选择开关cs2_k,其中第二电源切断检测电平低于第一电源切断检测电平v_th。因此,可减小或避免异常电压改变vcc对先前记录在存储器阵列150的存储器单元的一部分中的数据的影响。另外,重设程序可还包含控制电路110执行半导体存储器100的预设重设命令(例如,ffh重设命令),以执行半导体存储器100的重设操作。

59.图5为示出根据本公开的实施例的电源切断监视电路的示意图。图6为示出根据本公开的另一实施例的电源电压及输出电压的电压关系图。参考图5及图6,电源切断监视电路120包含分压器121、电压产生器122以及比较器123。分压器121耦接至电源电压vcc,且用以根据电源电压vcc输出分压电压v_div。分压器121可由多个分压器电阻器构成,但本公开不限于此。电压产生器122用以根据第一电源切断检测电平v_th输出参考电压v_ref。比较器123藉由比较器123的第一输入端及第二输入端耦接至分压器121及电压产生器122。比较器123用以藉由比较器123的输出端将用于产生触发信号的输出信号vo输出至控制电路110。如图6中所示,参考电压v_ref可藉由根据第一电源切断检测电平v_th设计。在本实施例中,当分压电压v_div与参考电压v_ref交叉时,比较器123的输出信号vo可自高电压电平变为低电压电平。因此,电源切断监视电路120可根据输出信号vo的电压改变而对应地产生触发信号至控制电路110。

60.图7为示出根据本公开的实施例的重设程序的流程图。应注意,基于图5的电源切断监视电路120的设计概念,图1的电源切断监视电路120可还包含更多的以上相关电路以设定第二电源切断检测电平及第三电源切断检测电平,且第二电源切断检测电平及第三电源切断检测电平可用于重设程序中以上不同阶段处的数据保护操作。因此,参考图1、图2以及图7,控制电路110可执行重设程序具有不同阶段(如以下步骤s710至s730)。在步骤s710中,当电源电压vcc在写入期间下降至第一电源切断检测电平以下时,控制电路110可使第一电荷泵131停止将多个字线电压输出至多个字线。在步骤s720中,当电源电压vcc在写入期间下降至第二电源切断检测电平以下时,控制电路110可进一步使第二电荷泵132停止将多个控制电压输出至多个第一开关,以断开多个选择开关cs1_1至cs1_k。在步骤s730中,当电源电压vcc在写入期间下降至第三电源切断检测电平以下时,控制电路110可执行半导体存储器100的预设重设命令(例如,ffh重设命令)。第三电源切断检测电平低于第二电源切

断检测电平,且第二电源切断检测电平低于第一电源切断检测电平。

61.亦即,在本实施例中,控制电路110可首先停止将字线电压提供至字线,且接着可在一时间段间隔之后断开选择开关cs1_1至选择开关cs1_k。因此,全域字线gwl0至全域字线gwln上的剩余电压可有效地释放(放电)。最后,控制电路110可执行半导体存储器100的预设重设命令。因此,执行以上步骤s710至s730的半导体存储器100能够保护先前记录(写入)在存储器阵列150中的可经有效保护的数据。

62.综上所述,本公开的半导体存储器及数据保护方法可额外设计电源切断监视电路,以在半导体存储器的写入期间自动地检测电源电压,且利用重设程序的一或多个以上数据保护操作来保护先前记录(写入)在存储器阵列中的数据。因此,本公开的半导体存储器及数据保护方法能够在电源电压在半导体存储器的写入期间非预期地下降使得半导体存储器不可正常操作时有效地保护先前记录(写入)在存储器阵列中的数据。

63.本领域技术人员将显而易见,可在不脱离本公开的范围或精神的情况下对所公开实施例作出各种修改及变化。鉴于前述,本公开意欲涵盖修改及变化,前提为所述修改及变化在随附权利要求书及其等效物的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1