一种多功能信号发生器校正方法及多功能信号发生器与流程

1.本发明涉及多功能信号发生器装置,公开了一种一种多功能信号 发生器校正方法及多功能信号发生器。

背景技术:

2.信号发生器作为一种基本频率源发生器无论是在教学、电子信息 工程和科研等领域,都有着广泛的使用。随着通信技术、卫星定位系 统、精密机械控制以及航空航天测控等领域对测控技术要求的不断提 高,对信号发生器的稳定度、精确度和频率带宽等要求越来越高。

3.现有技术awg系统中,需要dac将输入的数字离散波形数据 转化为模拟连续信号。而dac作为零阶保持器,由于矩形采样独特 的频域特性,不可避免的会引入幅频失真。

4.例如专利名称为:一种多功能信号发生器,专利申请号为: cn201010531082.4;申请日为:2010

‑

11

‑

03,专利申请公开了一种多 功能信号发生器,该信号发生器包括:波形存储器,用于存储波形数 据;中央处理器,用于根据用户的设置进行系统控制;固定时钟源, 用于提供稳定的时钟数据;现场可编程门阵列fpga,用于将固定时 钟源提供的时钟数据作频率合成处理,产生fpga的工作时钟,并根 据中央处理器的速率设置波形数据的读出速率,将读出的波形数据输 出;数模变换器,用于将fpga输出的波形数据进行数模变换;模拟 输出电路,用于将数模变换后的波形数据输出。

5.例如专利名称为:一种基于fpga的dds多信号发生器。专利 申请号为:cn201410365693.4,专利申请日为:2014

‑

07

‑

30;专利申 请公开了一种失真度小的基于fpga的dds多信号发生器。本发明 包括频率控制字部分、累加器、寄存器、正弦波数据部分、三角波数 据部分、锯齿波数据部分、方波波数据部分、波形选择器、波形选择 输入部分、高速da部分、低通部分和信号输出部分,其结构要点累 加器端口分别与频率控制字部分、寄存器、正弦波数据部分、三角波 数据部分、锯齿波数据部分相连,波形选择器端口分别与正弦波数据 部分、三角波数据部分、锯齿波数据部分、方波波数据部分、波形选 择输入部分、高速da部分相连。

6.对于现有技术的多功能信号发生器,其不能很好的进行幅频失真 的校正,同时一般信号发生器智能处理规则的波形数据,对于不规则 的波形数据不能进行处理。

技术实现要素:

7.本发明针对现有技术的多功能信号发生器,其不能很好的进行幅 频失真的校正,同时一般信号发生器智能处理规则的波形数据,对于 不规则的波形数据不能进行处理的缺点,提供了一种多功能信号发生 器校正方法及多功能信号发生器。

8.为了解决上述技术问题,本发明通过下述技术方案得以解决:

9.一种多功能信号发生器校正方法,包括主控制单元、fpga单元 和dac单元;其方法包括,

10.波表数据的传输,主控制单元发送波表数据并配置波表数据的频 率,并将波表文件和频率传送至fpga单元;

11.波形数据的校正,fpga单元对接收的波表数据进行存储和读取, 并通过幅频修正算法校正,将校正后的波形数据传送至dac单元。

12.根据dac的零阶保持特性,在数字信号输入dac之前进行幅值校 正,从而对幅频失真进行校正,大大提高了多功能信号发生器系统输 出信号的幅频特性。

13.作为优选,还包括数模转换,dac单元对接收的波形数据转换成 模拟的波形。将fpga单元输出的波形数据进行数模转换,同时数模 转换内包括有模拟输出电路,用于将数模变换后的波形数据输出。

14.作为优选,幅频修正算法其通过公式1获得修正后的波形数据 m

cali

;

[0015][0016]

公式1中,m

dc

为读出的波形数据,ω=2πf,f为输出波形频率; t为fpga单元的工作时钟周期。通过幅频修正算法对于读出的波形 数据进行幅度校正,从而对幅频失真进行校正,大大提高了多功能信 号发生器系统输出信号的幅频特性。

[0017]

作为优选,还包括固定时钟源的提供,固定时钟源提供固定的时 钟至fpga单元。通过固定时钟源,能够提供稳定的时钟从而整个数 据在传输的过程中稳定。

[0018]

作为优选,fpga单元包括时钟生成模块、波表存储模块、dds控 制模块、幅值校正模块;波形数据的校正方法包括,

[0019]

fpga单元工作时钟的生成,通过时钟生成模块对固定时钟源提 供的时钟进行处理得到fpga单元的工作时钟;

[0020]

波表数据的存储,通过波表存储模块使用例化的sdpram对波表 数据进行存储;

[0021]

波形数据的获取,dds控制模块依据主控制单元配置的频率,获 得波形数据的读取地址,依据读取地址读取波表数据对应的波形数据;

[0022]

幅值校正,幅值校正模块对读取的波形数据进行幅值校正,并获 得幅值校正后的波形数据。fpga单元不外挂sram或者sdram,其整 个的系统结构更简单,同时占用的fpga逻辑资源少,同时简化了整 个的fpga单元的控制,有利于节约多功能信号发生器的设计成本。

[0023]

作为优选,波表数据包括规则的波形数据和不规则的波形数据。 通过波表数据的传输,对于波形没有要求,这样在使用的过程中,既 能够传输规则的波形数据,又可以传输不规则的波形数据。

[0024]

作为优选,主控制单元发送波表数据并配置频率,并将波表文件 和频率传送至fpga单元;fpga单元对接收的波表数据进行存储和读 取,并通过幅频修正算法校正,将校正后的波形数据传送至dac单元; dac单元对接收的波形数据转换成模拟的波形。

[0025]

作为优选,还包括固定时钟源,固定时钟源提供固定的时钟至 fpga单元。

[0026]

作为优选,fpga单元包括时钟生成模块、波表存储模块、dds控 制模块、幅值校正模块;

[0027]

时钟生成模块对固定时钟源提供的时钟进行处理得到fpga单元 的工作时钟;

[0028]

波表存储模块使用例化的sdpram对波表数据进行存储;

[0029]

dds控制模块依据主控制单元配置的频率,进行相位累加计算, 每个时钟累加一次,累加的结果作为sdpram的读地址,读出相应的 波形数据;

[0030]

幅值校正模块对读取的波形数据进行幅值校正,并获得幅值校正 后的波形数据。

[0031]

作为优选,fpga内部的波表存储模块,包括使用fpga内部的bram 资源实现的sdpram,用于存储主控制单元下发的波表。fpga单元不 外挂sram或者sdram,其整个的系统结构更简单,同时占用的fpga 逻辑资源少,同时简化了整个的fpga单元的控制,有利于节约多功 能信号发生器的设计成本。

[0032]

本发明由于采用了以上技术方案,具有显著的技术效果:本发明 通过根据dac的零阶保持特性,在数字信号输入dac之前进行幅值校 正,从而对幅频失真进行校正,从而大大提高了多功能信号发生器系 统输出信号的幅频特性。

[0033]

本发明设计的fpga单元不外挂sram或者sdram,其整个的系统 结构更简单,同时占用的fpga逻辑资源少,同时简化了整个的fpga 单元的控制,有利于节约多功能信号发生器的设计成本。

附图说明

[0034]

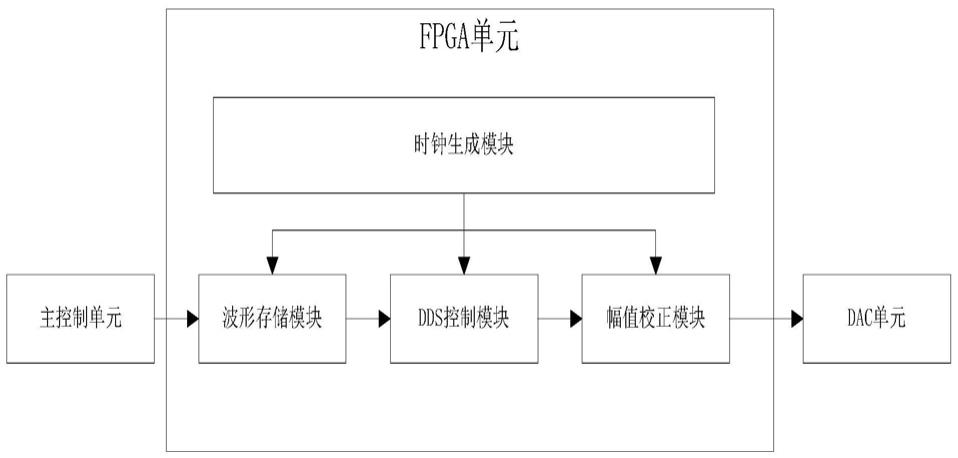

图1是本发明的结构图。

[0035]

图2是本发明的测试单元示意图。

[0036]

图3a是本发明的验证波形图校正前不带dds模块;

[0037]

图3b是本发明的验证波形图校正前带dds模块;

[0038]

图3c是本发明的验证波形图校正后带dds模块;

[0039]

图4是本发明的dds模块图。

具体实施方式

[0040]

下面结合附图与实施例对本发明作进一步详细描述。

[0041]

实施例1

[0042]

一种多功能信号发生器校正方法,包括主控制单元、fpga单元 和dac单元;其方法包括,

[0043]

波表数据的传输,主控制单元发送波表数据并配置波表数据的频 率,并将波表文件和频率传送至fpga单元;

[0044]

波形数据的校正,fpga单元对接收的波表数据进行存储和读取, 并通过幅频修正算法校正,将校正后的波形数据传送至dac单元。

[0045]

根据dac的零阶保持特性,在数字信号输入dac之前进行幅值 校正,从而对幅频失真进行校正,从而大大提高了多功能信号发生器 系统输出信号的幅频特性。

[0046]

还包括数模转换,dac单元对接收的波形数据转换成模拟的波形。 将fpga单元输出的波形数据进行数模转换,同时数模转换内包括有 模拟输出电路,用于将数模变换后的波形数据输出。

[0047]

幅频修正算法其通过公式1获得修正后的波形数据m

cali

;

[0048]

[0049]

公式1中,m

dc

为读出的波形数据,ω=2πf,f为输出波形频 率;t为fpga单元的工作时钟周期。通过幅频修正算法对于读出的 波形数据进行幅度校正,从而对幅频失真进行校正,大大提高了多功 能信号发生器系统输出信号的幅频特性。

[0050]

实施例2

[0051]

在实施例1基础上,本实施例还包括固定时钟源的提供,固定时 钟源提供固定的时钟至fpga单元。通过固定时钟源,能够提供稳定 的时钟从而整个数据在传输的过程中稳定。

[0052]

fpga单元包括时钟生成模块、波表存储模块、dds控制模块、 幅值校正模块;波形数据的校正方法包括,

[0053]

fpga单元工作时钟的生成,通过时钟生成模块对固定时钟源提 供的时钟进行处理得到fpga单元的工作时钟;

[0054]

波表数据的存储,通过波表存储模块使用例化的sdpram对波表 数据进行存储;

[0055]

波形数据的获取,dds控制模块依据主控制单元配置的频率,获 得波形数据的读取地址,依据读取地址读取波表数据对应的波形数据;

[0056]

幅值校正,幅值校正模块对读取的波形数据进行幅值校正,并获 得幅值校正后的波形数据。fpga单元不外挂sram或者sdram,其 整个的系统结构更简单,同时占用的fpga逻辑资源少,同时简化了 整个的fpga单元的控制,有利于节约多功能信号发生器的设计成本。

[0057]

波表数据包括规则波形数据和不规则的波形数据。通过波表数据 的传输,对于波形没有要求,这样在使用的过程中,既能够传输规则 的波形数据,又可以传输不规则的波形数据。

[0058]

实施例3

[0059]

多功能信号发生器,其包括主控制单元、fpga单元和dac单元, 主控制单元发送波表数据并配置频率,并将波表文件和频率传送至 fpga单元;fpga单元对接收的波表数据进行存储和读取,并通过幅 频修正算法校正,将校正后的波形数据传送至dac单元;dac单元对 接收的波形数据转换成模拟的波形。

[0060]

还包括固定时钟源,固定时钟源提供固定的时钟至fpga单元。

[0061]

fpga单元包括时钟生成模块、波表存储模块、dds控制模块、 幅值校正模块;

[0062]

时钟生成模块对固定时钟源提供的时钟进行处理得到fpga单元 的工作时钟;

[0063]

波表存储模块使用例化的sdpram对波表数据进行存储;

[0064]

dds控制模块依据主控制单元配置的频率,进行相位累加计算, 每个时钟累加一次,累加的结果作为sdpram的读地址,读出相应的 波形数据;

[0065]

幅值校正模块对读取的波形数据进行幅值校正,并获得幅值校正 后的波形数据。

[0066]

fpga内部的波表存储模块,包括使用fpga内部的bram资源实 现的sdpram,用于存储主控制单元下发的波表。fpga单元不外挂 sram或者sdram,其整个的系统结构更简单,同时占用的fpga逻 辑资源少,同时简化了整个的fpga单元的控制,有利于节约多功能 信号发生器的设计成本。

[0067]

实施例4

[0068]

在上述实施例基础上,本实施例根据用户的设置,cpu首先将 各个参数配置给

fpga;波表写入fpga内存波形存储器,波表写入 是否完成进行判断,写完之后则进行dds处理;首先启动dds,依据 cpu配置的频率开始dds累加器的累加,累加值截位处理,作为 sdpram的读地址,从而读出相应的波形数据,针对读出的波形数据, 进行幅值校正计算,从而得到校正后的幅值;并将校正后的幅值输入 值dac单元,进行波形的输出。

[0069]

依据附图4可知dds模块的框图,其包括相位累加器,相位累 加器是dds产生稳定精确信号的关键。经同步寄存器输出,送入相 位累加器,相位累加器是由同步寄存器与加法器组成,将前面同步寄 存器传送的频率信号相加。

[0070]

依据dds的原理,可知输出的频率f为:

[0071][0072]

是基准时钟的频率,n是相位累加器的数据位宽度,b

δθ

是频 率控制;

[0073]

dds系统的频率分辨率δf,即输出频率最小步进值,就是频率控 制字b

δθ

步进一个最小间隔,亦即b

δθ

=1对应的频率输出值;

[0074][0075]

只要基准频率足够高频足够稳定,同时n足够大,利用dds技 术,可以实现输出任意频率和任意精度的信号波形。

[0076]

依据附图3a所示,dac采样频率2m,波表2048个样点数;不 使用dds技术,只能输出2m/2048=976.5625m频率的波形;同样的 波表,使用dds技术,通过配置不同频率控制字,可以输出不同的 频率,比如设置频率控制字为2^42,取n=48,输出频率 f=(2m/2048)*2^42/2^48=15.2587890625khz,如附图3b所示,使用 dds技术、vpp为2v档位、未进行幅值校正,设置频率控制字为 2^42,测量幅值大概为1.90v左右;使用dds技术、vpp为2v档 位、进行了幅值校正,设置频率控制字为2^42,测量幅值大概为2.02v 左右,幅值有明显改善,如附图3c所示。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1