一种基于阻抗的走线评估优化方法、装置、设备及介质与流程

1.本发明涉及阻抗评估领域,尤其是涉及一种基于阻抗的走线评估优化方法、装置、设备及介质。

背景技术:

2.随着科技发展,尤其在集成电路的材料之进步,使指令周期有显着提升,促使集成电路走向高密度﹑小体积,单一零件,芯片组多采用bga(ball grid array,球栅数组封装)。bga出线是件不容易的事,由于空间有限,走线线宽和间距必须足够小,才能出线,但走线线宽和间距较小带来的问题是高阻抗和串扰问题。

3.按照常用的处理方式就是按照规范要求让bga的走线尽量的短,让所有的走线不仅间距均匀,而且尽量的宽。如图1所示,为一般pcb板(print circuit board,印刷电路板)中bga区域走线范例。但随着速度越来越快,为了保证信号质量,英特尔提出了tab routing设计。tab routing是将小梯形的铜皮添加到相邻平行走在线的一种方式,以更好的控制信号线的互容和阻抗,tab routing添加的地方主要是cpu中bga部分走线的位置上面。如图2

‑

图3所示,为pcb板中bga区域tab走线范例的不同角度的放大示意图。

4.在pcb设计中,pcb板提供的电路性能必须能够使信号在传输过程中不发生反射现象,信号保持完整,降低传输损耗,起到匹配阻抗的作用,这样才能得到完整、可靠、精确,无干扰、噪音的传输信号。pcb bga区域tab走线设计,通常需要使用3d仿真软件,绘出pcb bga区域tab走线结构,执行3d仿真,评估tab走线的阻抗值是否符合要求,如果对应tab走线的阻抗值不符合要求,需要改变tab走线参数,重新绘出pcb bga区域tab走线结构,然后重新进行仿真评估,不断优化调整,直至符合要求,需要花费大量时间,评估优化效率较低。

技术实现要素:

5.本发明为了解决现有技术中存在的问题,创新提出了一种基于阻抗的走线评估优化方法、装置、设备及介质,有效解决由于现有技术造成走线评估优化效率低的问题,有效地提高了走线评估的优化效率。

6.本发明第一方面提供了一种基于阻抗的走线评估优化方法,应用于印刷电路板中的球栅数组封装区域中,包括:

7.通过多个走线结构的阻抗仿真得到多个输入参数与阻抗的对应关系;

8.根据多个输入参数与阻抗的对应关系以及当前的输入参数,得到当前输入参数对应的阻抗,判断当前输入参数对应的阻抗是否满足预设范围,如果满足,则评估优化完成,如果不满足,则评估不通过。

9.可选地,通过多个走线结构的阻抗仿真得到多个输入参数与阻抗的对应关系具体包括:

10.仿真获得多个走线结构,每个走线结构对应的输入参数不同;

11.根据获得多个走线结构仿真获取对应的阻抗,将得到的多个走线结构以及对应的

阻抗建立多个输入参数与阻抗的对应关系。

12.进一步地,仿真的走线结构的数量与输入参数数量成正比。

13.可选地,输入参数包括但不限于走线宽度、走线间距、走线短边宽度、走线长边宽度、走线长度、不同走线间距、走线近端参考层介电质厚度、走线远端参考层介电质厚度、印刷电路板材料的介电常数、印刷电路板材料的损耗因子。

14.可选地,不同走线结构中,每一种输入参数均包括第一端点值、中间值、第二端点值,其中,第一端点值为输入参数的取值范围的最小值,第二端点值为输入参数的取值范围的最大值,中间值为输入参数的取值范围的最小值与最大值的一半。

15.可选地,还包括:

16.如果不满足,修改当前输入参数,重新得到当前输入参数对应的阻抗,直至当前输入参数满足预设范围。

17.本发明第二方面提供了一种基于阻抗的走线评估优化装置,应用于印刷电路板中的球栅数组封装区域中,包括:

18.对应关系确定模块,通过多个走线结构的阻抗仿真得到多个输入参数与阻抗的对应关系;

19.阻抗评估模块,根据多个输入参数与阻抗的对应关系以及当前的输入参数,得到当前输入参数对应的阻抗,判断当前输入参数对应的阻抗是否满足预设范围,如果满足,则评估优化完成,如果不满足,则评估不通过。

20.可选地,对应关系确定模块具体包括:

21.仿真子模块,仿真获得多个走线结构,每个走线结构对应的输入参数不同;

22.对应关系建立子模块,根据获得多个走线结构仿真获取对应的阻抗,将得到的多个走线结构以及对应的阻抗建立多个输入参数与阻抗的对应关系。

23.本发明第三方面提供了一种电子设备,包括:存储器,用于存储计算机程序;处理器,用于执行所述计算机程序时实现如本发明第一方面所述的一种基于阻抗的走线评估优化方法的步骤。

24.本发明第四方面提供了一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如本发明第一方面所述的一种基于阻抗的走线评估优化方法的步骤。

25.本发明采用的技术方案包括以下技术效果:

26.1、本发明通过建立多个输入参数与阻抗之间的对应关系,有效解决由于现有技术造成走线评估优化效率低的问题,有效地提高了走线评估的优化效率。

27.2、本发明技术方案中通过多个走线结构的阻抗仿真得到多个输入参数与阻抗的对应关系具体包括:仿真获得多个走线结构,每个走线结构对应的输入参数不同;根据获得多个走线结构仿真获取对应的阻抗,将得到的多个走线结构以及对应的阻抗建立多个输入参数与阻抗的对应关系,即通过多个输入参数不同的走线结构仿真结果建立多个输入参数与阻抗的对应关系,提高了多个输入参数与阻抗的对应关系的准确性以及可靠性,以便于提高走线评估的优化的准确性。

28.3、本发明技术方案中仿真的走线结构的数量与输入参数数量成正比,不同走线结构中,每一种输入参数均包括第一端点值、中间值、第二端点值,其中,第一端点值为输入参

数的取值范围的最小值,第二端点值为输入参数的取值范围的最大值,中间值为输入参数的取值范围的最小值与最大值的一半,适应于多个输入参数的情况,而且进一步地提高了多个输入参数与阻抗的对应关系的准确性以及可靠性。

29.4、本发明技术方案中如果不满足,修改当前输入参数,重新得到当前输入参数对应的阻抗,直至当前输入参数满足预设范围,不需要重新进行走线结构创建,直接调整参数,即可获得当前输入参数对应的阻抗,有效地提高了走线评估的优化效率。

30.应当理解的是以上的一般描述以及后文的细节描述仅是示例性和解释性的,并不能限制本发明。

附图说明

31.为了更清楚说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单介绍,显而易见的,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

32.图1为现有技术中pcb板中bga区域走线的俯视图(不放大);

33.图2为现有技术中pcb板中bga区域tab走线结构图的俯视图(放大后);

34.图3为现有技术中pcb板中bga区域tab走线结构图的侧视截面图(放大后);

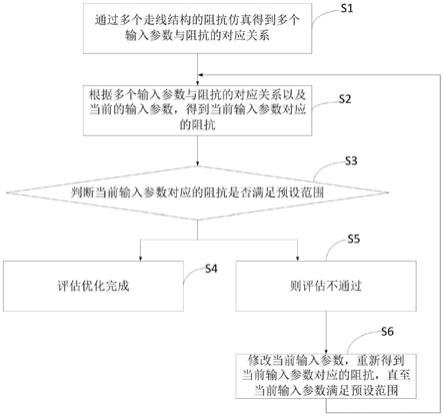

35.图4为本发明方案中实施例一方法的一流程示意图;

36.图5为本发明方案中实施例一方法中步骤s1的流程示意图;

37.图6为本发明方案中实施例一方法中仿真走线结构中输入参数与阻抗的对应关系示意图;

38.图7为本发明方案中实施例一方法中统计分析软件建立多个输入参数与阻抗对应关系的示意图;

39.图8为本发明方案中实施例一方法中统计分析软件确定的多个输入参数与阻抗的对应关系式示意图;

40.图9为本发明方案中实施例一方法中输入参数与阻抗的对应关系评估界面示意图;

41.图10为本发明方案中实施例一方法中的另一流程结构示意图;

42.图11为本发明方案中实施例二装置的一结构示意图;

43.图12为本发明方案中实施例二装置中对应关系确定模块101的结构示意图;

44.图13为本发明方案中实施例二装置的另一结构示意图;

45.图14为本发明方案中实施例三设备的结构示意图;

46.英文注释:ptab:同一走线之tab间距;tw:走线宽度;ts:走线间距;swtab:tab走线短边宽度;lwtab:tab走线长边宽度;ltab:tab走线长度;ptab:同一走线之tab间距;stab:不同走线之面对面tab间距;h1:tab走线近端参考层介电质厚度;h2:tab走线远端参考层介电质厚度;dk:印刷电路板材料的介电常数;df:印刷电路板材料的损耗因子;pin

‑

fieldvia:引脚区域过孔;pin

‑

field trace:引脚区域路径;predictionprofiler:jmp软件中刻画器:calculate:计算;impdeance:阻抗。

具体实施方式

47.为能清楚说明本方案的技术特点,下面通过具体实施方式,并结合其附图,对本发明进行详细阐述。下文的公开提供了许多不同的实施例或例子用来实现本发明的不同结构。为了简化本发明的公开,下文中对特定例子的部件和设置进行描述。此外,本发明可以在不同例子中重复参考数字和/或字母。这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施例和/或设置之间的关系。应当注意,在附图中所图示的部件不一定按比例绘制。本发明省略了对公知组件和处理技术及工艺的描述以避免不必要地限制本发明。

48.实施例一

49.如图4所示,本发明提供了一种基于阻抗的走线评估优化方法,应用于印刷电路板中的球栅数组封装区域中,包括:

50.s1,通过多个走线结构的阻抗仿真得到多个输入参数与阻抗的对应关系;

51.s2,根据多个输入参数与阻抗的对应关系以及当前的输入参数,得到当前输入参数对应的阻抗;

52.s3,判断当前输入参数对应的阻抗是否满足预设范围,如果判断结果为是,则执行步骤s4;如果判断结果为否,则执行步骤s5;

53.s4,评估优化完成;

54.s5,则评估不通过。

55.其中,如图5所示,步骤s1具体包括:

56.s11,仿真获得多个走线结构,每个走线结构对应的输入参数不同;

57.s12,根据获得多个走线结构仿真获取对应的阻抗,将得到的多个走线结构以及对应的阻抗建立多个输入参数与阻抗的对应关系。

58.其中,在步骤s11中,仿真的走线结构的数量与输入参数数量成正比。例如,如图6所示,当输入参数为六个时,仿真的走线结构的数量(case)可以为64个,也可以是其他数量,本发明在此不做限制。多个走线结构的仿真可以是在3d仿真软件中仿真多个bga区域tab走线结构。

59.输入参数具体是指与走线相关的输入参数,包括但不限于走线宽度(tw,单位:mil)、走线间距(ts,单位:mil)、tab走线短边宽度(swtab,单位:mil)、tab走线长边宽度(lwtab,单位:mil)、tab走线长度(ltab,单位:mil)、同一走线之tab间距(ptab,单位:mil)、不同走线之面对面tab间距(stab,单位:mil)、tab走线近端参考层介电质厚度(h1,单位:mil)、tab走线远端参考层介电质厚度(h2,单位:mil)、印刷电路板材料的介电常数(dielectric constant,dk)、印刷电路板材料的损耗因子(loss tangent,df)。

60.不同走线结构中,每一种输入参数均包括第一端点值、中间值、第二端点值,其中,第一端点值为输入参数的取值范围的最小值,第二端点值为输入参数的取值范围的最大值,中间值为输入参数的取值范围的最小值与最大值的一半。如图6所示,输入参数tab走线近端参考层介电质厚度h1,取值范围为3

‑

5,则在仿真的走线结构中取值可以是3、4、5;输入参数tab走线远端参考层介电质厚度h2,取值范围为4

‑

12,则在仿真的走线结构中取值可以是4、8、12;印刷电路板材料的介电常数dk,取值范围为3

‑

4,则在仿真的走线结构中取值可以是3、3.5、4;tab走线长度ltab,取值范围为2

‑

6,则在仿真的走线结构中取值可以是2、4、6;tab走线短边宽度swtab,取值范围为5

‑

15,则在仿真的走线结构中取值可以是5、10、15;

tab走线长边宽度lwtab,取值范围为5

‑

15,则在仿真的走线结构中取值可以是5、10、15;也可以是其他取值方式,取值时同一种输入参数的步长尽可能大一些,以便能够覆盖全部取值范围,具体地,如果仿真的走线结构的数量较多时,每一种输入参数的步长可以相对小一些,如果仿真的走线结构的数量较少时,每一种输入参数的步长可以相对大一些,以提高多个输入参数与阻抗的对应关系的准确性以及全面性。

61.进一步地,也可以将多个输入参数分别输入统计分析软件(例如jmp软件),通过jmp软件的反馈获取仿真的走线结构数量,以及仿真的走线结构数量中每一种输入参数的组合,本发明在此不做限制。

62.在步骤s12中,将仿真获得的多个tab走线结构的参数值及阻抗的仿真结果,可以通过非线性回归方程,建立多个输入参数与阻抗的对应关系,其中对应关系中包括各项输入参数对于输出阻抗的影响权重;也可以利用统计分析软件(例如jmp软件),使用jmp软件内的rsm(response surface methodology,反应曲面法)功能,如图7所示,mean代表输入参数变化量的中间值,sd(standard deviation,标准差)代表标准偏差,横坐标中

‑

1代表输入参数变化量的最小值,1代表输入参数变化量的最大值,纵坐标35~55代表阻抗值(impedance),random代表输入参数变化是随机的,normal代表是常态分布,通过统计分析软件分析输入参数和输出结果(阻抗)的关系,以及各个输入参数影响阻抗的比重,得到输入参数和阻抗之间的关系式,如图8所示(输入参数如图6所示)。

63.其中,在步骤s2中,可以在excel中建立tab走线多个输入参数和阻抗的单元格,将步骤s1得到的多个输入参数与阻抗的对应关系式写入excel公式,建立pcb板中bga区域tab走线设计评估工具。如图9所示,根据tab走线结构和选用额pcb板的材料,在pcb板中bga区域tab走线设计评估工具中输入各项参数,即可得到结果。根据多个输入参数与阻抗的对应关系式以及当前输入的多个输入参数,即可确定当前输入的多个输入参数对应的阻抗。在输入参数的选择中,可以选用比较常用的输入参数,例如输入参数tab走线近端参考层介电质厚度h1、输入参数tab走线远端参考层介电质厚度h2、印刷电路板材料的介电常数dk、tab走线长度ltab、tab走线短边宽度swtab、tab走线长边宽度lwtab,这样不仅能够减少输入参数变化需要重新建立输入参数与阻抗的对应关系的次数,而且使用方便,不需要经常改动,提高效率。

64.在步骤s3

‑

s5中,阻抗预设范围可以是40ohms+/

‑

5%以内(以ddr5走线为例,一般阻抗设计要求为40ohms),也可以根据实际情况进行调整,本发明在此不做限制。只要当前多个输入参数对应的阻抗符合阻抗预设范围,则完成pcb板中bga区域tab走线优化完成。

65.进一步地,如图10所示,本发明技术方案还提供的一种基于阻抗的走线评估优化方法,还包括:

66.s6,修改当前输入参数,重新得到当前输入参数对应的阻抗,直至当前输入参数满足预设范围。

67.当前多个输入参数对应的阻抗不符合阻抗预设范围,只须回到修改当前输入参数,即可重新得到当前输入参数对应的阻抗,去做tab走线的优化,直至当前输入参数满足预设范围,这样节省大量的时间人力。

68.需要说明的是,本发明技术方案中步骤s1

‑

s6均可以通过硬件或软件语言编程实现,实现的思路与本发明实施例中的步骤相对应,也可以通过其他方式实现,本发明在此不

做限制。

69.本发明通过建立多个输入参数与阻抗之间的对应关系,有效解决由于现有技术造成走线评估优化效率低的问题,有效地提高了走线评估的优化效率。

70.本发明技术方案中通过多个走线结构的阻抗仿真得到多个输入参数与阻抗的对应关系具体包括:仿真获得多个走线结构,每个走线结构对应的输入参数不同;根据获得多个走线结构仿真获取对应的阻抗,将得到的多个走线结构以及对应的阻抗建立多个输入参数与阻抗的对应关系,即通过多个输入参数不同的走线结构仿真结果建立多个输入参数与阻抗的对应关系,提高了多个输入参数与阻抗的对应关系的准确性以及可靠性,以便于提高走线评估的优化的准确性。

71.本发明技术方案中仿真的走线结构的数量与输入参数数量成正比,不同走线结构中,每一种输入参数均包括第一端点值、中间值、第二端点值,其中,第一端点值为输入参数的取值范围的最小值,第二端点值为输入参数的取值范围的最大值,中间值为输入参数的取值范围的最小值与最大值的一半,适应于多个输入参数的情况,而且进一步地提高了多个输入参数与阻抗的对应关系的准确性以及可靠性。

72.本发明技术方案中如果不满足,修改当前输入参数,重新得到当前输入参数对应的阻抗,直至当前输入参数满足预设范围,不需要重新进行走线结构创建,直接调整参数,即可获得当前输入参数对应的阻抗,有效地提高了走线评估的优化效率。

73.实施例二

74.如图11所示,本发明技术方案还提供了一种基于阻抗的走线评估优化装置,应用于印刷电路板中的球栅数组封装区域中,包括:

75.对应关系确定模块101,通过多个走线结构的阻抗仿真得到多个输入参数与阻抗的对应关系;

76.阻抗评估模块102,根据多个输入参数与阻抗的对应关系以及当前的输入参数,得到当前输入参数对应的阻抗,判断当前输入参数对应的阻抗是否满足预设范围,如果满足,则评估优化完成,如果不满足,则评估不通过。

77.如图12所示,对应关系确定模块101具体包括:

78.仿真子模块1011,仿真获得多个走线结构,每个走线结构对应的输入参数不同;

79.对应关系建立子模块1012,根据获得多个走线结构仿真获取对应的阻抗,将得到的多个走线结构以及对应的阻抗建立多个输入参数与阻抗的对应关系。

80.其中,在仿真子模块1011中,仿真的走线结构的数量与输入参数数量成正比。例如,如图6所示,当输入参数为六个时,仿真的走线结构的数量(case)可以为64个,也可以是其他数量,本发明在此不做限制。多个走线结构的仿真可以是在3d仿真软件中仿真多个bga区域tab走线结构。

81.输入参数包括但不限于走线宽度(tw,单位:mil)、走线间距(ts,单位:mil)、tab走线短边宽度(swtab,单位:mil)、tab走线长边宽度(lwtab,单位:mil)、tab走线长度(ltab,单位:mil)、同一走线之tab间距(ptab,单位:mil)、不同走线之面对面tab间距(stab,单位:mil)、tab走线近端参考层介电质厚度(h1,单位:mil)、tab走线远端参考层介电质厚度(h2,单位:mil)、印刷电路板材料的介电常数(dielectric constant,dk)、印刷电路板材料的损耗因子(loss tangent,df)。

82.不同走线结构中,每一种输入参数均包括第一端点值、中间值、第二端点值,其中,第一端点值为输入参数的取值范围的最小值,第二端点值为输入参数的取值范围的最大值,中间值为输入参数的取值范围的最小值与最大值的一半。如图6所示,输入参数tab走线近端参考层介电质厚度h1,取值范围为3

‑

5,则在仿真的走线结构中取值可以是3、4、5;输入参数tab走线远端参考层介电质厚度h2,取值范围为4

‑

12,则在仿真的走线结构中取值可以是4、8、12;印刷电路板材料的介电常数dk,取值范围为3

‑

4,则在仿真的走线结构中取值可以是3、3.5、4;tab走线长度ltab,取值范围为2

‑

6,则在仿真的走线结构中取值可以是2、4、6;tab走线短边宽度swtab,取值范围为5

‑

15,则在仿真的走线结构中取值可以是5、10、15;tab走线长边宽度lwtab,取值范围为5

‑

15,则在仿真的走线结构中取值可以是5、10、15;也可以是其他取值方式,取值时同一种输入参数的步长尽可能大一些,以便能够覆盖全部取值范围,具体地,如果仿真的走线结构的数量较多时,每一种输入参数的步长可以相对小一些,如果仿真的走线结构的数量较少时,每一种输入参数的步长可以相对大一些,以提高多个输入参数与阻抗的对应关系的准确性以及全面性。

83.进一步地,也可以将多个输入参数分别输入统计分析软件(例如jmp软件),通过jmp软件的反馈获取仿真的走线结构数量,以及仿真的走线结构数量中每一种输入参数的组合,本发明在此不做限制。

84.在对应关系建立子模块1012中,将仿真获得的多个tab走线结构的参数值及阻抗的仿真结果,可以通过非线性回归方程,建立多个输入参数与阻抗的对应关系,其中对应关系中包括各项输入参数对于输出阻抗的影响权重;也可以利用统计分析软件(例如jmp软件),使用jmp软件内的rsm(response surface methodology,反应曲面法)功能,如图6所示,mean代表输入参数变化量的中间值,sd(standard deviation,标准差)代表标准偏差,横坐标中

‑

1代表输入参数变化量的最小值,1代表输入参数变化量的最大值,纵坐标35~55代表阻抗值(impedance),random代表输入参数变化是随机的,normal代表是常态分布,通过统计分析软件分析输入参数和输出结果(阻抗)的关系,以及各个输入参数影响阻抗的比重,得到输入参数和阻抗之间的关系式,如图8所示(输入参数如图6所示)。

85.其中,在对应关系建立子模块1012中,可以在excel中建立tab走线多个输入参数和阻抗的单元格,将步骤s1得到的多个输入参数与阻抗的对应关系式写入excel公式,建立pcb板中bga区域tab走线设计评估工具。根据tab走线结构和选用额pcb板的材料,在pcb板中bga区域tab走线设计评估工具中输入各项参数,即可得到结果。根据多个输入参数与阻抗的对应关系式以及当前输入的多个输入参数,即可确定当前输入的多个输入参数对应的阻抗。在输入参数的选择中,可以选用比较常用的输入参数,例如输入参数tab走线近端参考层介电质厚度h1、输入参数tab走线远端参考层介电质厚度h2、印刷电路板材料的介电常数dk、tab走线长度ltab、tab走线短边宽度swtab、tab走线长边宽度lwtab,这样不仅能够减少输入参数变化需要重新建立输入参数与阻抗的对应关系的次数,而且使用方便,不需要经常改动,提高效率。

86.阻抗预设范围可以是40ohms+/

‑

5%以内(以ddr5走线为例,一般阻抗设计要求为40ohms),也可以根据实际情况进行调整,本发明在此不做限制。只要当前多个输入参数对应的阻抗符合阻抗预设范围,则完成pcb板中bga区域tab走线优化完成。

87.进一步地,如图13所示,本发明技术方案还提供的一种基于阻抗的走线评估优化

装置,还包括:

88.修改模块103,修改当前输入参数,重新得到当前输入参数对应的阻抗,直至当前输入参数满足预设范围。

89.当前多个输入参数对应的阻抗不符合阻抗预设范围,只须回到修改当前输入参数,即可重新得到当前输入参数对应的阻抗,去做tab走线的优化,直至当前输入参数满足预设范围,这样节省大量的时间人力。

90.本发明通过建立多个输入参数与阻抗之间的对应关系,有效解决由于现有技术造成走线评估优化效率低的问题,有效地提高了走线评估的优化效率。

91.本发明技术方案中通过多个走线结构的阻抗仿真得到多个输入参数与阻抗的对应关系具体包括:仿真获得多个走线结构,每个走线结构对应的输入参数不同;根据获得多个走线结构仿真获取对应的阻抗,将得到的多个走线结构以及对应的阻抗建立多个输入参数与阻抗的对应关系,即通过多个输入参数不同的走线结构仿真结果建立多个输入参数与阻抗的对应关系,提高了多个输入参数与阻抗的对应关系的准确性以及可靠性,以便于提高走线评估的优化的准确性。

92.本发明技术方案中仿真的走线结构的数量与输入参数数量成正比,不同走线结构中,每一种输入参数均包括第一端点值、中间值、第二端点值,其中,第一端点值为输入参数的取值范围的最小值,第二端点值为输入参数的取值范围的最大值,中间值为输入参数的取值范围的最小值与最大值的一半,适应于多个输入参数的情况,而且进一步地提高了多个输入参数与阻抗的对应关系的准确性以及可靠性。

93.本发明技术方案中如果不满足,修改当前输入参数,重新得到当前输入参数对应的阻抗,直至当前输入参数满足预设范围,不需要重新进行走线结构创建,直接调整参数,即可获得当前输入参数对应的阻抗,有效地提高了走线评估的优化效率。

94.实施例三

95.如图14所示,本发明技术方案还提供了一种电子设备,包括:存储器201,用于存储计算机程序;处理器202,用于执行所述计算机程序时实现实施例一中的一种基于阻抗的走线评估优化方法的步骤。

96.本技术实施例中的存储器201用于存储各种类型的数据以支持电子设备的操作。这些数据的示例包括:用于在电子设备上操作的任何计算机程序。可以理解,存储器201可以是易失性存储器或非易失性存储器,也可包括易失性和非易失性存储器两者。其中,非易失性存储器可以是只读存储器(rom,read only memory)、可编程只读存储器(prom,programmable read

‑

only memory)、可擦除可编程只读存储器(eprom,erasable programmable read

‑

only memory)、电可擦除可编程只读存储器(eeprom,electrically erasable programmable read

‑

only memory)、磁性随机存取存储器(fram,ferromagnetic random access memory)、快闪存储器(flashmemory)、磁表面存储器、光盘、或只读光盘(cd

‑

rom,compact disc read

‑

only memory);磁表面存储器可以是磁盘存储器或磁带存储器。易失性存储器可以是随机存取存储器(ram,random accessmemory),其用作外部高速缓存。通过示例性但不是限制性说明,许多形式的ram可用,例如静态随机存取存储器(sram,static random access memory)、同步静态随机存取存储器(ssram,synchronous static random access memory)、动态随机存取存储器(dram,dynamic random access memory)、

memory、磁表面存储器、光盘、或cd

‑

rom等存储器。

104.本领域普通技术人员可以理解:实现上述方法实施例的全部或部分步骤可以通过程序指令相关的硬件来完成,前述的程序可以存储于一计算机可读取存储介质中,该程序在执行时,执行包括上述方法实施例的步骤;而前述的存储介质包括:移动存储设备、rom、ram、磁碟或者光盘等各种可以存储程序代码的介质。或者,本技术上述集成的单元如果以软件功能模块的形式实现并作为独立的产品销售或使用时,也可以存储在一个计算机可读取存储介质中。基于这样的理解,本技术实施例的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台电子设备(可以是个人计算机、服务器、或者网络设备等)执行本技术各个实施例所述方法的全部或部分。而前述的存储介质包括:移动存储设备、rom、ram、磁碟或者光盘等各种可以存储程序代码的介质。

105.本发明通过建立多个输入参数与阻抗之间的对应关系,有效解决由于现有技术造成走线评估优化效率低的问题,有效地提高了走线评估的优化效率。

106.本发明技术方案中通过多个走线结构的阻抗仿真得到多个输入参数与阻抗的对应关系具体包括:仿真获得多个走线结构,每个走线结构对应的输入参数不同;根据获得多个走线结构仿真获取对应的阻抗,将得到的多个走线结构以及对应的阻抗建立多个输入参数与阻抗的对应关系,即通过多个输入参数不同的走线结构仿真结果建立多个输入参数与阻抗的对应关系,提高了多个输入参数与阻抗的对应关系的准确性以及可靠性,以便于提高走线评估的优化的准确性。

107.本发明技术方案中仿真的走线结构的数量与输入参数数量成正比,不同走线结构中,每一种输入参数均包括第一端点值、中间值、第二端点值,其中,第一端点值为输入参数的取值范围的最小值,第二端点值为输入参数的取值范围的最大值,中间值为输入参数的取值范围的最小值与最大值的一半,适应于多个输入参数的情况,而且进一步地提高了多个输入参数与阻抗的对应关系的准确性以及可靠性。

108.本发明技术方案中如果不满足,修改当前输入参数,重新得到当前输入参数对应的阻抗,直至当前输入参数满足预设范围,不需要重新进行走线结构创建,直接调整参数,即可获得当前输入参数对应的阻抗,有效地提高了走线评估的优化效率。

109.上述虽然结合附图对本发明的具体实施方式进行了描述,但并非对本发明保护范围的限制,所属领域技术人员应该明白,在本发明的技术方案的基础上,本领域技术人员不需要付出创造性劳动即可做出的各种修改或变形仍在本发明的保护范围以内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1