用于流水线控制的装置以及方法与流程

1.本发明涉及指令流水线(instruction pipeline),具体地涉及一种用于流水线控制的装置(apparatus)以及方法。

背景技术:

2.在电子装置中的存储器组织架构可包含多个层级,诸如寄存器(register)、高速缓存(cache)、主存储器以及辅助(auxiliary)存储器。由于最靠近中央处理单元的存储器层级存取速度最快但储存空间最小,因此存取速度由快到慢依序为寄存器、高速缓存、主存储器以及辅助存储器,而储存空间由大到小依序为辅助存储器、主存储器、高速缓存以及寄存器;

3.最外部的层级存取速度则最慢但储存空间最大。

4.在指令流水线的架构下运算时,中央处理单元可通过载入指令将位于高速缓存的数据载入至寄存器以供后续指令快速取得。然而,高速缓存内的数据仍是在执行载入指令的数个周期后才能在寄存器中就绪以供使用,这导致某些指令的执行需要被延迟而导致流水线调度出现“气泡(bubble)”,从而降低了中央处理单元在流水线指令的架构下运算的效能。尤其,现代的中央处理器利用较深的流水线阶段以达到较快的时钟同步频率,而上述问题在较深的流水线阶段的架构下尤其严重;

5.因此,需要一种新颖的方法以及装置,以在没有副作用或相对不会带来副作用的情况下最优化指令流水线的效能。

技术实现要素:

6.本发明的目的之一在于提供一种用于流水线(pipeline)控制的装置以及方法,以解决相关技术的问题。

7.本发明至少一个实施例提供用于流水线控制的装置。所述装置可包含预加载(preload)预测器、算术逻辑单元(arithmetic logic unit,alu)以及数据缓冲器,其中数据缓冲器耦合至预加载预测器与算术逻辑单元。预加载预测器用以判断载入指令是否符合至少一个特定条件,以产生预加载判断结果。算术逻辑单元用以进行算术逻辑运算,以及数据缓冲器用以提供数据给算数逻辑单元使用,其中算数逻辑单元从数据缓冲器中提取数据的速度快于算数逻辑单元从高速缓存中提取数据的速度。特别是,当所述预加载判断结果指出载入指令符合至少一个特定条件时,数据缓冲器依据载入指令所载有的信息从高速缓存中提取(fetch)预加载数据并且将预加载数据储存于所述数据缓冲器内,其中所述预加载数据为后续载入指令所请求的数据。

8.本发明至少一个实施例提供一种用于流水线控制的方法。所述方法可以包括:利用预加载预测器判断载入指令是否符合至少一个特定条件,以产生预加载判断结果;当预加载判断结果指出载入指令符合至少一个特定条件,数据缓冲器根据载入指令所载有的信息从高速缓存中提取预加载数据并且将预加载数据储存在数据缓冲器内,其中预加载数据

为后续载入指令所请求的数据;以及利用数据缓冲器提供预加载数据给算数逻辑单元进行算术逻辑运算,其中算数逻辑单元从数据缓冲器中提取数据的速度快于算数逻辑单元从高速缓存中提取数据的速度。

9.本发明的实施例所提供的装置以及方法能基于空间局部性(spatial locality)与时间局部性(temporal locality)有效地减少载入-使用指令对(load-use instruction pairs)所导致的延迟。特别地,本发明的实施例不会大幅增加额外成本,因此本发明能在没有副作用或相对不会带来副作用的情况下解决相关的技术问题。

附图说明

10.现在将通过示例的方式,参考附图来描述本发明构思的特定实施例,在附图中:

11.图1示出了根据本发明的实施例的装置在指令流水线的架构下运算的示意图。

12.图2示出了根据本发明的实施例的载入-使用数据缓冲器的示意图。

13.图3示出了根据本发明的实施例的载入-使用数据缓冲器的示意图。

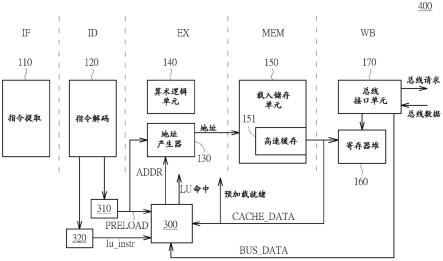

14.图4示出了根据本发明的实施例的装置在指令流水线的架构下运算的示意图。

15.图5示出了根据本发明的实施例的载入指令在图4所示的指令流水线的架构下的某些细节的示意图。

16.图6示出了根据本发明的实施例的用于流水线流水线控制的方法的流程图。

17.图7示出了根据本发明的实施例执行的预加载请求的流程图。

18.图8示出了根据本发明的实施例执行的载入指令的流程图。

具体实施方式

19.高速缓存(cache)是一种能快速存取的存储器,用来储存近期使用过或较容易被频繁使用的数据或指令。为了满足快速存取的需求,高速缓存可由静态随机存取存储器(static random access memory,简称sram)组成。然而,静态随机存取存储器仍需要在接收到存取地址的周期先锁存这个存取地址,并且直到下个周期才能回传对应的数据。

20.图1是根据本发明的实施例的装置100(例如中央处理单元)在指令流水线的架构下运算的示意图。在本实施例中,指令流水线的架构可以是五阶段管线,包含指令提取(instruction fetch,if)阶段、指令解码(instruction decode,id)阶段、指令执行阶段、存储器存取阶段以及数据写回阶段,其中以上阶段在图中分别标示为“if”、“id”、“exe”、“mem”以及“wb”以求简明。装置100首先可通过在其中运算的指令提取组件110(标示为“指令提取”以求简明)在指令提取阶段取得某一指令,继而进入指令解码阶段。在指令解码阶段,装置可利用其中的指令解码器120(标示为“指令解码”以求简明)对这个指令进行解码以取得这个指令所载有(carry)的信息诸如指令类型、基址(base address)、偏移值(offset)等,接着进入指令执行阶段。在指令执行阶段,若这个指令是载入指令,装置100可利用其中的地址产生器130依据这个指令所载有的基址与偏移值产生存取地址,再接着进入存储器存取阶段;而若这个指令是算术指令,所述装置可利用其中的算术逻辑单元(arithmetic logic unit,alu)140进行算数逻辑运算诸如算数指令所对应的运算。在存储器存取阶段,装置100可从其中的载入储存单元150(尤指载入储存单元150内的高速缓存151)提取对应于存取地址的数据,再接着进入数据写回阶段。在数据写回阶段,装置100可

将提取出的数据写回最靠近中央处理单元的存储器诸如寄存器堆(register file)160以供后续指令使用,其中若高速缓存151并未命中(例如高速缓存151并未储存有载入指令所请求的数据),装置100在数据写回阶段则可利用其中的总线接口单元170对外发出总线请求,以从外部存储器(例如硬式磁碟机、固态硬碟或外接辅助存储器)取得载入指令所请求的数据(例如图1所示的总线数据)。

21.在图1的实施例中,虽然载入指令能在存储器存取阶段从高速缓存151中取得数据,但是若某个算数指令在管线架构中与载入指令背靠背(back to back)地执行(例如算数指令紧跟在载入指令后面),这个算数指令仍需要等到下一个周期(例如等到载入指令进入数据写回阶段)才能使用从高速缓存中取得的数据。

22.表1

23.操作指令载入load r0,[r8];相加add r5,r0,#8;载入load r1,[r9];

[0024]

表1为一个指令组合的例子,其中表1的第一行的指令(以下称为第一载入指令)表示将高速缓存151中的地址[r8]的数据载入寄存器r0,表1的第二行的指令(以下称为相加指令)表示将寄存器r0的值加8的算术结果储存在寄存器r5,而表1的第三行的指令(以下称为第二载入指令)表示从快闪存储器中的地址[r9]的数据载入寄存器r1。

[0025]

表2

[0026] idexmemwb第一周期相加载入

ꢀꢀ

第二周期相加气泡载入 第三周期载入相加气泡载入

[0027]

表2为表1中的三个指令在流水线架构中的三个周期的调度,其中上述指令解码阶段、指令执行阶段、存储器存取阶段以及数据写回阶段在表2中分别标示为“id”、“exe”、“mem”以及“wb”以求简明。在第一周期,第一载入指令在指令执行阶段而相加指令在指令解码阶段。在第二周期,第一载入指令进入存储器存取阶段,然而由于此时第一载入指令所请求的数据尚未能从高速缓存151中取得,因此装置100会延迟相加指令进入指令执行阶段的时间,使得在第一载入指令与相加指令之间出现“气泡(bubble)”。在第三周期,由于第一载入指令进入数据写回阶段(表示寄存器r0的数据已就绪),因此相加指令可进入指令执行阶段以进行相关运算,而第二载入指令则可进入指令解码阶段。

[0028]

由于上述第一载入指令与相加指令为一对载入-使用(load-use)指令,即相加指令涉及第一载入指令且第一载入指令与相加指令背靠背地执行,导致相加指令必须等待载入指令所对应的数据(例如载入至寄存器r0的数据)后才能进入指令执行阶段,从而造成载入-使用停顿(stall),整体运算效率也受到影响。

[0029]

图2为依据本发明的实施例的载入-使用数据缓冲器200的示意图。在本实施例中,载入-使用数据缓冲器200可提供数据暂存空间,其中载入-使用数据缓冲器内部的数据暂存空间利用触发器(flip-flop)作为储存单元以达到单周期存取的目的,例如在接收到存取地址时,载入-使用数据缓冲器200可在当下的周期回传对应的数据供后续指令使用。基

于上述特性,载入-使用数据缓冲器200可用来移除上述载入-使用指令对(例如背靠背执行的第一载入指令与相加指令)所产生的载入-使用气泡。在本实施例中,载入-使用数据缓冲器200可包含数据储存区以及标签储存区,其中n组数据诸如data[0]、data[1]、

…

及data[n](n可为正整数)可被分别储存在数据储存区的n个条目(entry),而分别对应于n组数据的n个地址诸如tag[0]、tag[1]、

…

及tag[n]则可分别被储存在标签储存区的n个条目。另外,标签储存区的n个条目的每一条目的状态可由各自的有效位vld以及锁定位lock来判断。例如,当某一条目的有效位为“1”,表示这个条目储存的地址与对应的数据是有效的或可使用的;而当这个条目的有效位为“0”,表示这个条目储存的地址所对应的数据是无效的或不可使用的。又例如,当某一条目的锁定位为“1”,表示这个条目储存的地址以及对应的数据处于锁定状态(例如正在被更新因此不允许使用);而当这个条目的锁定位为“0”,表示这个条目储存的地址以及对应的数据并未处于锁定状态。具体来说,有效位vld[0]与锁定位lock[0]可用来表示标签地址tag[0]与数据data[0]的状态,有效位vld[1]与锁定位lock[1]可用来表示标签地址tag[1]与数据data[1]的状态,而依此类推,有效位vld[n]与锁定位lock[n]可用来表示标签地址tag[n]与数据data[n]的状态。

[0030]

在本实施例中,当载入-使用数据缓冲器200收到存取地址addr,载入-使用数据缓冲器200可将存取地址addr的至少一部分与储存在载入-使用数据缓冲器200的标签储存区的标签地址逐一进行比对,以确认存取地址addr所请求的数据是否已被储存在载入-使用数据缓冲器200内。举例来说,当n组数据的每一组数据为64位(bit),载入-使用数据缓冲器200可将存取地址addr的第31位至第3位(可表示为addr[31:3])与标签地址tag[0]、tag[1]、

…

、及tag[n]逐一比对以产生n个比对结果。另外,载入-使用数据缓冲器200内的选择控制器220可依据这n个比对结果产生载入-使用缓冲器(例如对这n个比对结果进行或逻辑处理以产生有效信号lub_valid),其中若这n个比对结果中的任一者指出其比对结果为“命中(hit)”,有效信号lub_valid可指出载入-使用数据缓冲器200命中(表示存取地址addr所请求的数据可在载入-使用数据缓冲器200被找到)。特别是,当有效信号lub_valid指出载入-使用数据缓冲器200命中,选择控制器220可依据这n个比对结果产生一选择信号sel,以使载入-使用数据缓冲器200内的选择电路诸如多工器230依据选择信号sel选择相对应的条目以输出对应的数据。若这n个比对结果全部都为“错过(miss)”,表示存取地址addr所请求的数据并未储存于载入-使用数据缓冲器200内,载入-使用数据缓冲器200内的载入-使用缓冲(load-use buffer,简称lub)控制器210则可从高速缓存151中取得缓存数据或者通过总线接口单元170从外部取得总线数据,但本发明不限于此。

[0031]

当存取地址addr从高速缓存151或外部存储器取得存取地址addr所请求的新数据后,lub控制器210可将这个新数据储存至载入-使用数据缓冲器200内的数据储存区。这样,当载入-使用数据缓冲器200在未来再次接收到存取地址addr时,就能快速地提供这个新数据。需注意的是,若载入-使用数据缓冲器200内的储存空间已满,lub控制器210需要依据一更新替代方案将其中一个条目内的数据舍弃才能提供储存空间给这个新数据。因此,这n组数据中的每一组数据可对应于一个权重值,该权重值用以判断对应的数据被使用的频率,以供lub控制器210由此进行数据更新。例如,n组数据中的某组数据可能因为长时间未被使用而具有较低的权重值,而n组数据中的另一组数据可能因为较频繁地被使用而具有较高的权重值。当载入-使用数据缓冲器200内的储存空间已满但lub控制器210仍决定将一组尚

未储存于载入-使用数据缓冲器200内的新数据储存至载入-使用数据缓冲器200内,lub控制器210可选择将这n组数据中权重值最低的那组数据舍弃,并且以上述新数据取代。因此,本方法能够借助于数据的时间局部性,以容许被频繁使用的数据被储存在存取速度较快的载入-使用数据缓冲器200,从而最佳化装置100的整体效能。

[0032]

表3

[0033]

i0初始r2,10;i1载入r1,[r0],#16;i2相加r5,r4,r1;i3相加r3,r1,r2;i4相减r2,r2,1;i5返回i1

[0034]

表3为另一个指令组合的示例,其中表3所示的指令组合包括六个指令并且依次编号为i0、i1、i2、i3、i4及i5。指令i0表示将数值“10”写入寄存器r2作为初始值,指令i1表示将高速缓存151中地址[r0]的数据载入寄存器r1,指令i2表示将寄存器r4的值加上寄存器r1的值的结果写入寄存器r5,指令i3表示将寄存器r1的值加上寄存器r2的值的结果写入寄存器r3,指令i4表示将寄存器r2的值减去数值“1”的结果写入寄存器r2,而指令i5表示程序流程回到指令i1。由表3可看出指令i1及i2为一对载入-使用指令,然而图2所示的载入-使用数据缓冲器200仍无法避免表3所示的指令组合发生载入-使用停顿。详细来说,指令i2被执行时会将前一次的基址[r0]加上16以作为本次的目标地址。例如,在第一个周期时,指令i2将高速缓存151中地址[r0]的数据载入寄存器r1;而在第二周期时,指令i2则将高速缓存151中的地址[r0+16]的数据载入寄存器r1。根据上述可知,虽然指令i2被重复地执行,但每次的目标地址都被平移了“16”,因此载入-使用数据缓冲器200总是会得到“错过”的结果而无法避免载入-使用停顿的情况发生。

[0035]

图3为根据本发明的实施例的载入-使用数据缓冲器300的示意图,其中载入-使用数据缓冲器300可视为图2所示的载入-使用数据缓冲器200的增强型版本。具体来说,载入-使用数据缓冲器300是基于载入-使用数据缓冲器200的架构,针对标签储存区的n个条目的每一条目的状态位进行改良。例如,除了有效位vld以及锁定位lock外,n个条目的每一条目的状态可额外根据一就绪位rdy诸如rdy[0]、rdy[1]、rdy[2]、

…

及rdy[n]来判断。此外,载入-使用数据缓冲器300可另包含一选择电路例如多工器240,其中多工器240是通过内部路径耦合到数据缓冲器内部的数据暂存空间(特别是耦合到多工器230的输出端子),并且通过旁通路径耦合至载入-使用数据缓冲器300外部的高速缓存151。当载入-使用数据缓冲器300的数据暂存空间并未储存载入数据时(例如对存取地址addr[index_range]进行的比对所产生的n个比对结果全部都为“错过”),载入-使用数据缓冲器300可根据上述更新替代方案选择某一条目例如第i个条目(i为0到n的范围内的整数),以根据载入数据更新数据暂存空间内的数据诸如第i个条目所储存的数据。在本实施例中,存取地址addr中被用来进行比对的位的范围index_range可根据各个条目所储存的数据的大小而变化,为简明起见在此不赘述。如果载入数据可在高速缓存151中被找到,lub控制器210可从高速缓存151中取得载入数据(在图3中以缓存数据cache_data表示);而如果载入数据在高速缓存151无法被找到,lub控制器210则可另外通过总线接口单元170取得载入数据(在图3中以总线数据bus_

data表示)。

[0036]

需注意的是,在lub控制器210取得缓存数据cache_data后,对被选到的条目进行的数据更新不能立即完成。在本实施例中,多工器230可根据被选择到的条目的就绪位(例如第i个条目的就绪位rdy[i])从内部路径与旁通路径中选择其中之一,以在指令执行阶段向算术逻辑单元140提供载入指令(例如上述第一载入指令)所请求的载入数据。例如,当载入-使用数据缓冲器300的数据暂存空间并未储存载入数据但高速缓存151储存载入数据时,lub控制器210可将第i个条目的就绪位rdy[i]由“0”更新为“1”,而多工器240可使得旁通路径能够容许算数逻辑单元140在数据暂存空间内的数据(例如上述第i个条目的数据)尚未更新完成的情况下从高速缓存151中取得载入数据(例如缓存数据cache_data)。又例如,当载入-使用数据缓冲器300的数据暂存空间储存载入数据时,就绪位rdy[i]可被维持在“0”,而多工器230可使得内部路径能够容许算数逻辑单元从数据暂存空间中取得载入数据。

[0037]

图4为依据根据本发明的实施例的装置400(例如中央处理单元)在指令流水线的架构下运算的示意图,其中装置400可视为图1所示装置的增强型版本。在本实施例中,装置400可包含预加载(preload)预测器310、载入-使用指令检测器320、以及图3所示载入-使用数据缓冲器300。预加载预测器310可用来判断载入指令是否符合至少一个特定条件,以产生预加载判断结果preload。载入-使用数据缓冲器300可耦合到预加载预测器310,并且可另外耦合到算术逻辑单元140以提供资料给算数逻辑单元140使用。另外,载入-使用指令检测器320可检测该载入指令与紧跟在其后的后续指令是否为载入-使用指令对,以产生载入-使用侦测结果lu_instr,其中当载入-使用侦测结果lu_instr指出载入指令与后续指令为载入-使用指令对,表示后续指令涉及载入指令所请求的数据。

[0038]

当一个指令组合中包含多个载入指令,且多个载入指令所对应的存取地址以升序(ascending)排列或以降序(descending)排列,例如表3会被反复地执行指令i1,图1所示的装置100即使借助于图2所示的载入-使用缓冲器200,仍然无法避免在指令流水线的过程中产生气泡。在本实施例中,当预加载判断结果preload指出载入指令符合至少一个特定条件,载入-使用数据缓冲器300可依据载入指令所载有的信息消息从高速缓存151中提取预加载数据并且将预加载数据储存在载入-使用数据缓冲器300内,其中预加载数据为后续载入指令所请求的数据。例如,当预加载预测器310检测到上述以升序排列或以降序排列的载入指令,且载入-使用指令检测器检测到载入指令与后续指令为载入-使用指令对,预加载预测器310可对载入-使用数据缓冲器300发出预加载请求,而lub控制器210可据以触发预加载流程以根据在指令解码阶段取得的载入-使用信息对载入-使用数据缓冲器300进行存取。当载入-使用数据缓冲器300针对存取地址addr进行比对的结果命中(在图4中标示为“lu命中”),载入-使用数据缓冲器300可在载入指令在指令执行阶段时输出目标数据,以容许算术逻辑单元140在后续指令进入指令执行阶段时取用目标数据。当载入指令所请求的目标数据未能在载入-使用数据缓冲器300中找到,预加载请求可在存储器存取阶段检查目标数据是否能在高速缓存151中找到,其中若高速缓存151命中(表示可找到目标数据),目标数据(例如缓存数据cache_data)可先被预加载至载入-使用数据缓冲器300,也可另外利用图3所示的就绪位rdy[i]的控制将目标数据直接输出(标示为“预加载就绪”)。当高速缓存151错过(即目标数据未能在高速缓存151中找到),装置400可通过总线接口单元170发出

总线请求,以从外部的储存装置取得目标数据(标示为“总线数据”)。

[0039]

图5根据本发明的实施例绘示载入指令根据图4所示的指令流水线的架构下的某些细节,其中图5为简明起见仅展示指令解码阶段、指令执行阶段以及存储器存取阶段。在本实施例中,预加载预测器根据载入指令的至少一个字段产生预加载判断结果,以及预加载判断结果preload用以指出载入指令所对应的载入地址在载入指令执行完成后是否被更新,其中预加载数据对应于更新载入地址所产生的更新后载入地址,以及当预加载判断结果preload指出载入地址在载入指令执行完成后被更新时,载入指令符合至少一个特定条件。在本实施例中,当载入指令被解码后得到了后处理递增(post-increment)字段或后处理递减(post-decrement)字段,即表示载入指令符合至少一个特定条件,其中上述后处理递增字段可包含字段inc及字段p,而上述后处理递减字段可包含字段dec及字段p。此外,载入指令被解码过后可载有基址(在图5中标示为“基址寄存器”)以及偏移值,且当预加载判断结果preload指出载入地址在载入指令执行完成后被更新时,更新后载入地址等于载入地址加上偏移值或等于载入地址减去偏移值。例如,当载入指令被解码后得到了字段inc及字段p,表示载入指令执行完成后基址可被更新为基址加上偏移值;而当载入指令被解码过后得到了字段dec及字段p,表示载入指令执行完成后基址可被更新为基址减去偏移值。

[0040]

在本实施例中,地址产生器130可依据预加载判断结果preload产生载入指令所对应的载入地址。如图5所示,地址产生器130可包含第一选择器例如多工器131、第二选择器例如多工器132、以及耦合至多工器131及132的加总电路133。多工器131可用来根据预加载判断结果preload从载入指令所载有的基址addr(n)与先前载入指令所对应的先前载入地址addr(n-1)中选择最终基址,而多工器132可用来依据预加载判断结果preload从载入指令所载有的偏移值offset(n)与先前载入指令所载有的先前偏移值offset(n-1)中选择最终偏移值,其中加总电路133用来将最终基址加上(或减去)最终偏移值以产生载入地址(可称为“最终地址”)。特别是,当预加载判断结果preload指出载入地址在载入指令执行完成后会被更新时(例如preload的逻辑值为“1”),多工器131选择先前载入地址addr(n-1)作为最终基址,以及多工器132选择先前偏移值offset(n-1)作为最终偏移值。另外,当预加载判断结果preload指出载入地址在载入指令执行完成后不会被更新时(例如preload的逻辑值为“0”),多工器131选择基址addr(n)作为最终基址,以及多工器132选择偏移值offset(n)作为最终偏移值。需注意的是,本实施例在载入指令被解码过后得到了字段inc及字段p的情况作为例子进行说明,但本发明不限于此,其中本领域相关技术人员可依此类推得知在载入指令被解码过后得到了字段dec及字段p的情况下的相关细节,为简明起见在此不赘述。

[0041]

表4

[0042][0043]

表4为表3中的某些指令在流水线架构中的三个周期的过程,其中上述指令解码阶段、指令执行阶段、存储器存取阶段以及数据写回阶段在表4中分别标示为“id”、“exe”、“mem”以及“wb”以求简明。在第一周期,载入指令i1在指令执行阶段载入地址0x00的数据,而相加指令i2是在指令解码阶段,其中由于载入指令i1与相加指令i2为一对载入-使用指令且载入指令i1的存取地址为升序排列(每执行完成即对存取地址平移16),因此预加载预测器310可发出预加载请求。在第二周期,载入指令i1进入存储器存取阶段,相加指令i2进入指令执行阶段,而相加指令i3则进入指令解码阶段,其中于相加指令i2在指令执行阶段的同时,预加载请求可将存取地址0x10(对存取地址0x00平移16后取得的地址)的数据预加载至载入-使用数据缓冲器300中(标示为预加载0x10)。在第三周期,载入指令i1进入数据写回阶段,相加指令i2进入存储器存取阶段,相加指令i3进入指令执行阶段,而相减指令i4进入指令解码阶段。经过数个周期后,返回指令i5使得程序流程再次回到载入指令i1。由于存取地址0x10的数据已被预加载至载入-使用数据缓冲器300中,因此在第m周期(m为正整数)载入指令i1可得到载入使用缓冲器命中的结果。类似地,在第m+1周期,相加指令i2在指令执行阶段的同时,预加载请求可将存取地址0x20(对存取地址0x10平移16后取得的地址)的数据预加载至载入-使用数据缓冲器300中(标示为预加载0x20),因此在后续周期执行载入指令i1时即可得到。载入使用缓冲器命中的结果。由于第m周期至第m+2周期的运算与第一周期至第三周期类似,为简明起见相关细节不重复赘述。

[0044]

需注意的是,高速缓存151典型地以静态随机存取存储器来实施,而本发明的载入-使用数据缓冲器300可采用触发器作为储存单元。因此,算数逻辑单元140从载入-使用数据缓冲器300中提取数据的速度快于算数逻辑单元140从高速缓存151中提取数据的速度。基于上述特性,当某一载入指令在指令执行阶段得到载入-使用缓冲器命中的结果(即这个载入指令所请求的数据可在载入-使用数据缓冲器300中找到),载入-使用数据缓冲器300可在单周期内输出这个载入指令所请求的数据,从而避免在指令流水线的排程中产生气泡。特别是,当某一载入指令被反复地执行并且每一次执行时的目标地址以升序排列或降序排列时,表示后续即将执行的载入指令的目标地址是可预测的。本发明的预加载预测

器310能基于这样的空间局部性发出预加载请求,以将这些升序排列或降序排列的目标地址的数据在需要使用之前即提早被搬移至载入-使用数据缓冲器300内,从而避免载入-使用停顿的问题。

[0045]

图6为根据本发明的实施例的一种用于流水线控制的方法的工作流程,其中所述方法可应用于图4所示的装置400。需注意的是,图6所示的工作流程仅作为说明的目的,并非对本发明的限制。特别是,一个或多个步骤可根据图6所示的工作流程中被增加、删除或修改。此外,只要不妨碍整体结果,这些步骤并非必须完全依照图6所示的顺序执行。

[0046]

在步骤s610中,装置400可利用预加载预测器310判断载入指令是否符合至少一个特定条件,以产生预加载判断结果preload。

[0047]

在步骤s620中,当预加载判断结果preload指出载入指令符合至少一个特定条件,装置400可利用载入-使用数据缓冲器300根据载入指令所载有的信息从高速缓存151中提取预加载数据并且将预加载数据储存于载入-使用数据缓冲器300内,其中预加载数据为一后续载入指令所请求的数据。

[0048]

在步骤s630中,装置400可利用载入-使用数据缓冲器400提供预加载数据给算数逻辑单元进行算术逻辑运算,其中算数逻辑单元从数据缓冲器中提取数据的速度快于算数逻辑单元从高速缓存中提取数据的速度。

[0049]

图7为依据本发明的实施例执行预加载请求的工作流程,其中预加载请求可由图4所示的预加载预测器310发出,而工作流程可由图3所示的lub控制器210控制,但本发明不限于此。需注意的是,图7所示的工作流程仅作为说明目的,并非对本发明的限制。特别是,一个或多个步骤可在图7所示的工作流程中被增加、删除或修改。此外,只要不妨碍整体结果,这些步骤并非必须完全依照图7所示的顺序执行。

[0050]

在步骤s700中,预加载请求开始。

[0051]

在步骤s702中,lub控制器210可以检查是否命中lub(例如载入-使用数据缓冲器300),以产生lub检查结果。

[0052]

在步骤s704中,若lub检查结果显示为“是”,工作流程进入步骤s722;若lub检查结果显示为“否”,工作流程进入步骤s706。

[0053]

在步骤s706中,lub控制器210可以将有效位vld[i]设为“1”,将就绪位设为“0”,并且将锁定位lock[i]设为“1”。

[0054]

在步骤s708中,lub控制器210可以检查是否命中缓存(例如高速缓存151),以产生缓存检查结果。

[0055]

在步骤710中,若缓存检查结果显示为“是”,工作流程进入步骤s712;若缓存检查结果显示为“否”,工作流程进入步骤s720。

[0056]

在步骤s712中,lub控制器210可以从缓存(例如高速缓存151)中预加载数据至lub(例如载入-使用数据缓冲器300)。

[0057]

在步骤s714中,lub控制器210可将有效位vld[i]设为“1”,将就绪位设为“1”,并且将锁定位lock[i]设为“1”。

[0058]

在步骤s716中,lub控制器210可以使用sram数据(例如快取数据cache_data)更新lub数据。

[0059]

在步骤s718中,lub控制器210可以将有效位vld[i]设为“1”,将就绪位设为“0”,并

且将锁定位lock[i]设为“0”。

[0060]

在步骤s720中,lub控制器210可以将有效位vld[i]设为“0”,将就绪位设为“0”,并且将锁定位lock[i]设为“0”。

[0061]

在步骤s720中,预加载请求结束。

[0062]

图8为根据本发明的实施例的执行载入指令的工作流程,其中载入指令是可应用于图4所示的装置400。需注意的是,图8所示的工作流程仅作为说明的目的,而不是限制本发明。特别是,一个或多个步骤可以在图8所示的工作流程中被增加、删除或修改。此外,只要不影响整体结果,这些步骤并非必须完全按照图8所示的顺序执行。

[0063]

在步骤s800中,载入指令开始。

[0064]

在步骤s802中,装置400可以检查是否命中lub(例如载入-使用数据缓冲器300)以产生lub结果。

[0065]

在步骤s804中,若lub结果显示为“是”,工作流程进入步骤s806;若lub结果显示为“否”,工作流程进入步骤s818。

[0066]

在步骤s806中,装置400可判断锁定位lock[i]是否为“1”。若判断结果显示为“是”,工作流程进入步骤s812;若判断结果显示为“否”,工作流程进入步骤s808。

[0067]

在步骤s808中,装置400可以更新替代方案(例如更新上述各个条目所对应的权重值)。

[0068]

在步骤s810中,装置400可以利用载入-使用数据缓冲器300对核心流水线回传lub数据(例如在载入-使用数据缓冲器300中被命中的条目的数据)并且宣称lub数据有效(例如以逻辑值“1”输出有效信号lub_valid)。

[0069]

于步骤s812中,装置400可检查lub预加载是否正在进行中(例如检查对应的条目的就绪位rdy[i])。

[0070]

于步骤s814中,装置400可判断就绪位rdy[i]是否为“1”。若判断结果显示为“是”,工作流程进入步骤s816;若判断结果显示为“否”,工作流程进入步骤s824。

[0071]

在步骤s816中,装置400可对核心管线回传sram数据(例如从高速缓存151中提取的快取数据cache_data)并且宣称lub数据有效(例如以逻辑值“1”输出有效信号lub_valid)。

[0072]

在步骤s818中,装置400可判断载入指令与跟在其后的后续指令是否为载入-使用指令对(标示为“lu_instr?”以求简明)。若判断结果显示为“是”,工作流程进入步骤s820;若判断结果显示为“否”,工作流程进入步骤s824。

[0073]

在步骤s820中,装置400可依据替代方案(例如更新上述各个条目所对应的权重值)选择条目索引i(即选择第i个条目)。

[0074]

在步骤s822中,装置400可将第i个条目的锁定位lock[i]设为“1”。

[0075]

在步骤s824中,装置400可检查是否命中缓存(例如是否命中高速缓存151)以产生缓存检查结果。

[0076]

在步骤s826中,若缓存判断结果显示为“是”,工作流程进入步骤s828;若缓存判断结果显示为“否”,工作流程进入步骤s836。

[0077]

在步骤s828中,装置400可回传缓存数据诸如cache_data给核心流水线。

[0078]

在步骤s830中,装置400可判断lub是否命中(例如载入-使用数据缓冲器300是否

命中)。若判断结果显示为“否”,工作流程进入步骤s844;若判断结果显示为“是”,工作流程进入步骤s832。

[0079]

在步骤s832中,装置400可用sram数据(例如快取数据cache_data)更新lub数据(例如第i个条目的data[i])。

[0080]

在步骤s834中,装置400可将第i个条目的锁定位lock[i]设为“0”。

[0081]

在步骤s836中,装置400可通过总线接口单元170发送请求例如总线请求给总线,并且回传总线接口单元170取得的总线数据给核心流水线。

[0082]

在步骤s838中,装置400可判断lub是否命中(例如载入-使用数据缓冲器300是否命中)。若判断结果显示为“否”,工作流程进入步骤s844;若判断结果显示为“是”,工作流程进入步骤s840。

[0083]

在步骤s840中,装置400可用总线数据更新lub数据(例如第i个条目的data[i])。

[0084]

在步骤s842中,装置400可将第i个条目的锁定位lock[i]设为“0”。

[0085]

在步骤s844中,载入指令结束。

[0086]

总结来说,基于时间局部性(例如某些数据近期被使用过或频繁地被使用)与空间局部性(例如某些地址的数据是预期将会被使用的),本发明能提前将某些数据搬移至存取速度较快的载入-使用数据缓冲器中,以容许在出现载入-使用指令对时能在不产生气泡或较不容易产生气泡的情况下执行指令流水线的运算,从而降低载入-使用停顿发生的机率。特别的,本发明的实施例不会大幅地增加额外成本,因此本发明能在没有副作用或相对不会带来副作用的情况下解决相关技术的问题。

[0087]

以上所述仅为本发明的较优实施例,根据发明申请专利范围所做出的均等同变化与修饰,均应当属于本发明的涵盖范围。

[0088]

【符号说明】

[0089]

100:装置

[0090]

110:指令提取

[0091]

120:指令解码

[0092]

130:地址产生器

[0093]

131:多工器

[0094]

132:多工器

[0095]

133:加总电路

[0096]

140:算术逻辑单元

[0097]

150:载入储存单元

[0098]

151:高速缓存

[0099]

160:寄存器堆

[0100]

170:总线接口单元

[0101]

200:载入-使用数据缓冲器

[0102]

210:lub控制器

[0103]

220:选择控制器

[0104]

230:多工器

[0105]

240:多工器

[0106]

300:载入-使用数据缓冲器

[0107]

310:预加载预测器

[0108]

320:载入-使用指令侦测器

[0109]

400:装置

[0110]

preload:预加载判断结果

[0111]

lu_instr:载入-使用侦测结果

[0112]

cache_data:缓存数据

[0113]

bus_data:总线数据

[0114]

addr:存取地址

[0115]

valid[0]~valid[n]:有效位

[0116]

lock[0]~lock[n]:锁定位

[0117]

tag[0]~tag[n]:标签地址

[0118]

data[0]~data[n]:数据

[0119]

sel:选择信号

[0120]

lub_valid:有效信号

[0121]

addr(n):基址

[0122]

addr(n-1):先前载入地址

[0123]

offset(n]:偏移值

[0124]

offset(n-1):先前偏移值

[0125]

inc,p:字段

[0126]

s610~s640,s700~s722,s800~s844:步骤

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1