基于低延迟的精确频率输出方法及系统

1.本发明涉及频率调节领域,尤其涉及一种基于低延迟的精确频率输出方法及系统。

背景技术:

2.直接数字频率合成器(dds)电路由相位累加器和相位-幅度转换器组成。相位累加器由一个加法器和一个反馈寄存器组成,用于累加频率控制字和控制信号输出频率。相位-幅度转换器允许将输入角度映射为三角值,这通常是使用基于坐标旋转数字计算机(cordic)的算法实现的。目前,dds电路设计的重点是产生以16位定点数字表示的10-5阶正弦/余弦波信号输出。然而,在诸如精密仪器、图像视觉处理和三维机器人等实时控制领域,通常需要生成更精确的正弦/余弦波输出。为了使用cordic算法生成由32位定点数字表示的10-10

阶超高精度正弦/余弦值,至少需要32级迭代,因此输出延迟必须至少为32个时钟周期。目前,超高精度dds通常是在dsp或微处理器的基础上通过浮点运算实现的,整个计算过程将消耗大量处理器资源和较长的计算时间,难以适应时序要求严格的应用。

3.上述内容仅用于辅助理解本发明的技术方案,并不代表承认上述内容是现有技术。

技术实现要素:

4.本发明的主要目的在于,解决现有技术中,数字频率合成器的计算过程需要消耗大量处理器资源和较长计算时间的技术问题。

5.为实现上述目的,本发明提供一种基于低延迟的精确频率输出方法,包括:

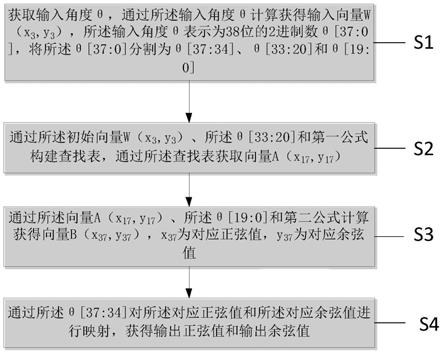

6.s1:获取输入角度θ,通过所述输入角度θ计算获得输入向量w(x3,y3),所述输入角度θ表示为38位的2进制数θ[37:0],将所述θ[37:0]分割为θ[37:34]、θ[33:20]和θ[19:0];

[0007]

s2:通过所述初始向量w(x3,y3)、所述θ[33:20]和第一公式构建查找表,通过所述查找表获取向量a(x

17

,y

17

);

[0008]

s3:通过所述向量a(x

17

,y

17

)、所述θ[19:0]和第二公式计算获得向量b(x

37

,y

37

),x

37

为对应正弦值,y

37

为对应余弦值;

[0009]

s4:通过所述θ[37:34]对所述对应正弦值和所述对应余弦值进行映射,获得输出正弦值和输出余弦值。

[0010]

优选地,步骤s1具体为:

[0011]

s11:将所述输入角度θ的值限定为[0,π/8),所述输入角度θ的弧度值表示为其中bk表示输入角度θ中第k位对应的二进制数,bk∈{0,1},k表示输入角度θ的位数,2≤k≤n,n的值为35;k=2时,取所述输入角度θ的第5位;k=35时,取所述输入角度θ的第38位;

[0012]

s12:令输入角度θ的位数k对应的位值为:rk=2b

k-1,则所述输入角度θ表示为:

[0013][0014]

其中,为初始角度,

[0015]

s13:通过所述初始角度计算获得缩放因子kn,计算公式如下:

[0016][0017]

s14:通过所述缩放因子kn计算获得输入向量w(x3,y3),计算公式如下所示:

[0018][0019]

其中,(x0,y0)=(kn,0)。

[0020]

优选地:

[0021]

所述第一公式的表达式如下:

[0022][0023]

其中,xk表示输入角度θ的位数k对应向量的横坐标,yk表示输入角度θ的位数k对应向量的纵坐标。

[0024]

优选地,步骤s2具体为:

[0025]

s21:将所述θ[33:20]划分为θ[33:27]和θ[26:20],获得所述θ[26:20]对应的r3至r9的值,以及所述θ[33:27]对应的r

10

至r

16

的值;

[0026]

s22:将所述初始向量w(x3,y3)以及r3至r9输入所述第一公式进行迭代计算,构建第一查找表,所述第一查找表表示为

[0027]

s23:将(x

10

,y

10

)以及r

10

至r

16

输入所述第一公式进行迭代计算,构建第二查找表,所述第二查找表表示为

[0028]

s24:所述第一查找表和所述第二查找表组合获得所述查找表,所述查找表表示为

[0029]

s25:获取所述查找表中的所述向量a(x

17

,y

17

)。

[0030]

优选地,步骤s3具体为:

[0031]

s31:获取所述θ[19:0]对应的r

17

至r

36

的值;

[0032]

s32:将所述向量a(x

17

,y

17

)以及r

17

至r

36

输入所述第二公式进行迭代计算,获得x

37

和y

37

的值,所述第二公式的表达式如下:

[0033][0034]

其中,m的值为17,s的值为20。

[0035]

一种基于低延迟的精确频率输出系统,用于实现上述的基于低延迟的精确频率输出方法,包括:辅助相位累加器、主相位累加器、输入模块、输出模块和时钟模块;

[0036]

所述输入模块与所述辅助相位累加器电性连接,所述辅助相位累加器与所述主相位累加器电性连接,所述主相位累加器与所述输出模块电性连接,所述时钟模块与所述辅助相位累加器和所述主相位累加器电性连接。

[0037]

优选地:

[0038]

所述输入模块包括输入信号a和输入信号b;

[0039]

所述输出模块的输出值f

out

=(f

tw

+a/b)/2n·fclk

,其中f

clk

为所述时钟模块提供的时钟,n为相位累加器位数,f

tw

为频率控制字,所述频率控制字为十进制,其值由所述输入信号a的值和所述输入信号b的值决定。

[0040]

本发明具有以下有益效果:

[0041]

1、改进了传统的相位累加器设计,允许频率控制字不再是整数,而可以是十进制,其值由用户定义的a和b的值确定,从而可以实现用户所期望的精确频率的输出;

[0042]

2、采用低时延cordic算法设计,建立查找表,对查找表进行压缩,减小电路面积;然后在查找表的基础上进行合并迭代,减小了输出时延。

附图说明

[0043]

图1为本发明实施例方法流程图;

[0044]

图2为传统的相位累加器;

[0045]

图3为基于低延迟的精确频率输出系统;

[0046]

本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

[0047]

应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

[0048]

参照图1,为了缩短数字频率合成器的输出延迟,降低硬件资源消耗,本发明提供一种基于低延迟的精确频率输出方法,包括:

[0049]

s1:获取输入角度θ,通过所述输入角度θ计算获得输入向量w(x3,y3),所述输入角度θ表示为38位的2进制数θ[37:0],将所述θ[37:0]分割为θ[37:34]、θ[33:20]和θ[19:0];

[0050]

s2:通过所述初始向量w(x3,y3)、所述θ[33:20]和第一公式构建查找表,通过所述查找表获取向量a(x

17

,y

17

);

[0051]

s3:通过所述向量a(x

17

,y

17

)、所述θ[19:0]和第二公式计算获得向量b(x

37

,y

37

),x

37

为对应正弦值,y

37

为对应余弦值;

[0052]

s4:通过所述θ[37:34]对所述对应正弦值和所述对应余弦值进行映射,获得输出

正弦值和输出余弦值。

[0053]

本实施例中,步骤s1参照cordic算法的基本思想,cordic算法是一种不断循环迭代逼近目标值的的计算方法,当以初始角度开始坐标旋转,并且每次旋转角度依次选择为2-3

(弧度)、2-4

(弧度)、

…

、2-k

(弧度),且旋转方向直接由输入角度θ的二进制表示时的位值rk决定。当rk=1时,就逆时针方向旋转2-k

(弧度),反之rk=-1时,则顺时针方向旋转2-k

(弧度),这样就可以由下式迭代产生输入角的正余弦值;

[0054]

步骤s1具体为:

[0055]

s11:将所述输入角度θ的值限定为[0,π/8),所述输入角度θ的弧度值表示为其中bk表示输入角度θ中第k位对应的二进制数,bk∈{0,1},k表示输入角度θ的位数,2≤k≤n,n的值为35;k=2时,取所述输入角度θ的第5位;k=35时,取所述输入角度θ的第38位;

[0056]

s12:令输入角度θ的位数k对应的位值为:rk=2b

k-1,则所述输入角度θ表示为:

[0057][0058]

其中,为初始角度,

[0059]

s13:通过所述初始角度计算获得缩放因子kn,计算公式如下:

[0060][0061]

s14:通过所述缩放因子kn计算获得输入向量w(x3,y3),计算公式如下所示:

[0062][0063]

其中,(x0,y0)=(kn,0)。

[0064]

本实施例中,所述第一公式的表达式如下:

[0065][0066]

其中,xk表示输入角度θ的位数k对应向量的横坐标,yk表示输入角度θ的位数k对应向量的纵坐标。

[0067]

本实施例中,步骤s2中由于输入角度θ限制在[0,π/8)范围内,根据对应角度小数部分较高的7位数值,第一查找表的二进制地址范围为0000000

–

1100100;

[0068]

第二查找表的计算结果由7个子矩阵相乘得到,在每个子矩阵中,主对角线元素相等,次对角线元素相反;由数学推导表明,乘法得到的最终矩阵也满足上述规律;进一步的计算表明,如果第二查找表的7位二进制地址b

11b12b13b14b15b16b17

的查找结果为则逐位采用地址字节的相反符号将导致查找结果为要构造第二查找表,只需在二进制地址范围0000000

–

0111111内进行计算,而矩阵的另一半可以按照第一公式推导,从而节省查找表的一半寄存器消耗,大大减少了电路面积;

[0069]

步骤s2具体为:

[0070]

s21:将所述θ[33:20]划分为θ[33:27]和θ[26:20],获得所述θ[26:20]对应的r3至r9的值,以及所述θ[33:27]对应的r

10

至r

16

的值;

[0071]

s22:将所述初始向量w(x3,y3)以及r3至r9输入所述第一公式进行迭代计算,构建第一查找表,所述第一查找表表示为

[0072]

s23:将(x

10

,y

10

)以及r

10

至r

16

输入所述第一公式进行迭代计算,构建第二查找表,所述第二查找表表示为

[0073]

s24:所述第一查找表和所述第二查找表组合获得所述查找表,所述查找表表示为

[0074]

s25:获取所述查找表中的所述向量a(x

17

,y

17

)。

[0075]

本实施例中,步骤s3具体为:

[0076]

s31:获取所述θ[19:0]对应的r

17

至r

36

的值;

[0077]

s32:将所述向量a(x

17

,y

17

)以及r

17

至r

36

输入所述第二公式进行迭代计算,获得x

37

和y

37

的值,所述第二公式的表达式如下:

[0078][0079]

其中,m的值为17,s的值为20。

[0080]

参考图2,传统的相位累加器的输出频率和频率控制字由以下参数控制:f

out

=f

tw

/2n·fclk

;显然,输出信号频率的分辨率是参考频率的1/2n;换句话说,输出信号频率具有最小的频率分辨率,使得不可能以任何精确频率输出;例如,传统的相位累加器无法在内输出信号频率,因为频率控制字只能是整数。

[0081]

参考图3,针对这一问题,本发明提供一种基于低延迟的精确频率输出系统,增加一个辅助相位累加器,其输入值可根据需要的输出频率进行设置,以实现精确的频率输出,从而解决了传统相位累加器固有的最小频率分辨率问题,用于实现上述的基于低延迟的精确频率输出方法,包括:辅助相位累加器、主相位累加器、输入模块、输出模块和时钟模块;

[0082]

所述输入模块与所述辅助相位累加器电性连接,所述辅助相位累加器与所述主相位累加器电性连接,所述主相位累加器与所述输出模块电性连接,所述时钟模块与所述辅助相位累加器和所述主相位累加器电性连接。

[0083]

本实施例中:

[0084]

所述输入模块包括输入信号a和输入信号b;

[0085]

所述输出模块的输出值f

out

=(f

tw

+a/b)/2n·fclk

,n为相位累加器位数,其中f

clk

为

所述时钟模块提供的时钟,f

tw

为频率控制字,所述频率控制字为十进制,其值由所述输入信号a的值和所述输入信号b的值决定,从而可以实现用户所期望的精确频率的输出。

[0086]

需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者系统不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者系统所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者系统中还存在另外的相同要素。

[0087]

上述本发明实施例序号仅仅为了描述,不代表实施例的优劣。在列举了若干装置的单元权利要求中,这些装置中的若干个可以是通过同一个硬件项来具体体现。词语第一、第二、以及第三等的使用不表示任何顺序,可将这些词语解释为标识。

[0088]

以上仅为本发明的优选实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1